简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

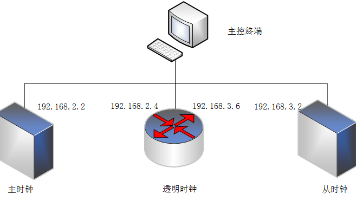

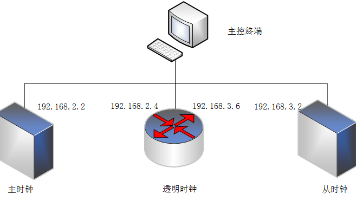

嵌入式Linux实战项目全开源-华为嵌入式开发大赛初赛获奖作品-基于LS1046A的时间同步系统设计与可视化监控平台开发。高精度时间同步技术是分布式嵌入式系统中保障事件一致性和时序协同的关键。本项目围绕IEEE 1588标准构建同步网络,在嵌入式平台上完成了从系统搭建到时钟节点部署的全流程实现,支持主从与透明时钟结构下的多种同步拓扑。进一步,设计了一种集设备管理、网络配置与同步监控于一体的图形化交

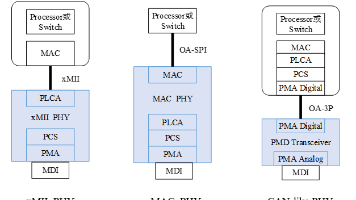

单对线以太网(SPE)芯片全景调研:从标准到选型的深度解析。 单对线以太网(SPE)正在工业物联网、车载电子等领域掀起一场 “布线革命”。对于想实际测试的初学者,理解其核心标准与芯片技术是入门的关键。本文将从单对线以太网标准体系入手,解析芯片接口分类逻辑,最终聚焦市面上主流的 10BASE-T1/100BASE-T1/1000BASE-T1 芯片,为你的技术选型提供参考。

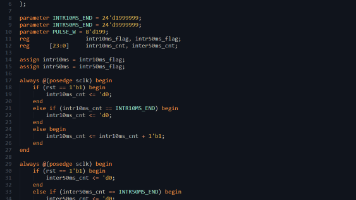

Sublime配置verilog开发环境-具备语法高亮、代码补全、自定义代码段及语法检查等功能,提升FPGA开发效率!对于在学习FPGA开发之前使用过其他集成开发工具如VS、pycharm、keil或编辑工具如Sublime、VScode、Notepad的朋友,在使用Vivado时可能感觉自带编辑器用起来不太舒服,比如不支持语法高亮显示,不支持代码自动补全等功能。因次,使用第三方编辑器来编写Ver

嵌入式Linux实战项目全开源-华为嵌入式开发大赛初赛获奖作品-基于LS1046A的时间同步系统设计与可视化监控平台开发。高精度时间同步技术是分布式嵌入式系统中保障事件一致性和时序协同的关键。本项目围绕IEEE 1588标准构建同步网络,在嵌入式平台上完成了从系统搭建到时钟节点部署的全流程实现,支持主从与透明时钟结构下的多种同步拓扑。进一步,设计了一种集设备管理、网络配置与同步监控于一体的图形化交