简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

Verilog提供了丰富的文件操作系统任务,主要包括文件打开/关闭、读写操作、字符串处理、定位和存储器加载等功能。文件打开使用$fopen指定读写模式,关闭用$fclose。写入任务如$fdisplay和$fwrite支持格式化输出到文件,而$swrite和$sformat用于字符串处理。读取操作包括字符级($fgetc)、行级($fgets)和格式化读取($fscanf)。文件定位通过$fsee

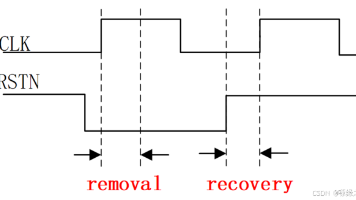

时序检查任务就是数字世界的交通规则摄像头$setup和$hold拍下同步信号是否遵守“绿灯前停车、绿灯后慢行”。$recovery和$removal拍下异步复位信号是否在正确时间“松手”。$width和$period拍下时钟是否“呼吸均匀”。你作为验证工程师,不需要自己写这些摄像头(除非你在建行为模型),但你要学会读懂监控照片(violation 报告),分析是哪个路口(路径)出了问题,然后告诉设

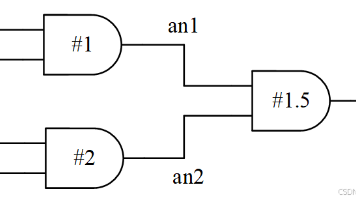

Verilog延迟模型是芯片设计中实现时序仿真的关键技术,主要包括三种模型:分布延迟(每个元件单独指定延迟)、集总延迟(累计延迟集中到末级)和路径延迟(精确描述引脚间延迟)。路径延迟因精度高、与标准单元库兼容成为主流方法,通常通过specify块实现。实际工作中,验证工程师需结合STA和时序仿真,重点关注标准库提供的路径延迟模型,并通过SDF反标进行门级仿真。理解这些模型对调试时序违例至关重要,推

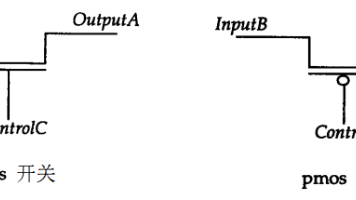

你要关注什么为什么怎么练习端口顺序(输出第一)顺序错了仿真会出奇怪错误手写几个nmospmos实例,放在 testbench 里跑,故意写反看看报错使能极性(低有效/高有效)与真实芯片规格一致,否则方向控制反了用bufif0和bufif1做 PAD 模型,改变 OEN 看波形高阻z与竞争多个驱动同时连到同一线网会导致x或短路仿真两个tranif1使能信号同时为 1 时的行为上拉/下拉电阻pullu

本文介绍了UPF(统一功耗格式)中的电源域(Power Domain)概念及其应用。电源域是一组共享相同电源管理特性的设计元素,可以独立控制电压、开关状态等。文章详细讲解了电源域的创建方法、层次化结构、边界定义和元素归属规则,并通过实际SoC示例说明如何划分多级电源域以实现精细功耗管理。重点包括:必须创建主电源域作为基准,使用create_power_domain命令定义域范围,以及层次化域结构对

开源 EDA 工具调试指南摘要 本文总结了四大开源 EDA 工具(Icarus Verilog、Verilator、Yosys、OpenSTA)的常见错误及解决方法: Icarus Verilog:信号未声明错误需显式声明;SystemVerilog语法需指定标准;时间尺度不一致需统一声明。 Verilator:不支持仿真专用语法,需重写为可综合代码;组合逻辑环路需用寄存器打破。 Yosys:存储

Skywater 130nm PDK 资源指南摘要 Skywater 130nm PDK 是首个商业晶圆厂开源的设计工具包,让开发者无需NDA或高昂授权费即可设计可制造芯片。该资源包含工艺规则、标准单元库、器件模型等完整工具链,并支持通过Google Open MPW项目免费流片。 核心资源包括: GitHub主仓库提供标准单元库、文档和脚本 官方文档站详细说明安装配置和设计规则 Liberty时

开源工具是绝佳的学习平台:让你看清每一步,理解核心原理。商业工具是工业生产的利器:提供容量、优化质量、高级功能和专业支持。概念映射关键差异:物理感知、OCV、SSTA、多角多模、更丰富的约束支持。过渡方法:掌握核心概念 → 申请试用 → 对比实验 → 学习流程生态。无论你将来使用哪种工具,时序分析和综合优化的基本思想永远不会变。你已经在正确的道路上。现在,勇敢地跨出一步,去尝试商业工具吧——你会发

**时钟域交叉(CDC)是芯片设计中极易出错的关键问题,当不同时钟域的信号交互时,可能因亚稳态导致数据错误。亚稳态发生在触发器采样时数据变化违反建立/保持时间要求,导致输出不确定。解决方法包括:1)两级触发器同步器,通过两级采样降低亚稳态概率;2)多比特传输技术,如格雷码(适合计数器)和握手协议(适合任意数据);3)异步FIFO(高吞吐量场景)。设计时必须遵循同步器使用法则,如保护同步器不被优化、

**时钟域交叉(CDC)是芯片设计中极易出错的关键问题,当不同时钟域的信号交互时,可能因亚稳态导致数据错误。亚稳态发生在触发器采样时数据变化违反建立/保持时间要求,导致输出不确定。解决方法包括:1)两级触发器同步器,通过两级采样降低亚稳态概率;2)多比特传输技术,如格雷码(适合计数器)和握手协议(适合任意数据);3)异步FIFO(高吞吐量场景)。设计时必须遵循同步器使用法则,如保护同步器不被优化、