简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

APCVD(常压化学气相沉积)是一种在常压下进行的气相沉积技术,无需真空设备。该技术主要用于微电子器件中沉积绝缘层(如SiO2)和导体层(如多晶硅),也可用于传感器制造。APCVD具有高沉积率、设备简单等优点,但存在非均匀性较差、表面粗糙度高、温度限制和污染风险等缺点。典型工艺包括使用硅烷和氧气反应沉积SiO2,通过添加不同气体可获得PSG或BPSG等特殊材料。该技术广泛应用于电子元件隔离和晶体管

芯片制造过程中,微小颗粒(0.1-100微米)会引发开路或短路等严重问题。人体是主要污染源(占75-80%),每分钟可释放数万颗粒。超净间需严格管控人员着装和活动,以减少皮肤细胞、毛发等污染物对纳米级芯片制程的影响,确保产品良率。

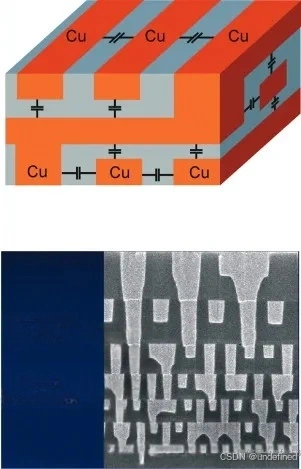

芯片互连中介质k值降低主要是为了减小RC延迟。随着CMOS技术进入45nm以下节点,互连寄生电容成为性能瓶颈。电容公式C=ε*A/d表明,降低介电常数(k值)能有效减小电容。因此工艺节点越先进,k值从2.7逐步降至2.1以下。常见低k介质包括有机聚合物、多孔硅基材料等,通过降低介电常数来提升芯片性能。

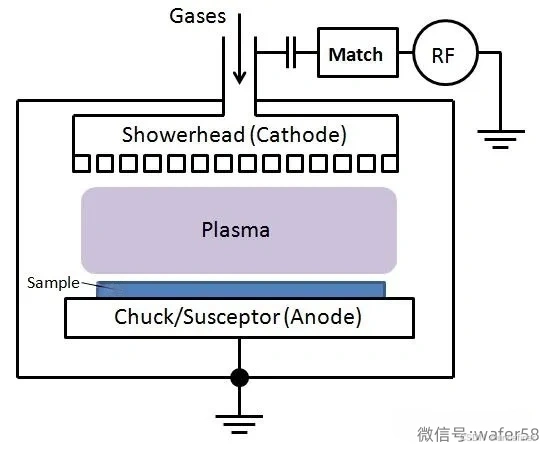

化学气相沉积(CVD)是制造半导体薄膜的重要技术,主要有PECVD、LPCVD、APCVD、MOCVD和ALD等类型。PECVD利用等离子体在低温下沉积薄膜;LPCVD在低压高温环境中提高膜均匀性;APCVD操作简单但精度较低;MOCVD专用于III-V族半导体;ALD通过自限反应实现原子级精度。不同CVD技术适用于不同材料和工艺需求。

本文详细解析了半导体制造中的静电吸盘(ESC)技术。ESC通过静电力固定晶圆,避免了传统机械夹持的损伤风险。文章介绍了ESC的三种吸附原理:库仑力、约翰逊-拉贝克力和电场梯度力,这些力共同作用产生吸附效果。同时阐述了ESC的主要结构组成,包括吸附盘、电极、加热器和底板等核心部件。静电吸盘技术广泛应用于PVD、CVD和刻蚀等半导体工艺中,了解其原理和结构有助于优化相关制造工艺。

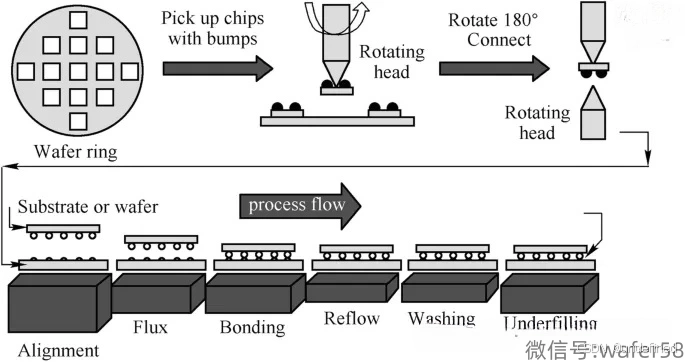

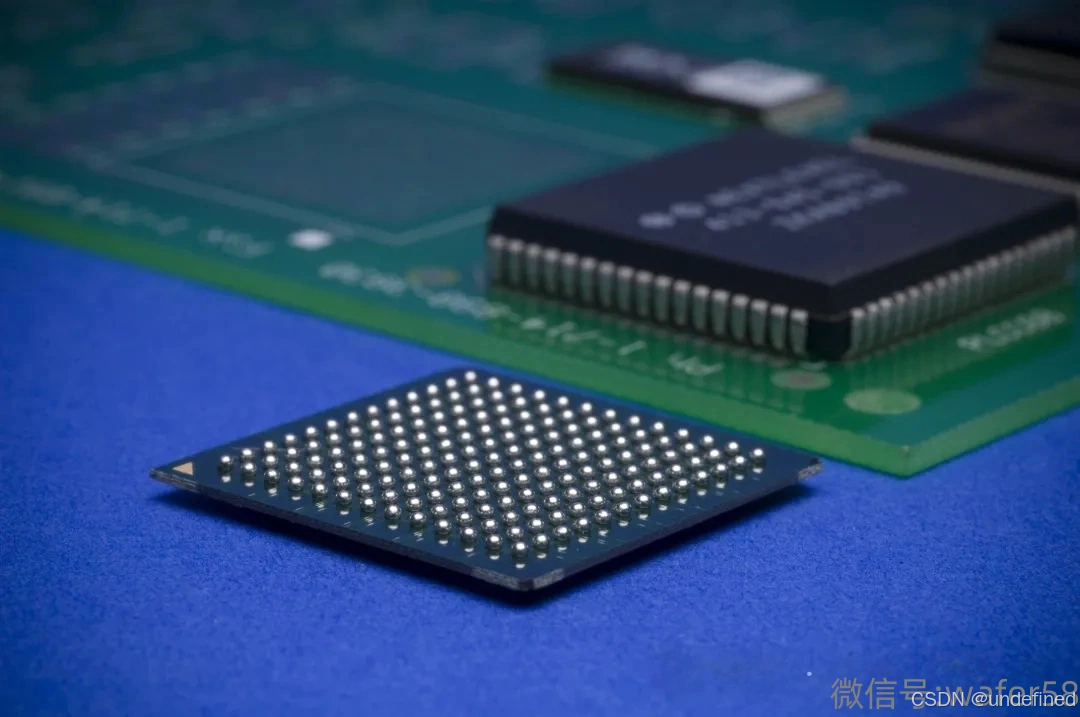

本文介绍了倒装芯片封装的关键工艺流程。首先通过顶针和吸嘴将带凸点的芯片从蓝膜上拾取并转向对准基板焊盘。接着通过助焊剂辅助焊接,采用压力、温度和超声波使锡球初步固定,再经回流焊实现牢固连接。随后进行助焊剂清洗、底部填充环氧树脂缓冲应力,最后经过固化、塑封和检测完成封装。整个流程重点突出了芯片对位精度、焊接工艺和应力缓冲等关键技术环节。

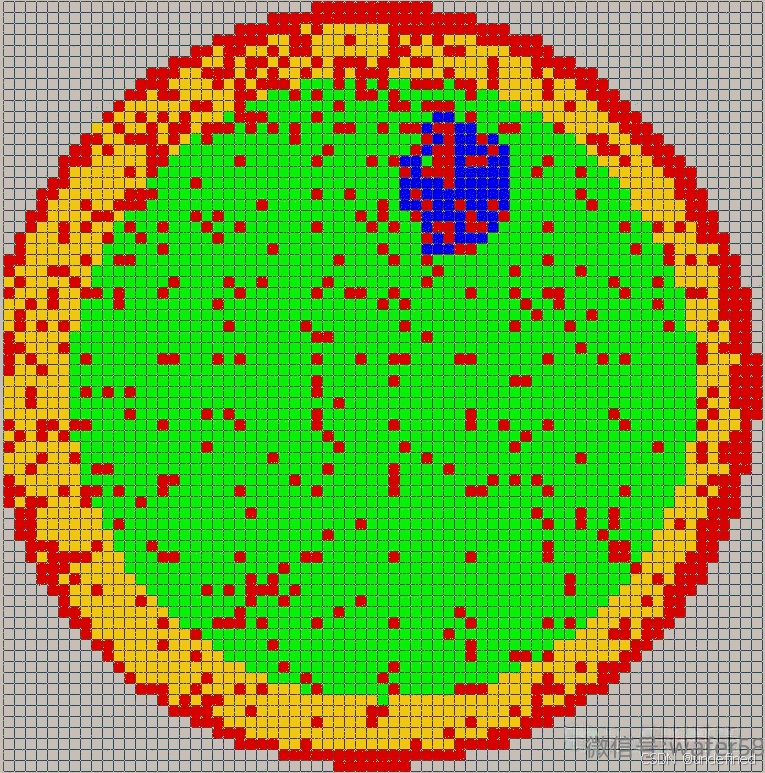

华为Mate60搭载的麒麟9000S芯片引发业界对国产芯片良率问题的关注。芯片良率指合格芯片与总产量的比例,直接影响利润和成本。以10万粒芯片的晶圆为例,良率50%和80%意味着合格芯片相差3万粒,导致生产成本和利润差异显著。芯片制造涉及上千道工序,每道工序良率的小幅波动都会导致最终良率大幅下降。即便相同设备、团队和工艺,不同工厂的良率也可能天差地别,说明芯片制造是动态过程,需要持续优化调整。目前

倒装芯片中的锡球主要通过丝网印刷、激光植球和电镀三种工艺制作,具有导电、散热和支撑三大功能。丝网印刷成本低但均匀性较差;电镀法可制作小锡球且均匀性好;激光植球精度高但设备昂贵。不同工艺适用于不同生产需求,共同确保芯片性能稳定。

芯片制程中的金属材料主要承担导电、导热和保护三大功能。常见金属材料包括铜(互连导线)、铝(早期互连材料)、钨(接触填充)、钛/氮化钛(隔离层/粘附层)、钴(硅化物)、金(电极/电镀)等。不同金属因其导电性、导热性、抗腐蚀性等特性,在芯片制造中各司其职,如铜用于高效互连,钨用于填充接触孔,钛氮化物用于防止金属扩散。这些金属材料共同确保芯片的正常运行和长期可靠性。

ICP-RIE是一种结合电感耦合等离子体与反应离子刻蚀的先进技术,具有高刻蚀速率、高选择性和低损伤的特点。其原理是通过射频电源在导体线圈中产生电磁场,激发气体形成高密度等离子体,实现物理和化学刻蚀的结合。线圈设计和偏压控制是影响刻蚀效果的关键因素,双射频源设计可实现离子密度与能量的独立调控。该技术广泛应用于半导体、电介质、金属和聚合物等材料的刻蚀加工,根据不同材料选用氟基或氯基工艺气体。