简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

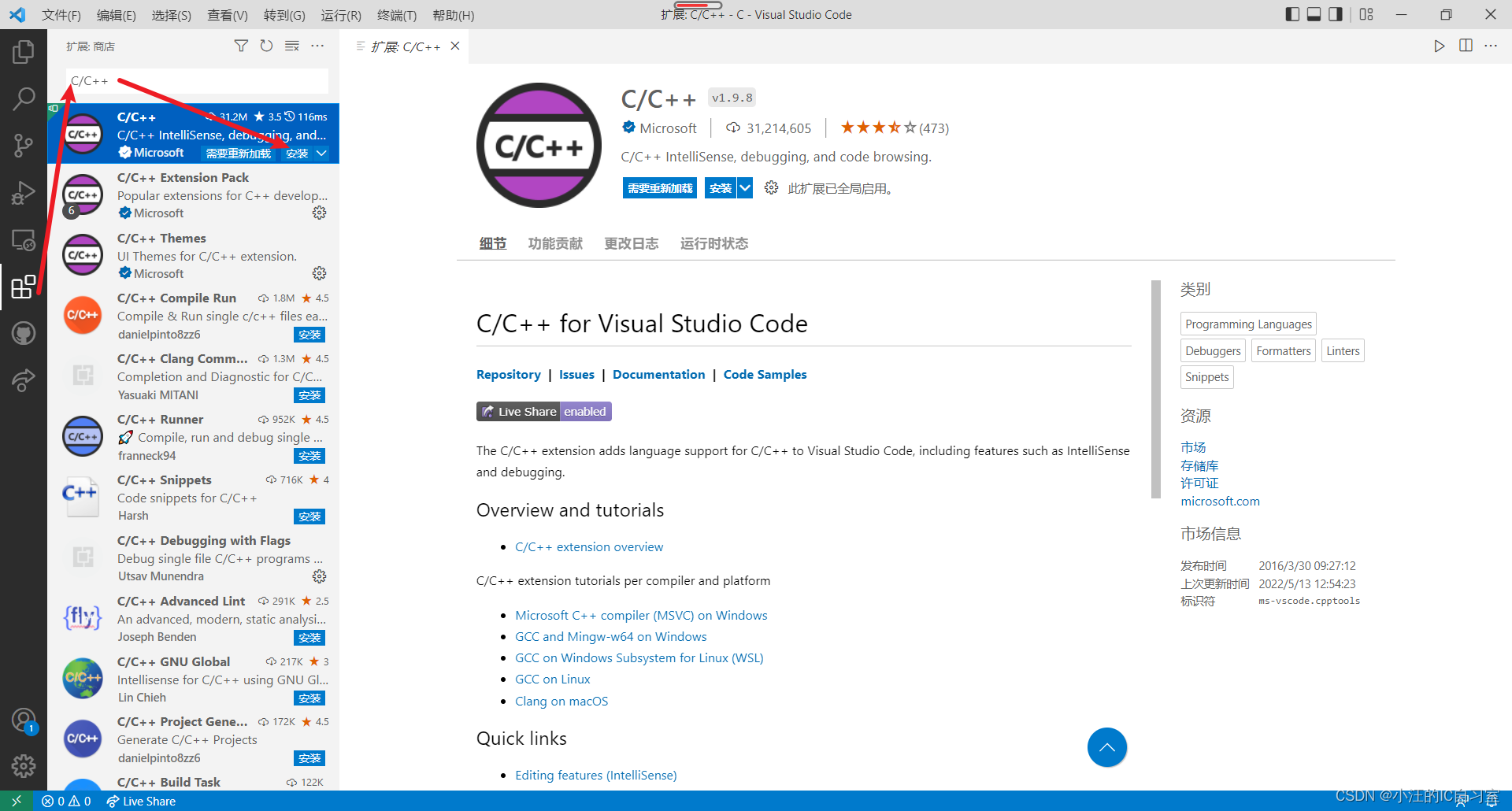

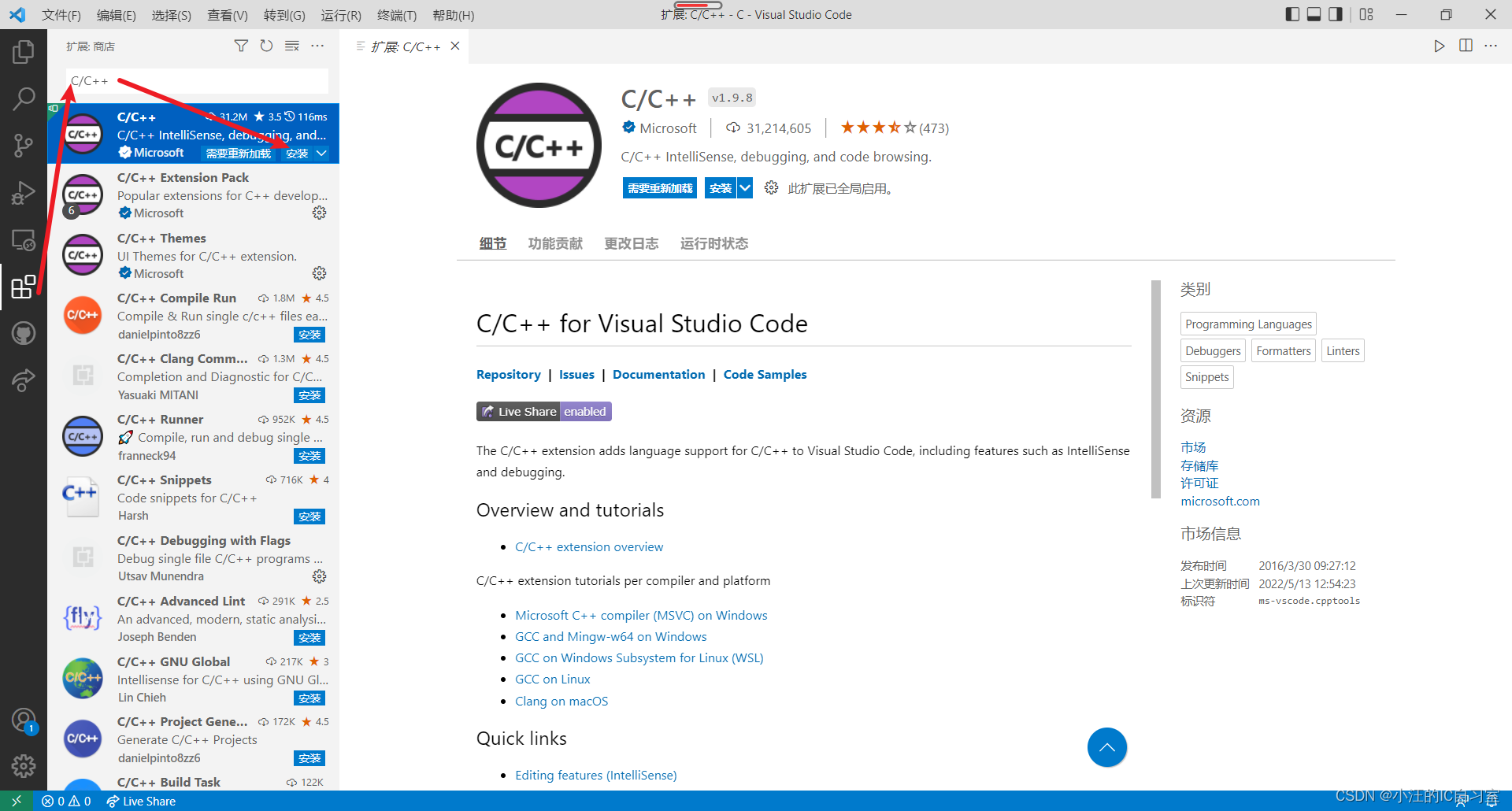

目录1 下载vscode(若提前下载好,直接跳转到3 配置C/C++环境:)2 配置为中文界面3 配置C/C++环境:3.1 准备3.2 配置环境变量3.2.1 首先安装MinGW编译器:3.2.2 然后配置环境变量:3.3配置编译器:3.3.1vscode安装C/C++扩展3.3.2 配置编译器1 下载vscode(若提前下载好,直接跳转到3 配置C/C++环境:)去vscode官

目录1 下载vscode(若提前下载好,直接跳转到3 配置C/C++环境:)2 配置为中文界面3 配置C/C++环境:3.1 准备3.2 配置环境变量3.2.1 首先安装MinGW编译器:3.2.2 然后配置环境变量:3.3配置编译器:3.3.1vscode安装C/C++扩展3.3.2 配置编译器1 下载vscode(若提前下载好,直接跳转到3 配置C/C++环境:)去vscode官

目录I、ASIC设计流程一、确定项目需求二、前端流程三、后端流程II、IC设计流程相关名词梳理(含各流程EDA工具梳理)III、IC设计流程整理(图片)I、ASIC设计流程一、确定项目需求1. 确定芯片的具体指标:物理实现制作工艺(代工厂及工艺尺寸);裸片面积(DIE大小,DIE由功耗、成本、数字/模拟面积共同影响);封装(封装越大,散热越好,成本越高)。性能指标:速度(时钟频率);...

Q1. 定宽数组、动态数组、关联数组、队列各自特点和使用定宽数组:属于静态数组,编译时便已经确定大小。其可以分为压缩定宽数组和非压缩定宽数组:压缩数组是定义在类型后面,名字前面;非压缩数组定义在名字后面。Bit [7:0][3:0] name; bit[7:0] name [3:0];动态数组:其内存空间在运行时才能够确定,使用前需要用new[]进行空间分配。关联数组:其主要针对需要超大空间但又不

Verilog实现1位全加器及输出逻辑解析1、半加器、全加器是什么 半加器电路指对两个输入数据位(a、b)相加,输出一个结果位(sum)和进位(cout),但没有计算进位输入的加法器电路。 相比半加器,全加器是将进位输入也代入计算的加法电路,同样输出一个结果位和进位。1位全加器就是计算带进位输入的1位二进制数的加法电路,多个一位全加器进行级联可以得到多位全加器。2、1位全加器的Verilog实