简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

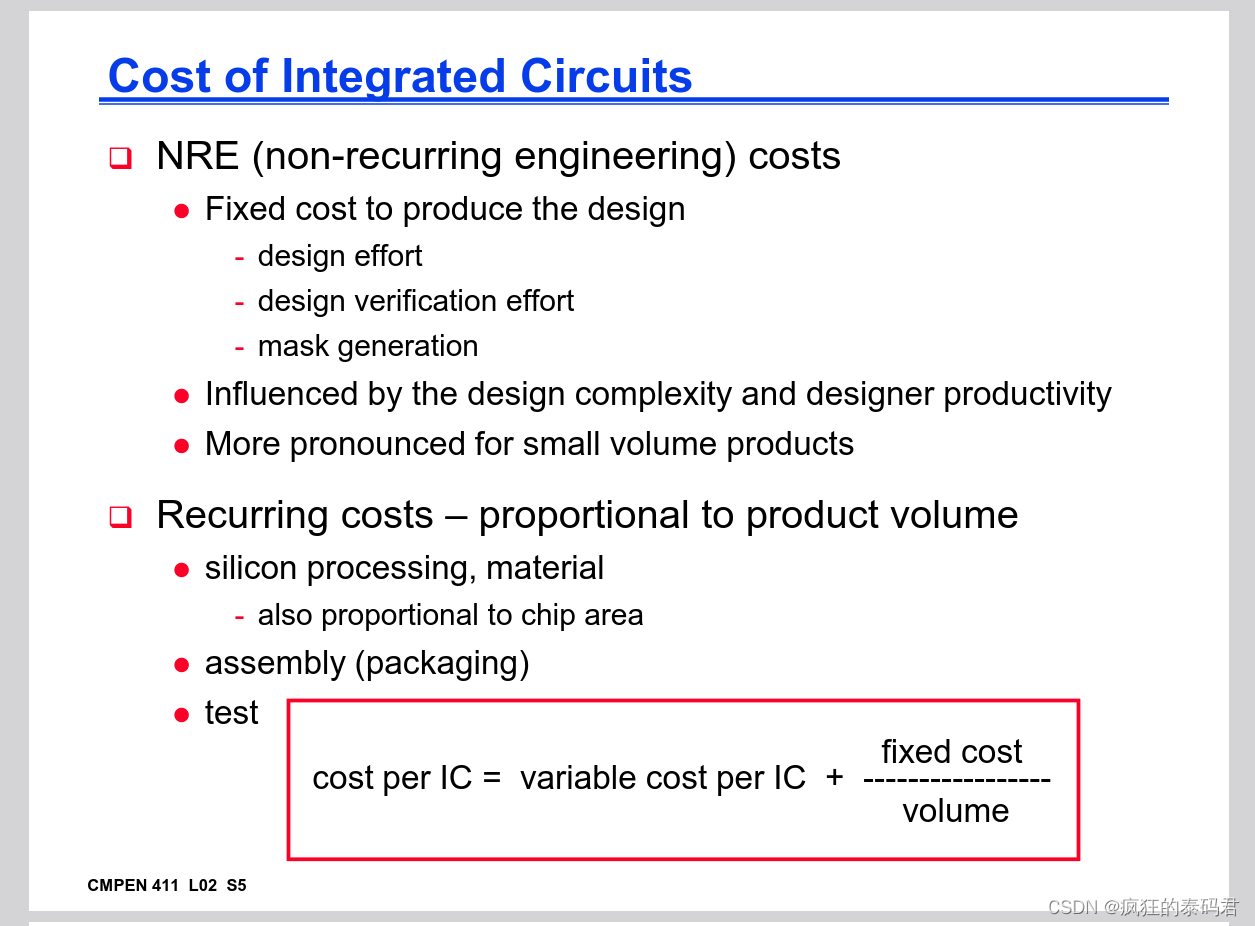

集成电路/芯片可循环成本(RE)和非可循环成本(NRE)

集成电路的可循环成本和非可循环成本

Verilog中双向端口(inout) 的原理和使用方法

在用Verilog描述的过程中,只考虑CPU的数据通路结构时,就容易忽略它的双向端口的具体实现,并非如图中一般,简简单单的与RAM模块的inout端口相连。分析inout的端口特性,对于一个模块来说,inout端口既可以当做输入,又可以当做输出,那么,与inout端口相连的另一模块是什么情形呢?当WriteRAM有效时,CPU向RAM写入数据,这时CPU的三态门导通,CPU的inout端口作为输出

codeforces1453C

大神代码以及思路总体思路就是保存每个数字的最小坐标和最大坐标,然后分类讨论,题意就不写了。大概意思就是怎末只改一个数字,让该0~9的围成的三角形面积最大。个人觉得不配1700,虽然我没想出来,但是我菜呀。。自己的代码#include <iostream>#include <algorithm>#include <vector>using namespace st

到底了