简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

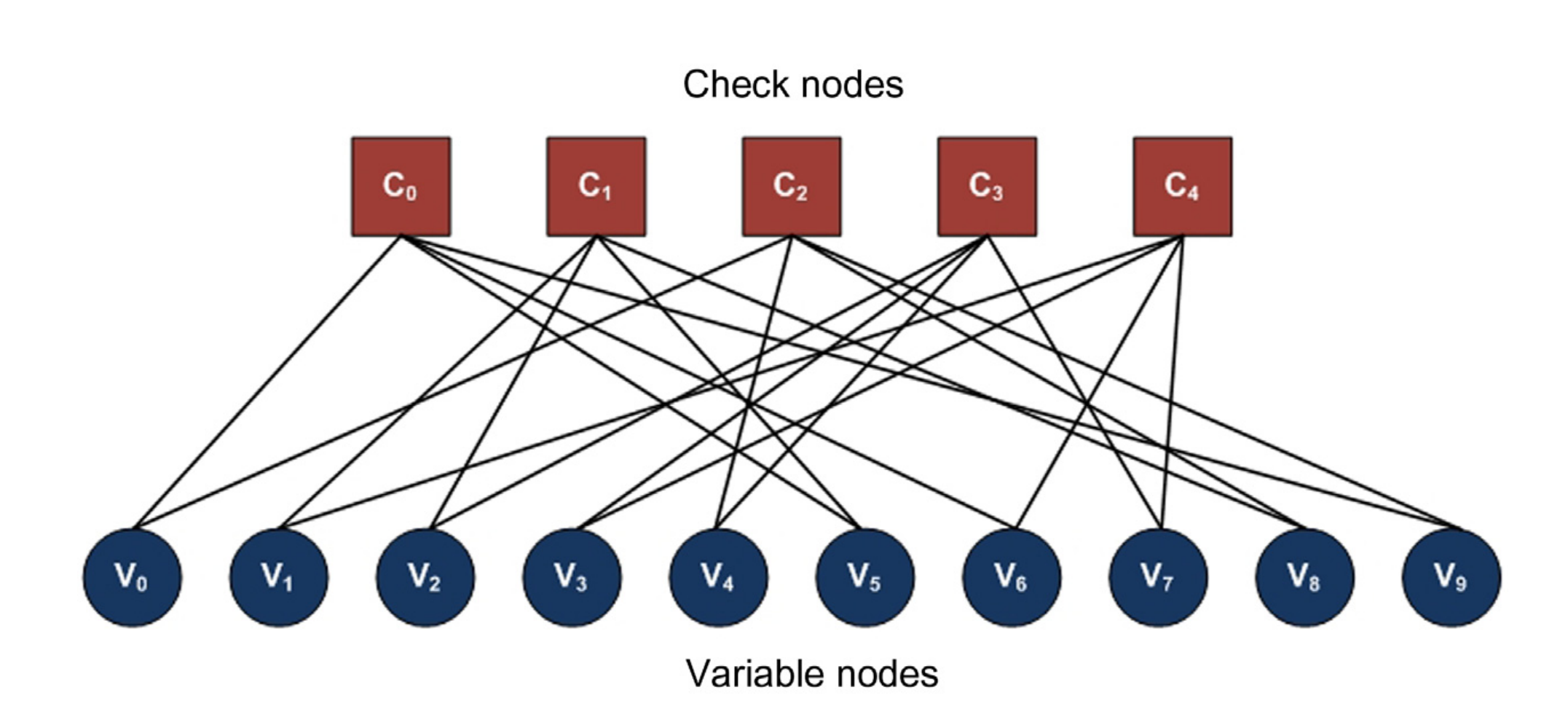

LDPC译码原理(公式推导)及其matlab代码实现(超详细)

低密度奇偶校验码(Low-Density Parity-Check Codes)凭借其逼近Shannon限的纠错性能,受到了信道编译码学者的广泛关注,已成为DVB-S2、IEEE802.16e、CCSDS、5G等无线通信标准首选的信道编码方案。2001年,S.Chung等人的研究结果表明,码率1/2、码长10^7的非规则LDPC码在AWGN信道下采用置信传播算法进行迭代译码,当错误概率为10 ^-

到底了