简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

(一)深度学习技术存在的问题:面向任务单一依赖于大规模有标签数据几乎是个黑箱模型,可解释性不强(二)深度学习框架

在当今EDA(电子设计自动化)工具高度发展的背景下,手动摆放单元格并绘制连线已经变得不切实际。因此,利用自动化工具进行芯片设计已成为必要。芯片后端已渐渐被APR这一称呼代替了,因为没有办法绕开EDA tool去手动PR,都是auto PR了。APR的过程主要包括四个步骤:布局规划(Floorplan)、单元摆放(Placement)、时钟树综合(CTS,Clock Tree Synthesis)和

小波分析的重要应用之一就是用于信号消噪,首先简要地说明一下小波变换实现信号消噪的基本原理。一、基本原理含噪的一维信号模型可以表示如下s(k)=f(k)+Ee(k)k=0,1,..,n-1式中s(k)为含噪信号,f(k)为有用信号,e(k)为噪声信号。这是假设e(k)是 一个高斯白噪声,通常表现为高频信号,而工程实际中f(k)通常为低频信号或者 是一些比较平稳的信号。因此我们可按如下方法进行消噪处理

MPW主要用于早期的设计验证和成本控制,而NTO则是设计定型后的首次全掩膜验证性流片,介于工艺调优和大规模生产之间的重要步骤。通过这两步,可以有效地从设计验证过渡到大规模生产。

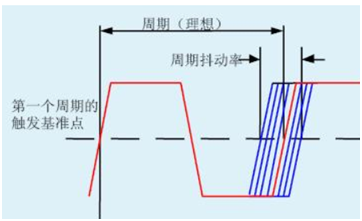

时序分析基础(Slack、Setup、Hold、Jitter、Skew、亚稳态)一、常见名词1.1 时钟偏移Skew1.1.1Skew出现的原因因时钟线长度不同或负载不同,导致时钟到达相邻单元的时间不同,这个时间上的偏差就叫时钟偏移SKEW。 在上图中的Tskew=Tclk2-Tclk11.1.2 Skew解决方法偏移会一直存在Skew 问题的解决方法就是:设计中的主要信号应该走全局时钟网络..

一、"天天向上的力量"问题分析基本问题:持续的价值二、"天天向上的力量"第一问问题1: 1‰的力量#DayDayUpQ1.pydayup = pow(1.001,365)daydown = pow(0.999,365)print("向上:{:.2f},向下:{:.2f}".format(dayup,daydown))运行结果:1‰的力量,接近2倍,不可小觑哦...

请思考如何用 case 语句写出比较电路:推出一个 2 位较大数判断电路的真值表用 case 语句编写判断电路1、给出程序2、给出仿真程序3、给出 RTL 图4、给出仿真结果1、真值表输入输出A1B1A0B0gt:A>B...

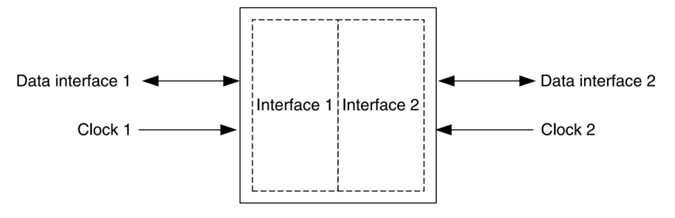

一、什么是跨时钟域?影响是什么?1、时钟域假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域。假如设计有两个输入时钟,如图所示,一个时钟给接口1使用,另一给接口2使用,那么我们说这个设计中有两个时钟域。2、单时钟域(同步时钟域)单时钟设计 (更确切地说,也就是同步设计) 如下图所示。在单时钟域中,有单个时钟贯穿整个设计。同多时钟设计相比,这样的设计

1、光电效应实验现象2、经典理论解释光电效应遇到的困难3、爱因斯坦的光量子论来解释光电效应4、光电效应的应用5、康普顿散射6、经典理论解释康普顿散射遇到的困难7、光量子理论解释8、光的本质认识9、自发辐射10、受激辐射11、受激吸收12、三个爱因斯坦系数之间的关系...

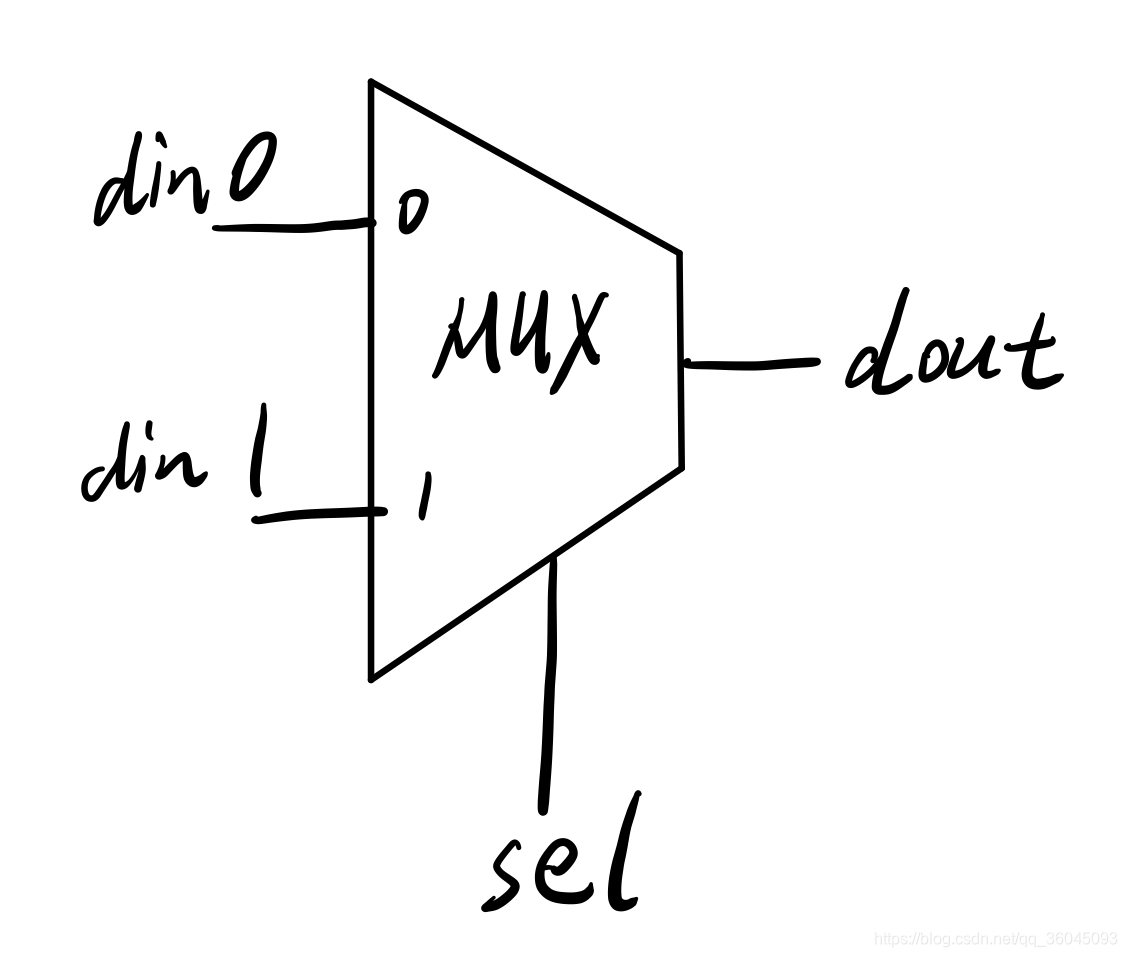

目录1、二选一MUX的真值表2、逻辑框图与逻辑表达式3、组成结构二、Glitch free 无毛刺的MUX1、利用MUX实现时钟切换毛刺出现原因:2、时钟无缝切换方法3、不相关时钟的无缝切换1、二选一MUX的真值表输入为din0、din1,控制为sel,输出为doutseldout0din01din12、逻辑框图与逻辑表达式逻辑表达式:3、组成结构使用与门、或门、反相器来构造二选一M...