简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

PCI和PCIe架构1。PCI架构一个典型的桌面系统PCI架构如下图:如图,桌面系统一般只有一个Host Bridge用于隔离处理器系统的存储器域与PCI总线域,并完成处理器与PCI设备间的数据交换。每个Host Bridge单独管理独立的总线空间,包括PCI Bus, PCI I/O, PCI Memory, and PCIPrefetchable Memory Space。桌面系统也一般只有一

本文就PCIe PHY测试的相关内容进行简要介绍,如有读者发现问题或错误,请慷慨指出,后期也会持续修正优化,谢谢!PCIe需要进行的测试:PHY TestConfiguration Space TestLink Layer TestTransaction Layer TestRetimer TestPCIe Architecture PHY test测试是针对底层电气特性的测试,主要关注PCIe信

scan DFF 是在原DFF 的输入端增加了一个 MUX,于是多了几个 pin :scan_in,scan_enable,scan_out。简单来讲,scan chain 工作时分为三个步骤: load ····> capture ····> unload。3. 在 SE 有效拉高时,将 input pattern 串行打入scan register。unload 是将scan chain 中的

scan DFF 是在原DFF 的输入端增加了一个 MUX,于是多了几个 pin :scan_in,scan_enable,scan_out。简单来讲,scan chain 工作时分为三个步骤: load ····> capture ····> unload。3. 在 SE 有效拉高时,将 input pattern 串行打入scan register。unload 是将scan chain 中的

#UVM# 简书 uvm_event 源码分析

源同步(source synchronous)系统同步(system synchronous)源同步,是由发送端在发送数据的同时发送一个选通信号。接收端将这个选通信号作为接收时钟。控制信号的接收。理论上不受频率的限制,极大的提高的数据传输的速度。系统同步,发送端和接收端都是由系统时钟驱动的。数据传输速度受限。(现在应用较少了。)针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,

相信大家时不时的都会听到传输线(Transmission Line,TL)的概念,在信号完整性分析中占据重要地位。这一期我们就浅显的学习下其基本概念和特性。电路系统是器件(Device)和连线(Interconnect)的整体。在电路图中经常使用的是理想连线。在集成电路中的制造中,连线的实现可能会用到多晶硅,铝线或者铜线。封装过程中的bonding wire可能会用到铝线或者金线。板级pcb走线通

我们先看Switching Power,开关功耗是指在逻辑门开关时所引起的功耗,在CMOS逻辑门输出节点产生逻辑转换时,电源对输出节点电容充放电所产生的功耗。电源在一个充放电的周期中提供的能量一半都将以热的形式被消耗,由此可见动态功耗的主要是逻辑门的输出电容引起的。Internal Power 主要包括内部短路电流对应的损耗(Short circuit)和内部节点充放电产生的功耗(Internal

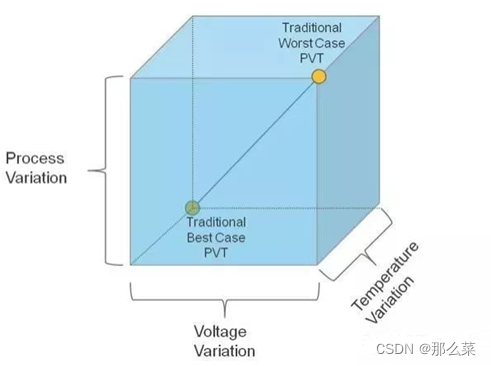

1.工艺角 process corner不同的晶片和不同的批次之间,因为掺杂、刻蚀、温度等外界因素导致MOSFET参数的变化范围比较大。为减轻设计困难度,需要将器件性能限制在某个范围内,并报废超出这个范围的芯片,来严格控制预期的参数变化。工艺角即为这个性能范围。1.2 5 个 Corner modelTT:nmos -Typical corner & pmos -Typical corne

PPM: part per milinon : 百万分之几数字电路中表示频率误差的ppm是什么意思?1 ppm指的是每隔1million clock会产生一个clock的偏移。例如:时钟偏移+100ppm,则时钟周期为T*10^6/(10^6 + 100)时钟偏移-100ppm,则时钟周期为T*10^6/(10^6 - 100)举例子:假设有一个50HZ的时钟,总有5ppm的频率误差,那么当它用于