简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

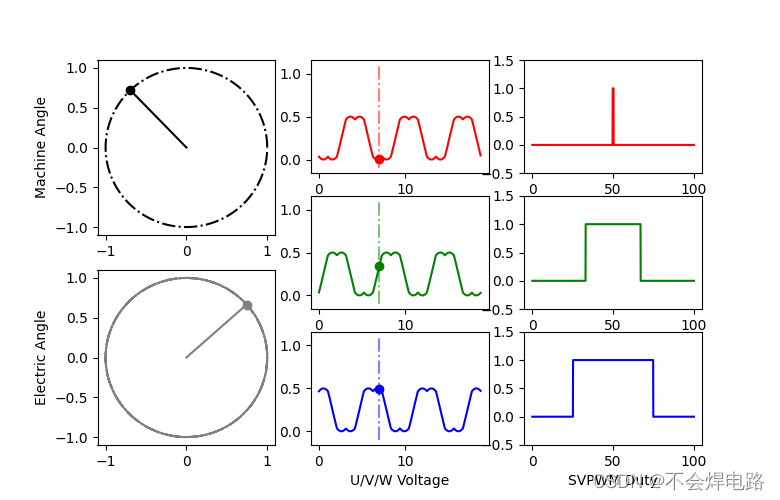

SVPWM波形仿真

以下全部图片均来自镁光(Micron)公司产品的数据手册。DDR:以MT48LCxx型号的DDR内存芯片为例,数据手册中给出如图1所示的一个表格。从表格中可以看出它的主频(Clock Frequency)。图1 不同速度等级的DDR主频它的主频与传输数据的频率相同。我们可以从时序图中观察出来。随便在数据手册中截过来一个有数据传输的时序图,如图2所示。图2 输出数据Dout与...

写在前边的话:如果你能搜到此篇文章,我就默认你对AXI4-Stream有了一个大致的了解(至少知道此协议不包含任何地址映射,仅仅是一串数据流)。本文是基于video in IP的对视频信号转AXI4-Stream信号的验证。因为博主现在不用OV5640/OV7725等之类的传感器了,因此抄无可抄,必须自己探究一下这个IP的输入时序是怎样的。只有理解了输入和输出的时序是怎样的,我们才能应用这个IP得

一、 GIC头文件中的那些函数xscugic.h文件中定义了以下多个函数。//连接:设置中断服务函数注册//入口参数:SCU GIC实例,中断ID,定义中断处理函数,中断s32 XScuGic_Connect (XScuGic *InstancePtr, u32 Int_Id, Xil_InterruptHandler Handler, void *CallBackRef);//断开连接:中断服务

在ZYNQ上调试OV5640并用HDMI显示出来这个实验简直就是一部血泪史啊!!有木有!!一个小小的摄像头,调了4天。因此我准备把这次痛苦的经历和全部经验、细节写出来,以供记录学习ZYNQ的心酸历程。在百度上输入ZYNQ VDMA OV5640等关键字,搜索的大部分是来自米联客的教程。在此特别地向米联客、ALINX、正点原子等等诸如此类的公司和机构表示感谢和深深的敬意,原因是他们向广大刚刚走进ZY

以下全部图片均来自镁光(Micron)公司产品的数据手册。DDR:以MT48LCxx型号的DDR内存芯片为例,数据手册中给出如图1所示的一个表格。从表格中可以看出它的主频(Clock Frequency)。图1 不同速度等级的DDR主频它的主频与传输数据的频率相同。我们可以从时序图中观察出来。随便在数据手册中截过来一个有数据传输的时序图,如图2所示。图2 输出数据Dout与...