简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

注:例程位置:2_Demo\09_pcie_test\ipcore\pcie_test\pnr\example_design 将程序固化到 flash 内,把开发板插入电脑 PCIE 卡槽,连接电源,将电源开关打开,电 脑开机。5.关闭本工程,按此路径打开 Example 工程: 2_Demo\11_pcie_test\ipcore\pcie_test\pnr\example_design。1.打

【Library】:选择 usim 则是 GTP 前仿库,vsim 则是 VOP 后仿库,ALL 则包括这两种仿真 库,默认选择 ALL;【Compiled Library Location】:编译出来的库的位置,默认是在当前工程下面;【Simulator】:第三方仿真工具,目前支持ModelSim和QuestaSim,本教程选择ModelSim;【Family】: 指定芯片系列对应的仿真库进行编

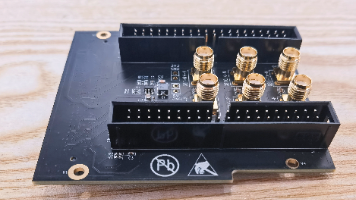

MES-FMC-LPC-IO子卡为FPGA开发板FMC接口扩展2路40pin扩展IO,共68个用户IO,提供丰富的IO连接外部设备,MES-FMC-LPC-IO子卡的40pin扩展IO与小眼睛科技FPGA开发板的40pin IO线序一致,配套外设模块在MES-FMC-LPC-IO子卡上可直接连接使用。:采用 FMC 标准的设计,可通过更换 FMC 模块并对 FPGA 设计略作调整,将现有的 FPG

在接收首部的同时进行校验和的检查,将首部接收的所有数据相加,存入32位寄存器,再将高16位与低16位相加,直到高16位为0,再将低16位取反,判断其是否为0,如果是0,则检验正确,否则错误,进入IDLE状态,丢弃此帧数据,等待下次接收。工程中的arp_rx.v为ARP接收模块,实现ARP数据接收,在IDLE状态下,接收到从MAC层发来的arp_rx_req信号,进入ARP接收状态,在此状态下,提取

(此为默认安装路径)。若电脑之前未安装 过则需要安装此运行库后才能运行 PDS,点击“是”按钮进行安装;若电脑之前已安装过此运 行库则无需再次安装,点击“否”按钮不进行安装即可。(5)选择接受许可协议,点击“I Agree”按钮,进入选择安装路径选择框,如下图所示, 默认安装路径为 C:\pango\PDS_2022.1,建议采用默认路径。(9)点击“是”进入运行库安装界面,选择同意许可条款和条件

(3)为方便管理license文件,建议在PDS软件安装目录下新建一个license文件夹存放license文件。若电脑之前未安装过则需要安装此运行库后才能运行PDS,点击“是”按钮进行安装;若电脑之前已安装过此运行库则无需再次安装,点击“否”按钮不进行安装即可。(5)选择接受许可协议,点击“I Agree”按钮,进入选择安装路径选择框,如下图所示,默认安装路径为C:\pango\PDS_2022

利用 Select Net 对话框,可以把 Debug Core 的工作时钟、 触发信号、数据信号与设计中的网线连接起来,方法是右侧选中 Debug Core 的信号,在左侧下方选中需要连接的网线,单击 Make Connections 按钮,即可以完成一条或者多条信号的连 接,所有信号都连接好之后,单击 OK 按钮。在配置位流文件后,便可将该文件下载到器件中。选中初始化链检测到的 FPGA 器件

当计数器计数到 25'd24_999_999 时,计数过程包含了从 0~26'd2499_9999 的时钟周期, 故而总时长时 25’d25_000_000 ×?在 module 之前添加文件头,文件头中包含信息有:公司,作者,时间,设计名,工程名, 模块名,目标器件,EDA 工具(版本),模块描述,版本描述(修改描述)等信息;单个状态计数 25_000_000,即 24_999_999 = 25

(2)按照“1.FPGA&CPLD 的下载”流程进入到下载界面,选择新的.sbit 文件,右击器件 中的【Flash】,在下拉菜单中选择【Program】,等待进度条消失出现“[Verify Eflash]execute successfully…(1)生成位流文件(.sbit)后,可以把.sbit 文件下载到 FPGA 或 CPLD 中,首先将 JTAG 下载器与 PCB 板连接并上电,点击菜单