简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

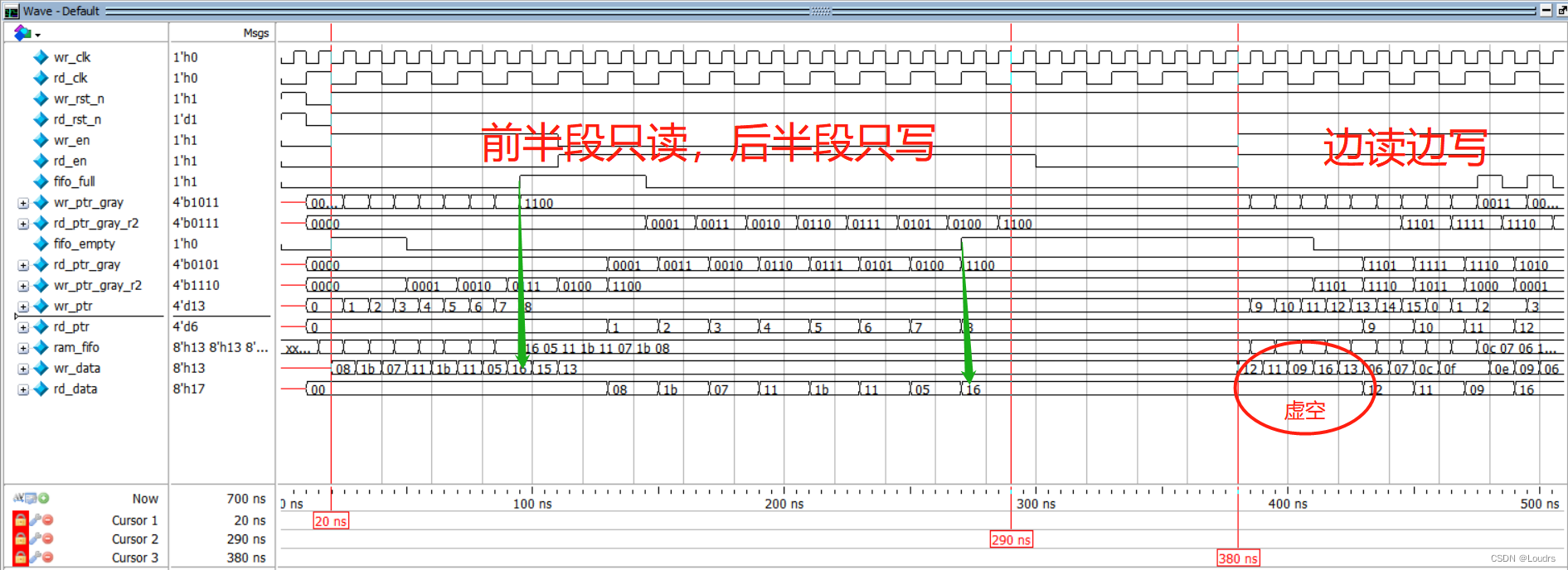

异步FIFO设计原理与设计方法以及重要问题汇总(包含verilog代码|Testbench|仿真结果)

异步FIFO主要由五部分组成:RAM、写控制端、读控制端、两个时钟同步端双端口RAM:此处为伪双端口RAM进行数据存储与读出,有两组数据线、地址线、时钟线。写控制端:写指针与满信号产生器,用于判断是否可以写入数据,写操作时,写使能有效且FIFO未满。读控制端:读指针与空信号产生器,用于判断是否可以读取数据,读操作时,读使能有效且FIFO未空。两个时钟同步端:读指针同步到写指针域进行“写满”判断,写

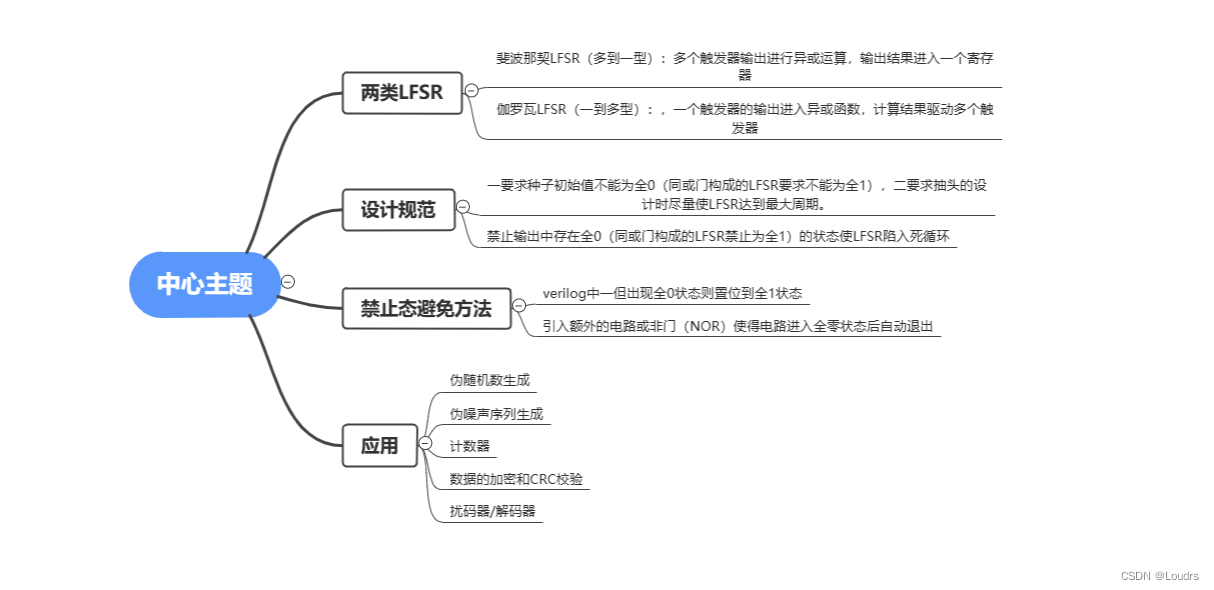

线性反馈移位寄存器LFSR(斐波那契LFSR(多到一型)和伽罗瓦LFSR(一到多型)|verilog代码|Testbench|仿真结果)

LFSR广泛应用于伪随机数生成、伪噪声序列生成、计数器、数据的加密和CRC校验、扰码器/解码器、信号生成和测试等领域,是一种非常有用的数字电路设计技术。LFSR主要分为斐波那契LFSR(多到一型)和伽罗瓦LFSR(一到多型)。对于斐波那契LFSR(多到一型)多个触发器输出进行异或运算,输出结果进入一个寄存器,对于伽罗瓦LFSR(一到多型),一个触发器的输出进入异或函数,计算结果驱动多个触发器。LF

到底了