简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

测试原理(二)

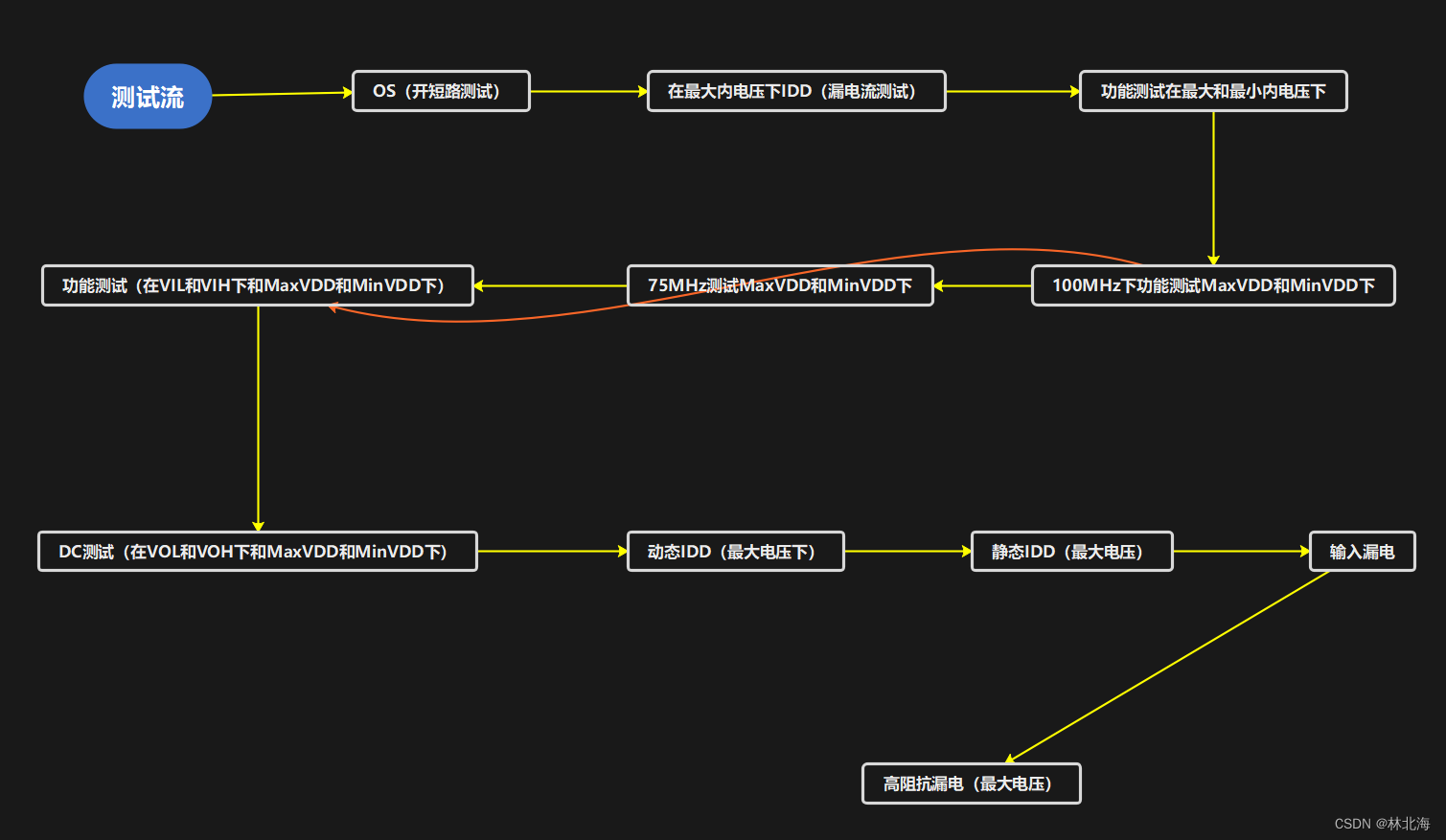

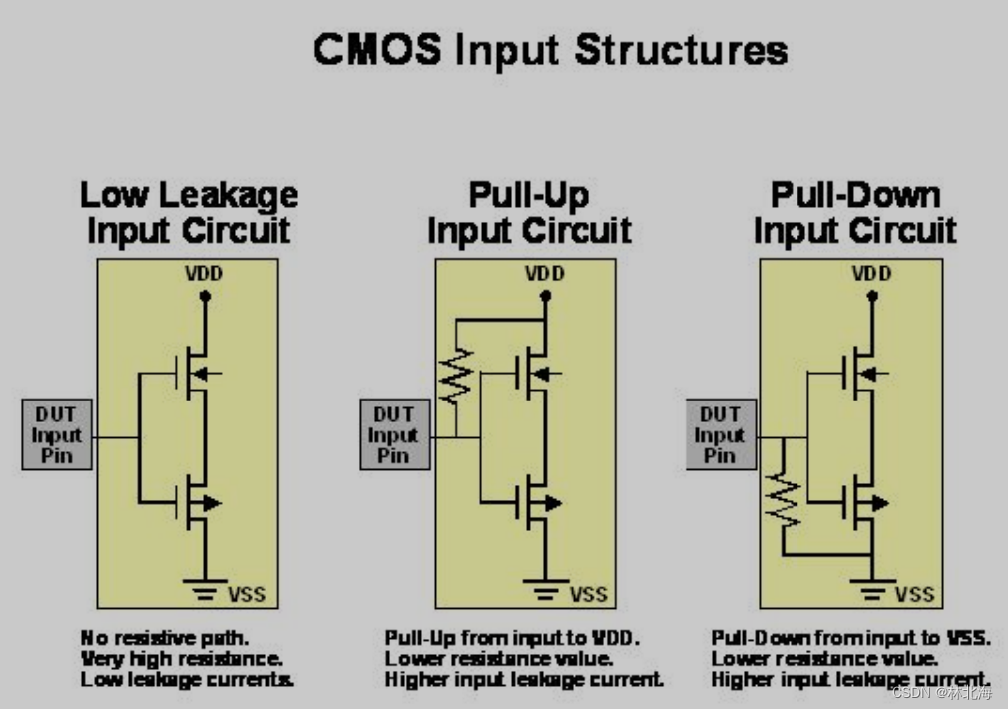

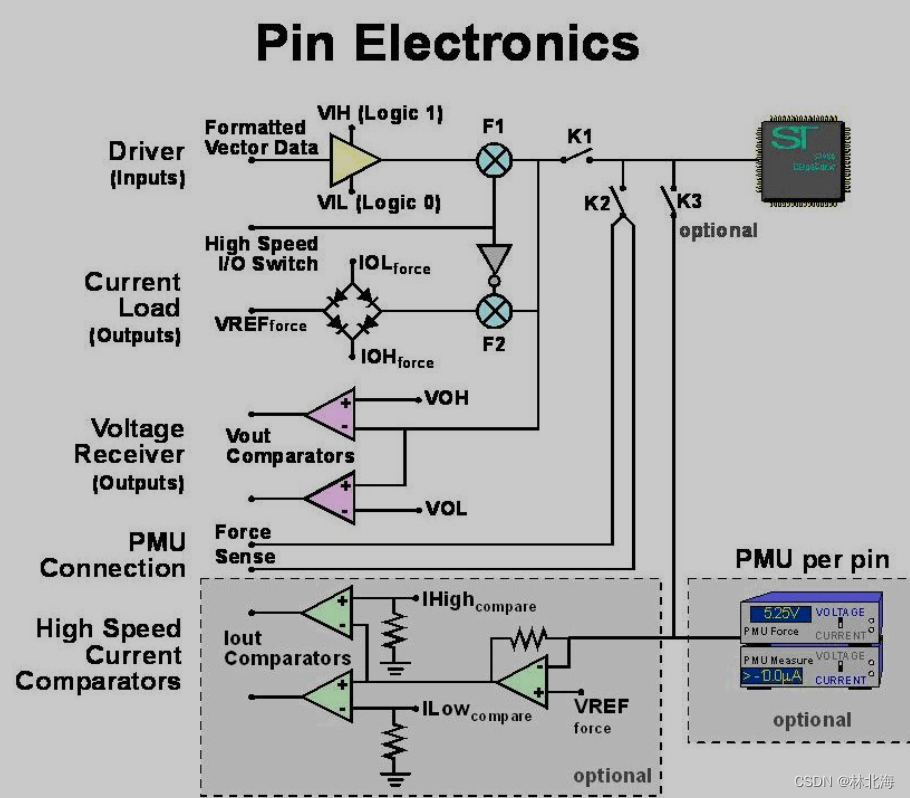

部分管脚具有上拉和下拉,所以会导致每个管脚的所可以吸收的电流大小并不相同,所以集体测试的方法并不适合用来测试。串行测试是对每一个管脚进行测试,所以每一个测试管脚与不同管脚之间的具有电压差,所以使管脚之间的漏电流会更加的明显,但是会大大的增加测试的时间。IIL测试测量的是输入管脚到VDD的阻抗,IIH测的是的输入到VSS的阻抗(VSS在COMS电路中这是接地,VDD是芯片内部的电源)集体测试对COM

芯片测试基础

对与晶圆(wafer)上每一个独立电路单元(Die)进行检测,也是区分是否为良品的第一道测试也成为“Wafer Sort”、CP测试。·封装完成后的测试,确保满足原有的要求,称为“Final Test”、FT测试、成品测试。·保证PASS中的产品中没有不合格的,保证Package Test的正确性。·器件的工作范围·经过老化后,测试芯片是否出现参数偏移·跟为严格的温度、老化等测试·保证购买芯片的合

到底了