VCS/irun/verdi编译命令/vhdl&verilog混合编译/.so联合编译/sv_lib/sv_liblist/sv_root

目录1.VCS的编译解析1.1一步编译法1.2 三步编译法1.3 VCS动态加载DPI shared lib (.so)2.irun编译命令3.verdi也可以编译1.VCS的编译解析1.1一步编译法这种适合都是verilog的工程下面是一个可以使用的vcs makefile用于编译VCS 编译仿真方法总结VCS编译命令摘自:SYNOPSYS...

目录

1.VCS的编译解析

1.1 VCS编译

1.1.1一步编译法

这种适合都是verilog的工程

下面是一个可以使用的vcs makefile用于编译

![]()

还可以加上+error+num 让编译器遇到多少个错误后停止

还可以加上 -top xxxx 这样多余文件不在top下各层的例化内的文件编译就算有错也不会停下编译 多用在有common ip 的情况下

| -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

有时加上-Mupdate而不带0时 目的是想增量编译,但会出现不能检测到修改的文件而导致编译一半自动停止,这时需要 clean之前的所有编译的工程文件。

上面的 -kdb -lca 这两个命令可以让verdi直接打开VCS编译之后的sim.daidir, 这样verdi可以直接trace 代码

verdi使用如下命令即可打开verilog工程 并可trace代码

verdi -dbdir ./simv.daidir -workMode hardwareDebug -nologo -autoalias -ssv –ssy -ssz摘自:SYNOPSYS VCS常用命令使用详解,这篇文章里详细的给出了vcs的编译和运行

VCS对verilog模型进行仿真包括两个步骤:

1. 编译verilog文件成为一个可执行的二进制文件命令为:

$> vcs source_files

2. 运行该可执行文件

$> ./simv (simv是一个可执行文件,即可直接运行)

类似于NC, 也有单命令行的方式:

$> vcs source_files -R

-R 命令表示, 编译后立即执行.

下面讲述常用的命令选项:

-cm line|cond|fsm|tgl|obc|path 设定coverage的方式

+define+macro=value+ 预编译宏定义

-f filename RTL文件列表

+incdir+directory+ 添加include 文件夹

1.1.2 三步编译法

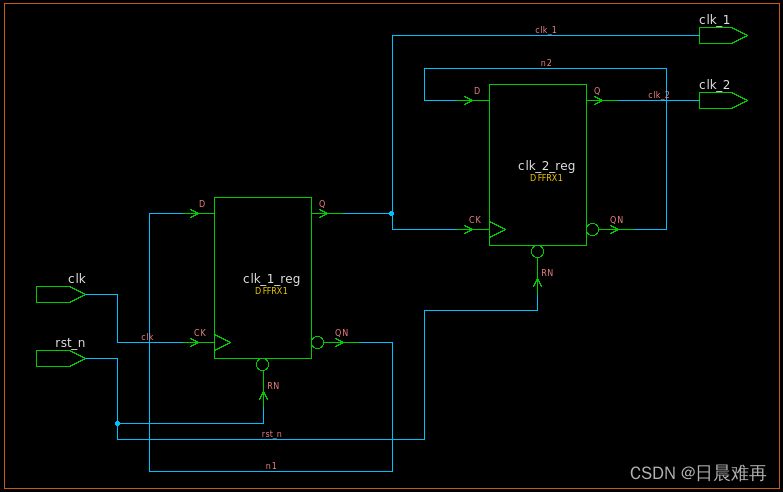

这种适合VHDL和verilog混合工程的编译

1. vhdlan compile VHDL.

2. vlogan compile verilog.

3. vcs elaboration.

例如下:

在最后一步 vcs elaboration中需要指定top file这里是gxx_wrapper

1.1.3 VCS动态加载DPI shared lib (.so)

VCS动态加载DPI shared lib,在vcs compile之后,调用GCC执行C的编译,产生so文件。

在vcs run的时候,手动加载so。包括以下2种种命令都行:

1) -sv_liblist,指定一个so的list文件bootstrap file,其中的so不需要加后缀名。

2) -sv_lib,加lib名,不需要加后缀。

-sv_root是指定DPI shared lib的根目录,可以识别环境变量$ENV,就很有用了。

以上先设置:

-sv_root /home/user

-sv_liblist Bootstrap.file

或者:

-sv_root /home/user

-sv_lib myclibs/lib1

-sv_lib myclibs/lib3

-sv_lib proj1/clibs/lib4

...

就可以调用

/home/user/myclibs/lib1.so

/home/user/myclibs/lib3.so

/home/user/proj1/clibs/lib4.so

![]()

sv_liblist如下:

所以这些 .so的全路径为:

$SIM/model/xxxxxxx/so/jdi.so

1.2vcs 编译后用verdi打开工程

要使用以下命令打开vcs的编译工程,有两个限制

1.vcs只能使用一步编译法

2.vcs编译过程中 加上-kdb选项生成 kdb.elab++

![]()

上面是打开vcs编译库的命令行形式,当然也可以先打开verdi, file--》import Design---》from Daidir ,然后选择目录simv.daidir来打开工程

2.irun编译命令

3.verdi编译

3.1verdi直接打开verilog

verdi -f filelist.f -top rtl_top

verdi xxx.v

verdi xxx.gv.gzverdi是可以直接打开verilog,网表及filelist文件的。也可以trace代码【应该是简单LINK,而没有compiler】

3.2 verdi编译后打开

不同于vcs的vhdlan和vlogan以及vcs这三个命令,verdi编译使用的是vhdlcom和vericom,具体过程如下

vhdlcom -f xxx.vhdl.lst

vericom -f xxx.veri.lst

verdi -lib work -top xxx三步编译完之后加载代码有两种方法:

1. 用命令行直接加载

verdi -lib work -top tb_top_design &

2.GUI加载

打开verdi后:File -〉import design -〉From Library,然后在Library中选

择work库,再在右栏的Design unit中找到top_design, 点击ok完成加载。

详细可参考:

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)