使用NE555制作多谐振荡器

本文对555定时器电路结构以及多谐振荡器的电路原理进行了细致的讲解,并且进行了仿真、上板的手段进行了验证,555定时器作为大家学习数字电路过程中的一门必修课,有很多同学可能一直对这款芯片产生困惑。然而理论结合实践的方式才是学习的最佳方式,希望本文能给读者带来一些帮助。

555定时振荡器也就是通常所说的555定时器。555定时器的用途非常广泛,可以生成各种类型的脉冲、创建时间延迟,也可以用于脉冲宽度调制(PWM),555定时器最常见的用途是为电路产生时钟信号。

本文对555定时器以及基于555定时器的多谐振荡器应用的原理进行了细致的讲解,并且分别进行了仿真验证以及实物验证。

一、555定时器的结构和工作原理

1.1、 电路结构

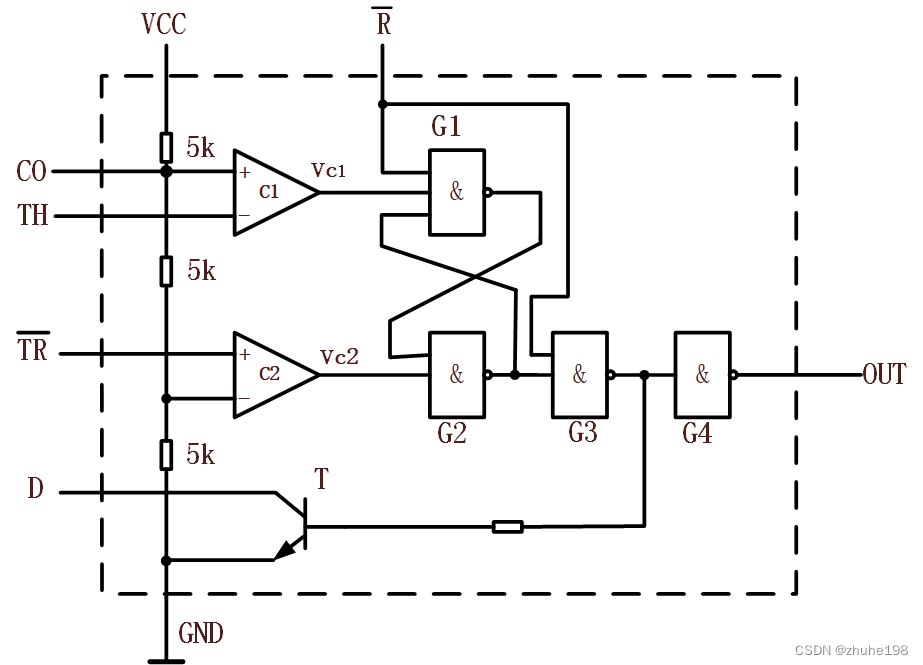

图1所示为555集成定时器的电路结构图,555定时器电路由五个部分组成:

图1.1 555定时器结构图

(1)由三个阻值为5k的电阻组成电阻分压器,为电压比较器C1和C2提供基准电压Vr1和Vr2;当5脚CO悬空时,Vr1=(2/3)Vcc,Vr2=(1/3)Vcc。CO为控制电压输入端,可在此外加控制电压改变基准电压值。CO端不用时,外接 0.01uF 的去耦电容,以消除干扰,保证基准电压不变。

(2) 集成运算放大器组成两个电压比较器C1和C2,每个电压比较器两个输入端标有“+”号和“-”号:

图1.2 运放符号

当v+>v-,比较器输出vo=1;

当v+<v-,比较器输出vo=0.

(3)基本SR触发器,其置0端(R端)和置1端(S端)均为低电平有效触发,RS的值取决于比较器的输出(R=Vc1,S=Vc2)。

(4)放电三极管 T,相当于一个受控电子开关;当输出OUT为0时,T导通;输出OUT为1时,T截止。

(5)输出缓冲器G3和G4,主要用于提高电路的带负载能力,同时也隔离了负载对定时器的影响。

1.2、 引脚功能

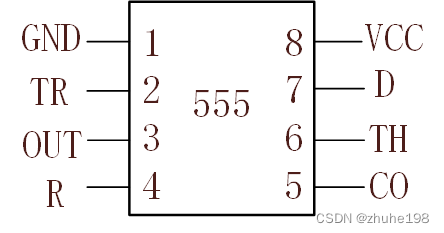

由图1.3可知555定时器各引脚端如下:

图1.3 555定时器引脚图

1端GND为接地端;

2端TR为低电平触发端,也称为触发输人端,由此输入触发脉冲。

3端OUT为输出端,输出电流可达 200mA,可直接驱动继电器发光二极管、扬声器等。

4端R为复位端,当R=0时,输出OUT为低电平,正常工作时,R必须接高电平。

5端CO为电压控制端,如果在CO端另加控制电压,则可改变比较器C1、C2的基准电压,工作中不使用 CO端时,一般都通过一个0.01uF 的电容接地,以消除干扰。

6端TH为高电平触发端,又叫阈值输入端,由此输入触发脉冲。

7端D为放电端。

8端Vcc为电源端,可在4.5~16V范围内使用,若为CMOS电路,则Vcc=3~15V.

1.3、工作原理

当 555 定时器的复位端R 为低电平时,不管其他输人端的状态如何,输出 OUT始终为低电平,放电三极管 T饱和导通。这说明其在 555 定时器电路的输人端中的控制级别最高。正常工作时,一般应将其接高电平。

当复位端R为高电平,且 5脚 CO端不使用外接控制电压时,比较器 C1和C2的比较电压分别为 Vr1=2/3Vcc和Vr2=1/3Vcc,工作状态将受阈值输入、触发输入的影响:

(1)当TH>2/3Vcc,TR>1/3Vcc时,比较器C1输出Vc1为低电平,C2输出Vc2为高电平,基本 SR 触发器置0端有效,被置 0,放电三极管T导通,输出端OUT为低电平。

(2) 当TH<2/3Vcc,TR<1/3Vcc时,比较器 C1输出 Vc1为高电平,C2输出 Vc2为低电平,基本 SR 触发器置 1端有效,被置 1,放电三极管T截止,输出端 OUT为高电平。

(3) 当TH<2/3Vcc,TR>1/3Vcc时,比较器 C1输出 Vc1为高电平,C;输出Vc2也为高电平,即基本 SR 触发器 R=1,S=1,触发器状态不变,电路亦保持原状态不变。

由于阈值输入端 TH为高电平(>2/3Vcc)时,555 定时器输出OUT 为低电平,因此也将该端称为高电平触发端(或称高触发端)。而触发输入端TR为低电平(<1/3Vcc) 时,555定时器输出 OUT 为高电平,因此也将该端称为低电平触发端(或称低触发端)。

如果在电压控制端 CO(5 脚)施加一个外加电压(其值在0~Vcc之间),则比较器的基准电压将发生变化,电路相应的阈值、触发电平也将随之变化,进而影响整个电路的工作状态。

1.4、原理总结

表 1 .2所示为 555 定时器的功能表,由电路框图和功能表可以得出如下结论:

表1.2 555引脚功能表

| 阈值输入(TH) | 触发输入(TR) | 复位(R) | 输出(OUT) | 放电管T |

| X | X | 0 | 0 | 导通 |

| <2/3Vcc | <1/3Vcc | 1 | 1 | 截止 |

| >2/3Vcc | >1/3Vcc | 1 | 0 | 导通 |

| <2/3Vcc | >1/3Vcc | 1 | 不变 | 不变 |

(1)555 定时器有两个阈值,当CO端悬空不用时,它们分别是2/3Vcc和1/3Vcc。

(2)输出端 3 脚和放电端 7脚的状态一致,输出低电平对应放电管饱和导通,输出高电放平对应放电管截止。

(3)输出端状态的改变有滞回现象,回差电压为1/3Vcc.

(4)输出与触发输入反相,可简记口诀“都大为0,都小为 1,一大一小保持不变“,以帮助理解 555定时器的输人输出关系。

掌握以上四条,对分析 555 定时器组成的电路将十分有利。

二、555定时器构成多谐振荡器

2.1、 电路组成及其工作原理

图2.1(a)所示为555定时器构成的多谐振荡器电路,电阻R1、R2和电容C是外接定时元件。5脚CO端通过一个0.01uF的电容接地,在工作中不使用外接控制电压。

电路的工作原理如下:

(1)接通电源Vcc后,Vcc经电阻R1和R2,对电容C进行充电,使vc逐渐升高,当vc上升到2/3V时,555定时器内比较器C1的输出,即基本SR触发器的R跳变为低电平,比较器C2的输出即基本SR触发器的S端跳变为高电平,使基本SR触发器置0有效,输出端OUT即vo=0,放电管T导通。

(2)电容 C通过电阻R2和7脚的放电管T放电,使vc下降。当vc下降到1/3Vcc时,比较器C1的输出即基本 SR触发器的R端跳变为高电平,比较器C2的输出即基本SR触发器的S端跳变为低电平,使基本SR触发器置1有效,输出端OUT即vo又由0变为1,放电管T截止。

(3)Vcc又经R1和R2再次对电容C进行充电,使vc再次升高。如此重复上述过程,周而复始,在输出端vo就产生了连续的矩形脉冲。电路的工作波形如2.1(b)

所示。

(a)多谐振荡器电路图 (b)工作波形

图2.1 用555定时器构成的多谐振荡器

2.2、 主要参数计算

估算多谐振荡器有两个暂稳态,持续时间分别为tp1和tp2;

电容 C充电的时间为:

电容C放电的时间为:

因此,输出矩形波的振荡周期为:

![]()

振荡频率为:

![]()

脉冲宽度与周期之比称为占空比q:

![]()

三、多谐振荡器验证与实现

3.1、multisim 仿真

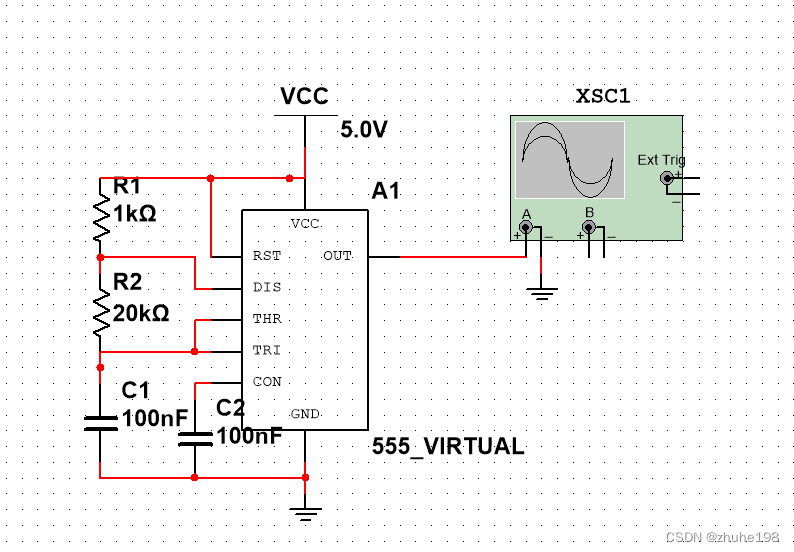

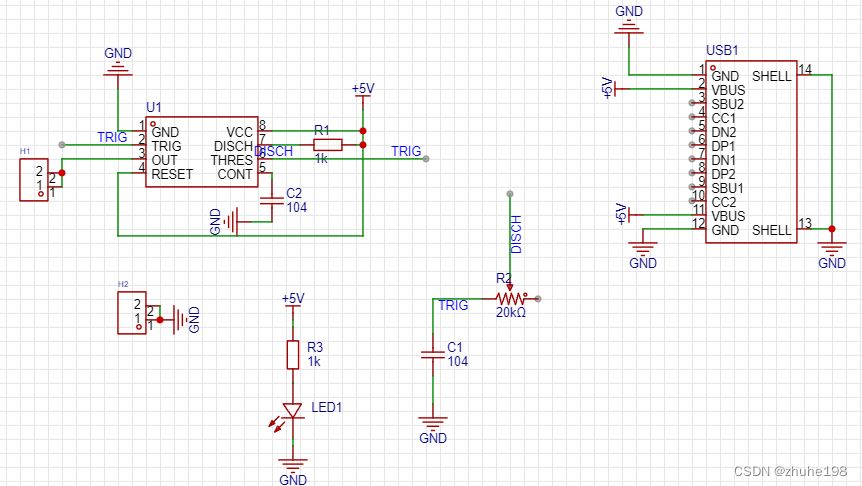

在上述理论中,相信你已经对555定时器已经有了一定的了解,现在我们通过仿真先验证一下电路的可行性。如图3.1所示,在multisim中加入了555定时器以及其他定时元件电阻电容等,本实验中充放电电容选用的是100nF,电阻R1为1K,R2为20K,并加入示波器观测波形。

图3.1.1 multisim 电路图

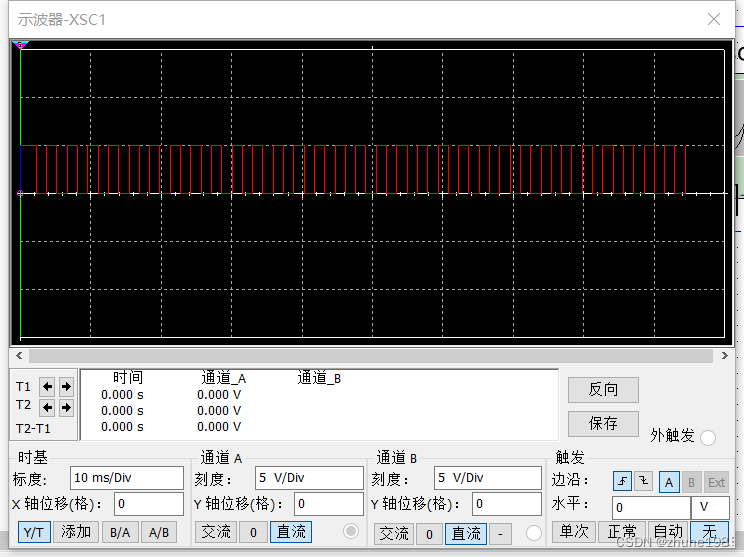

如图3.2所示,为上述电路中555定时器产生的波形图,已知时基的标度为10ms/div,一个div大概有3.5个周期的波形,因此该波形一个周期大概是10/3.5=2.857ms。

再让我们根据2.2中周期的波形计算公式来计算一下:

0.7*(1000+2*2000)*0.0000001=0.00287s,也就是2.87ms,与实际得到的结果基本一致。

图3.1.2 multisim 仿真波形图

3.2、电路板设计

仿真通过了,下面就是上板子!嘉立创每个月提供的两次免费打样的活动,让我告别了手动飞线。并且立创EDA确实好用,有很多云端器件库,大大提高了设计的效率(为国产EDA软件点赞)。

图3.2.1是多谐振荡器设计的原理图,可以看见电路非常简单,在电路中我还加入了一个TYPE-C端口用来给电路供电,以及一个电源指示灯,另外我将R2改成了一个可调电位器,这样就可以手动调节R2的大小,以便于调节波形的频率。

图3.2.1 原理图设计

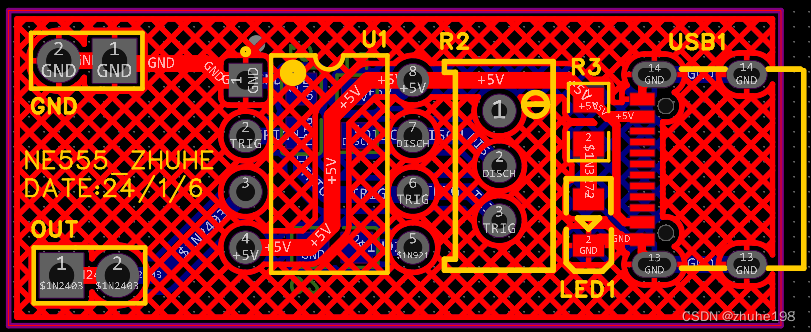

本电路PCB设计没有什么特殊的要求,布局布线尽量按照原理图中的来即可。

图3.2.2 PCB设计

3.3、实物验证

焊接后的板子与3D仿真图基本一致,下面开始用示波器测试波形。

图3.3.1 实物图

将板子通过数据线连接到示波器的USB口进行供电,并将探头连接到板子的信号输出上,可以看见示波器立刻显示了一个方波,频率为547Hz.

图3.3.2 实物测试1

将电位器朝着增大的方向旋转,增加阻值,直到旋转到频率不变时,电位器达到最大阻值20K,此时示波器显示频率为325Hz,再回顾3.1中计算的周期为2.857ms,对应的频率为1/T=1/0.00287=348.432Hz,实物与理论结果基本一致(产生偏差很正常,电位器可能存在微弱偏差,导线中也有一定阻抗,都会影响频率的输出结果)。

图3.3.3 实物测试2

将电位器朝减小方向旋转,随着电阻R2的减小,电容充放电时间加快,因此输出频率增大,在频率达到8.567KHz时,可以看见波形的占空比也明显增大。因此如果想产生占空比为50%的时钟信号时,应保证R2>>R1。

图3.3.4 实物测试3

四、总结

本文对555定时器电路结构以及多谐振荡器的电路原理进行了细致的讲解,并且进行了仿真、上板的手段进行了验证,555定时器作为大家学习数字电路过程中的一门必修课,有很多同学可能一直对这款芯片产生困惑。然而理论结合实践的方式才是学习的最佳方式,希望本文能给读者带来一些帮助。仿真和电路设计工程文件由于比较简单,我暂时不放出来了,有需要的同学可以在评论区留言,如果需求的比较多的话,我会免费将工程文件上传到资源中。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)