FIFO读写时序理解——almost_empty、almost_full

FIFO读写时序理解——almost_empty、almost_full

FIFO时序理解——almost_empty、almost_full

目录

为什么要设计almost_empty?

有Full、Empty,为什么还要加上Almost Full和Almost Empty?——不丢失数据和多读数据。

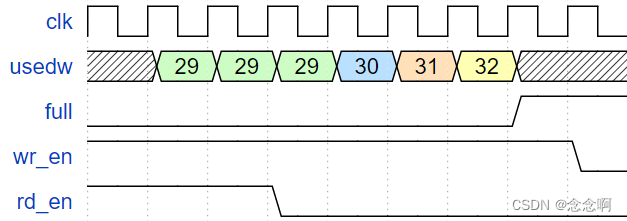

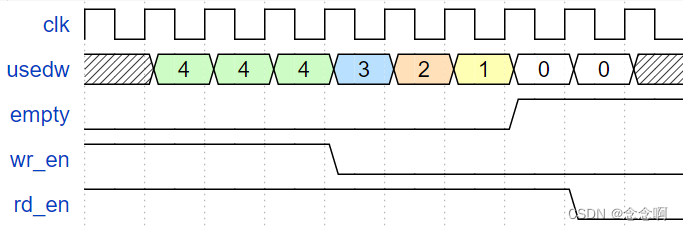

在写FIFO时,我们一般在时序逻辑中判断Full Signal:如果Full Signal为低,说明FIFO没满,于是拉高wr_en。但是这有时会出问题,如下图。

full:

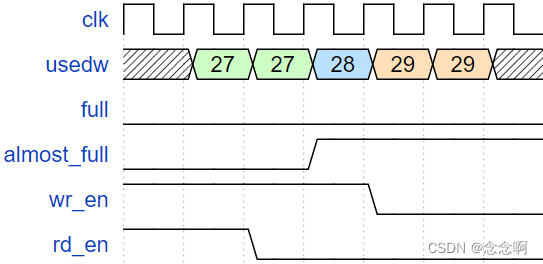

所以,在FIFO使用时,使用Almost_full信号来控制FIFO的读满预警,尽量让FIFO有足够满预警裕量。例如,在usedw为32才是真的满了,你可以设为28的时候就给出满预警,可以保证设计的可靠和安全。

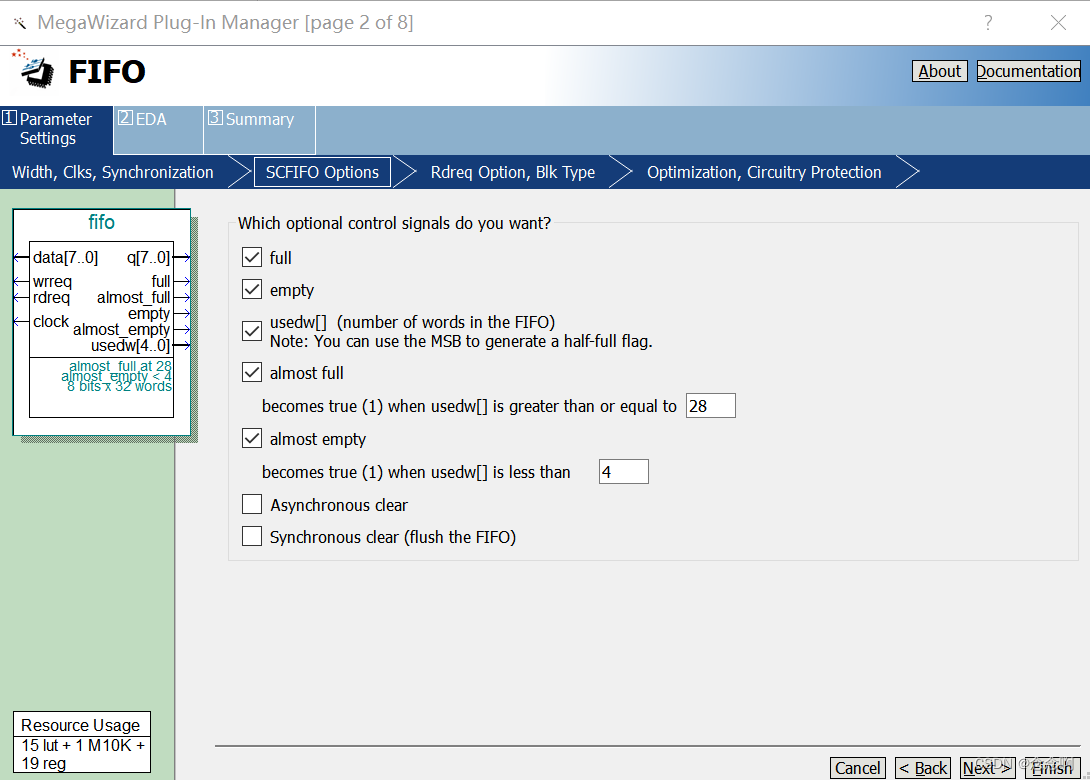

设置:

- full:FIFO满的标记信号,为高电平时表示FIFO已满,不能再进行写操作。

- empty:FIFO空的标记信号,为高电平时表示FIFO已空,不能在进行读操作。

- usedw[](number of words in theFIFO):显示存储在FIFO中数据个数的信号,Note:(可以使用最高位作为FIFO的半满指示信号。)

- almost full:接近满信号,当usedw信号的值大于或等于我们设置的almost full的值时,该信号置为高电平,是full信号的提前提示信号。

- almost empty:接近空信号,当usedw信号的值小于我们设置的almost empty的值时,该信号置为高电平,是empty信号的提前提示信号。

- Asynchronous clear:异步复位信号,用于复位所有输出状态端口。

- Synchronous clear(flush the FIFO):同步复位信号,用于复位所有输出状态端口。

增加almost_full:

empty:

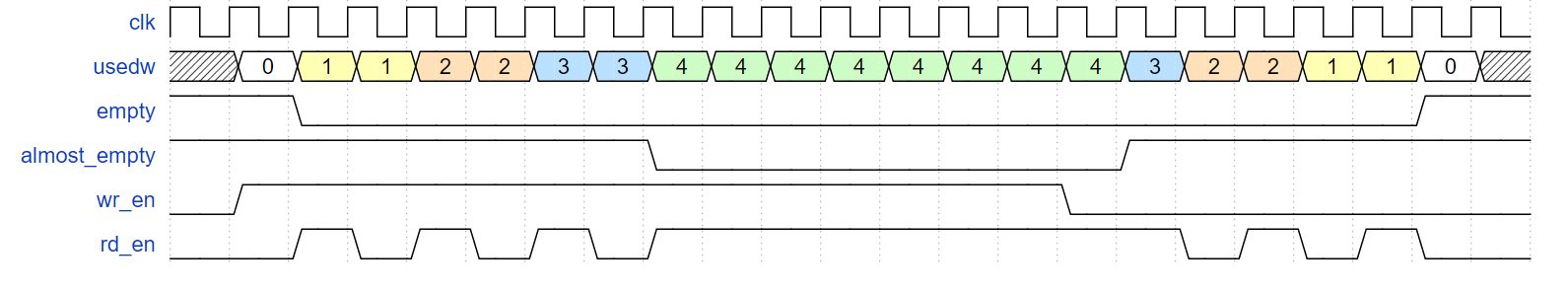

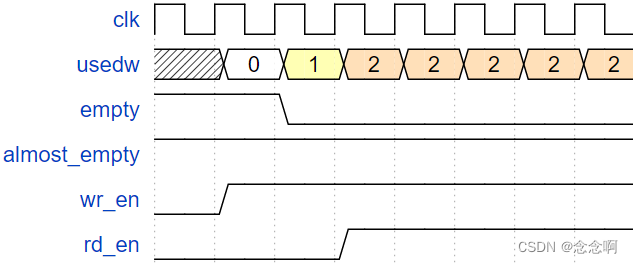

在读FIFO时,我们一般在时序逻辑中判断Empty Signal:如果Empty Signal为低,说明FIFO有数据可以读,于是拉高rd_en。但是这有时会出问题,如下图。

假设此时已经是FIFO的最后一个数据,由第6个clock的rd_en,在第7个clock中Empty Signal才会拉高,而在第7个clock中,时序逻辑输入的Empty Signal是上一个时钟的低电平信号,于是认为还有有效的FIFO数据,re_en继续为高。

有两种方法解决这个问题:

- 下一个时钟再去判断Empty Signal;

- 配合使用Almost Empty Signal来处理;

第一种方法每两个clock才能处理一个FIFO数据,想要快速地读出数据,这种方法显然不合适。

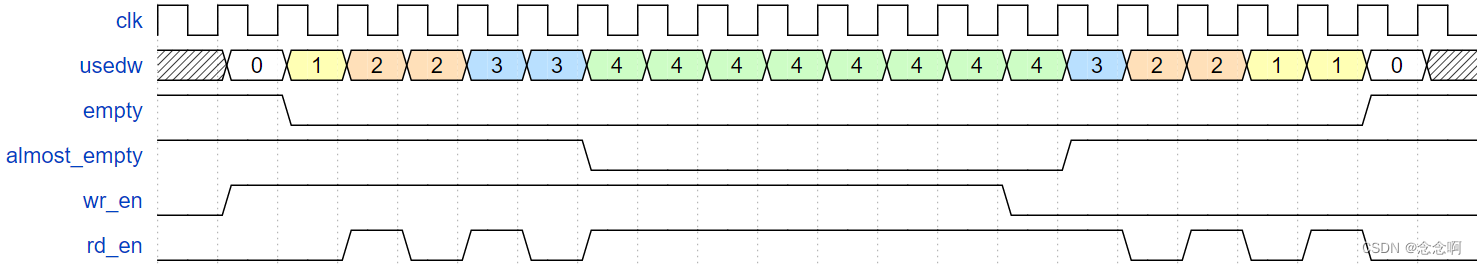

方法二的思路是:将FIFO的Empty和Almost_empty以及读使能配合起来使用,来保证能够连续读,并准确的判断FIFO空满状态,提前决定是否能启动读使能。

具体的实施办法是:

-

当Empty为1,不能读;

-

当Empty为0,Almost_empty为0时,可以连续读;

-

当Empty为0,Almost_empty为1时,读一拍停一拍。如果上一拍读使能ed_en=1,那么不能读;如果上一拍读使能rd_en=0,可以读。

这样,在数据连续读写时,既能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。

增加almost_empty:

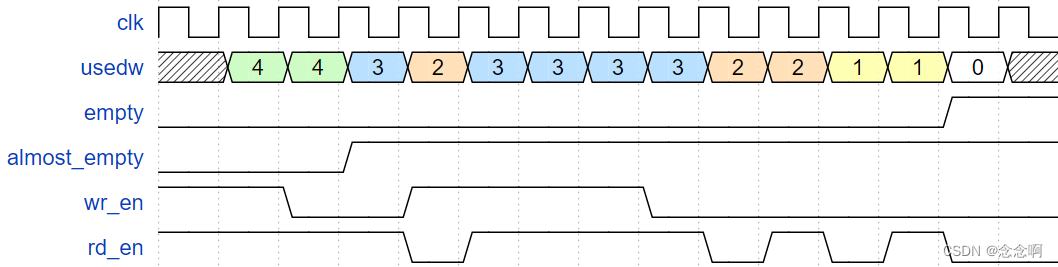

一种错误示范:

- almost_empty=0时,可以连读;

- 当almost_empty=1同时wr_en=1,可以连读;

- almost_empty=1,wr_en=0,读一拍停一拍。

实际上,这种是没有必要的。读只需要通过almost_empty来判断是否连读,不需要看wr_en。当alempty =1时,就慢慢读,读一拍停一拍。

读只需要通过almost_empty来判断是否连读,不需要看wr_en。当alempty =1时,就慢慢读,读一拍停一拍。

绘图工具:https://wavedrom.com/editor.html

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)