(电赛)数字信号发生方案和dds芯片选型经验

电赛经验总结贴,围绕dds dac芯片原理解读,dds芯片选型指南,程控幅度调节方案汇总

目录

前言

通常,电赛中的信号发生源设计都是数字方案实现的,模拟的方案不管是精度、信号质量,还是控制频率、幅度、相位的方便、稳定性,都比不上数字方案。

这里所说的数字方案,实际指的是是依靠一些特定的模拟芯片完成信号发生,而我们需要做的只是通过控制板(单片机或fpga等)与其进行通信。

而具体的数字方案也可以分为两种,第一种是fpga+DAC,另一种是MCU+dds。下面我将对这两种方案进行进一步阐述。

(标题一的部分是基础和原理介绍内容,不感兴趣的可以自行跳过)

一、什么是DAC、DDS?

1.DAC介绍

DAC(Digital to Analog Converter)就是数字—>模拟转换器,是将数字的编码信号转化为模拟的电压信号的器件。目前组要使用的DAC芯片主要是来自于ADI公司的。

ADI公司在其DAC芯片的目录中将DAC芯片分为了四类:

1数字电位器(DigiPOT)(数控电阻)

2高速数模转换器≥30MSPS

3集成式/特殊用途数模转换器

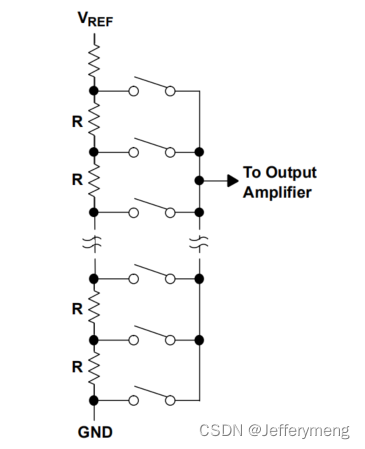

4精密DAC

最早先的数字到模拟信号转换电路的结构很简单,是一种电阻串联分压网络构成的,每个电阻的阻值相同,数字码对应了电阻串联网络的开关是否导通,在输出将所有电压相加,获得相应的模拟电压。现在的很多数字电位器就是这种结构,以及DAC8571也是采用这种结构。

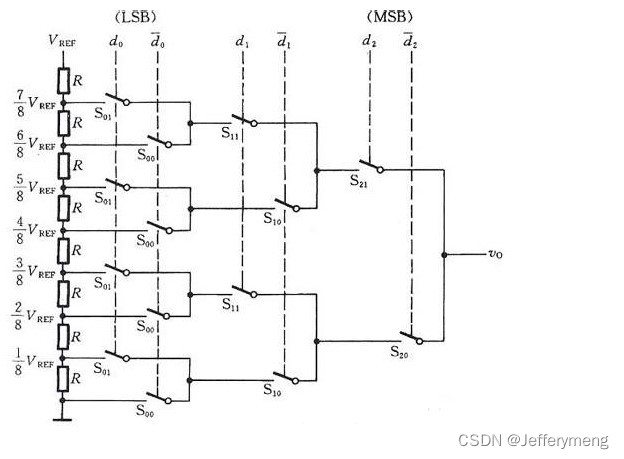

在DAC芯片中,比较简单的结构是如下的这种,采用电阻的树状结构,可以获得Vref/(2^n) 的LSB电压,并且需要的电阻也比较少,是R✖(2^n)。但这种电路需要的模拟开关比较多,也逐渐被淘汰。

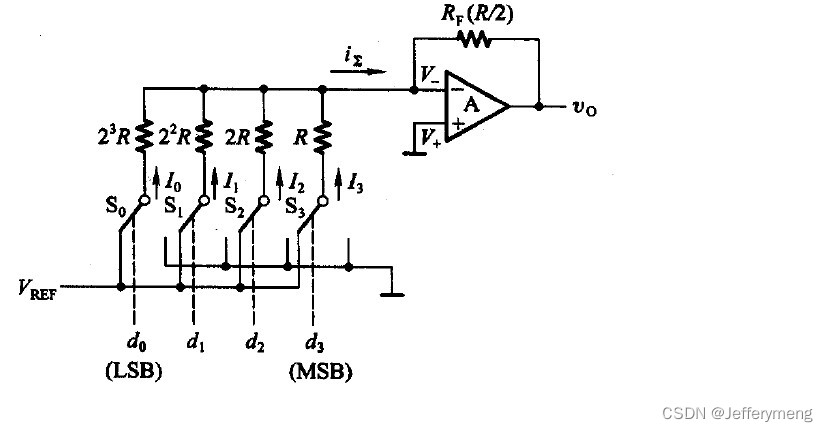

后来有了这种(也是模集中经常最先介绍的DAC结构),从低电位到高电位的电阻呈现2倍的倍增,其缺陷是位数一旦变大,电阻将会需要变得非常大,芯片的面积太大或是大电阻的准确性的缺陷都是十分致命的。

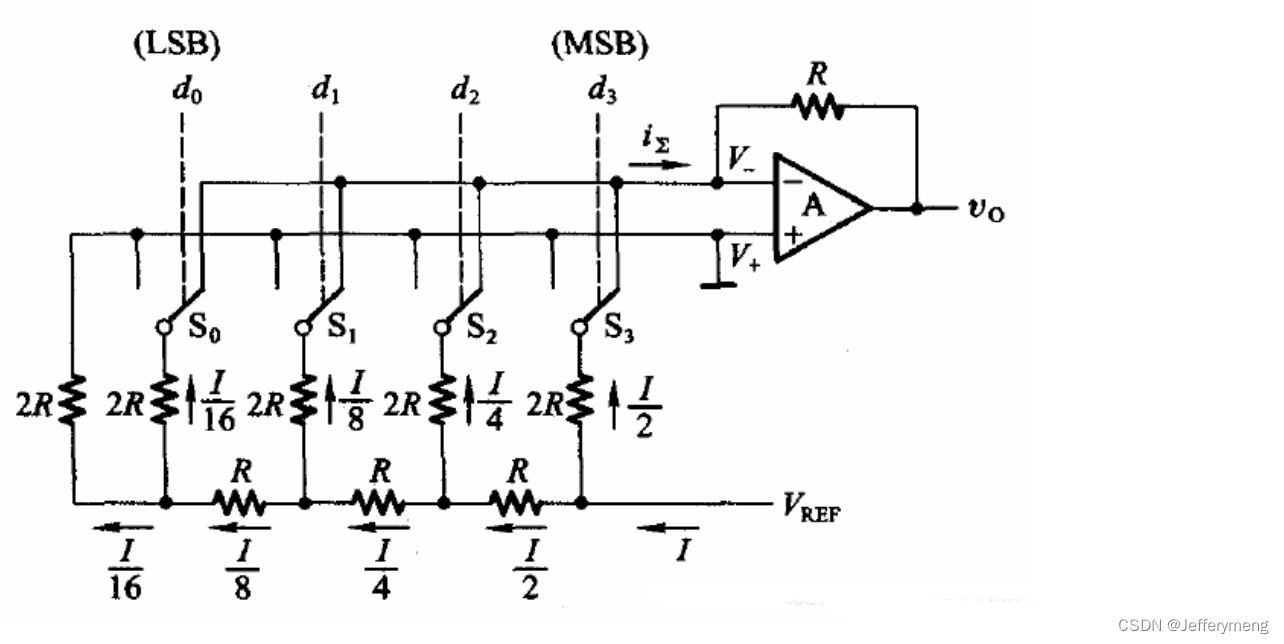

R-2R结构:这种结构的精妙之处在于,对于每个节点来说,到地的等效电阻都是2R,因此再将一个2R电阻与之并联,就可以获得与之相等的电流,电流通过这种效应被不停的缩小二分之一,从而实现了电压的2次方的倍减。这时,不仅需要的模拟开关更少了,而且电阻器件的面积也更小了,增加了一个运放的面积与电阻等无源器件相比也是很小的。

关于DAC的性能指标,在电赛的应用中,我们主要关注的是上限频率(最小的settle time),量化精度(一个LSB的电压),输出电压范围(最大能输出多大的电压)、供电电压范围(能否为负,最大到多少),输出模式(电压输出或是电流输出)。

2.DDS介绍

DDS的全程是Direct Digital Frequency Synthesis,翻译为“直接数字频率合成”,是专门用于产生正弦信号的专用芯片。

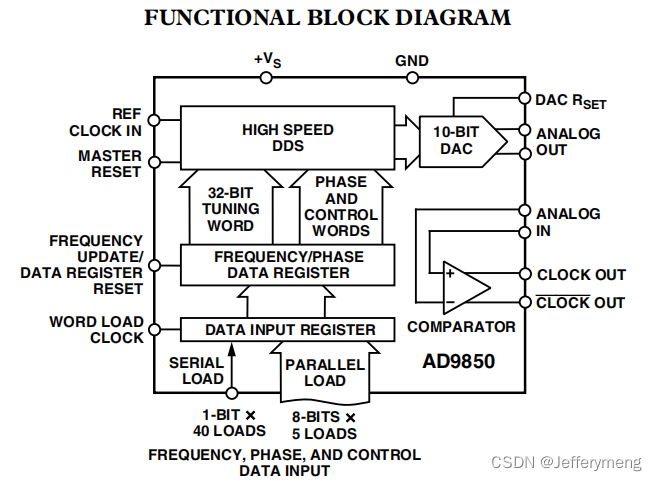

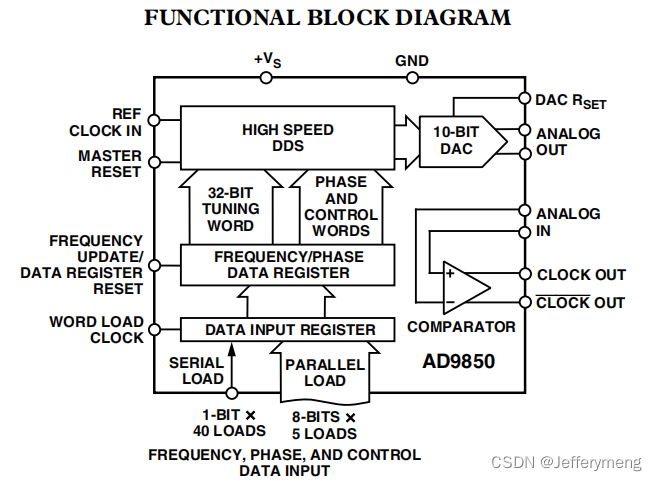

一般的DDS芯片都是由相位累加器 、相位幅度转换 、后端DAC组成:

要合成一个正弦波,即产生一个正弦波的数字码作用于dac,可以通过幅值信息直接合成,但是正弦波的幅度不是线性的,在每次转换过程中转变的损耗比较大。但正弦波的相位可以认为是线性变化的。我们将360度分为2的N次方,通过相位累加器,可以将频率控制字作为累加单元进行频率的控制(每隔多久进行一次相位累加)。然后再通过预先就存好的相位—幅度表,获取对应dac的输入码值,从而完成正弦信号的产生。

因此,通过对相位累加器的设计,就可以很容易的完成不同相位、频率信号的输出。

而幅度的控制,则必须改变相位-幅度码表中的数据才能进行。而在我们实际使用的芯片中,这个码表是已经在芯片的掩膜里就制造好了,不能进行修改。(有其他方案,后面再具体说明)

3.电流输出DDS

这里必须提到的是很多DDS或是DAC都是电流输出的,或者说性能要求较高的DAC芯片或是dds中集成的输出端dac都是电流输出的。

实际上,市面上的高速、高精度的DAC并不是给我们用来做信号发生的,而是工业上用于精密控制的芯片,具有更大的驱动能力。并且电流输出的dds还可以根据用户的电压幅度需要,在引脚上引入不同电阻,方便了芯片的使用。

但实际上电流输出类型的dds芯片,在电赛中用于作信号发生源是有很多不便之处的。我们主要考虑到最大电流通常在1mA—10mA数量级,耐压范围基本也都在0.5V左右,这个电压范围对我们来说通常太小了,所以后级需要一个运放来获得更大一些的电压。在这个放大的设计过程中会遇到很多的问题,也在后面具体阐述。

二、FPGA+DAC方案

FPGA的特点就是高速、并行。这就使得它非常适合与高速实时采样的并行DAC配合使用。

我们通过FPGA直接写出波形数字表,通过DAC的转换,直接获得模拟的输出。只要有表,任何波形、任何频率、任何幅度的信号都可以被输出为模拟,这是非常方便而且使用的,具体的实现在我前面的博客里面已经写过了。

https://blog.csdn.net/Jefferymeng/article/details/123655576?spm=1001.2014.3001.5501

1.芯片调试记录:AD9708

频率:AD9708的采样时钟的频率最大也是125MHz,但输出稳定时间所限制的最大频率是28MHz,而fpga通过pll的ipcore可以很轻松的输出几十M量级的时钟信号,可以很好的与之配合。

量化精度:AD9708的量化精度为8位,对于DAC来说,256的量化位数已经足够大了,对于输出的阶梯,可以很容易通过低通滤波器消除。

供电:AD9708的供电电压为3V到5V,并且功率最大为175mW,在3.3V供电下的电流为50mA左右,是可以直接用单片机的3.3V引脚进行供电的。

输出方式:该DAC采用的是差分电流输出(基本所有的高性能dac都是这种)。因此,可以在后级用一个运放将差分信号放大为无偏置的电压信号。

2.备注

但是,fpga能否使用在电赛中却是一个未知,近年来电赛的趋势是:数字化,以及开发板限制。很多赛题开篇明义的要求是使用特定公司、特定类型的开发板(TI、瑞萨),而不能使用stm32、fpga等等作为主控芯片。

而来到一般的单片机主控,由于一定需要通过中断来写DAC并行数据,并行、实时采样的DAC能够输出波形地 频率限制将很明显,例如TM4,在80MHz主频下,设计正弦周期被为64个点(已经很小了),不写中断而是直接while循环能够达到的最大频率也只有80M/(64*4)=312.5kHz(考虑一次写操作需要4个时钟周期),实际上能够达到的频率将会更小。因此我们必须考虑串行的、有寄存器的、非实时的dds芯片。

三、MCU+DDS方案

前面提到了我们必须使用dds芯片的初衷,在fpga使用收到限制的前提下,通过mcu的串行同行完成信号的发生。

我们必须明确我们产生的信号的需求是怎样的。信号频率可调并且足够宽,信号幅度可调,可以产生不同相位的信号(如反相),不仅可以生成正弦波,还可以产生其他波形(方波、三角波、脉冲波)。(我在这里主要考虑的是电路特性测量类型题目中的扫频功能,还有其他场景比如调制波的生成)

0.几种常用DDS芯片汇总

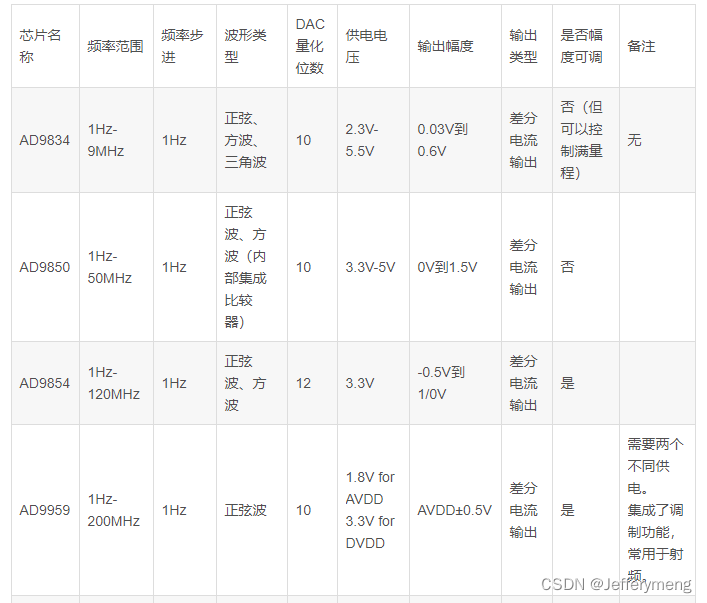

下面是我使用过的ADI公司的一些高性能DDS芯片的特性表,仅供参考:

1.芯片调试记录:AD9834

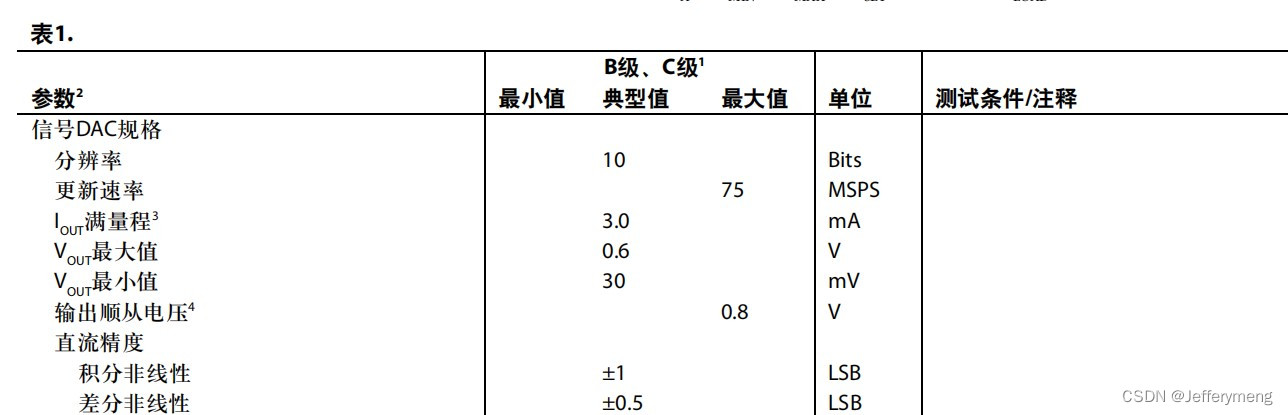

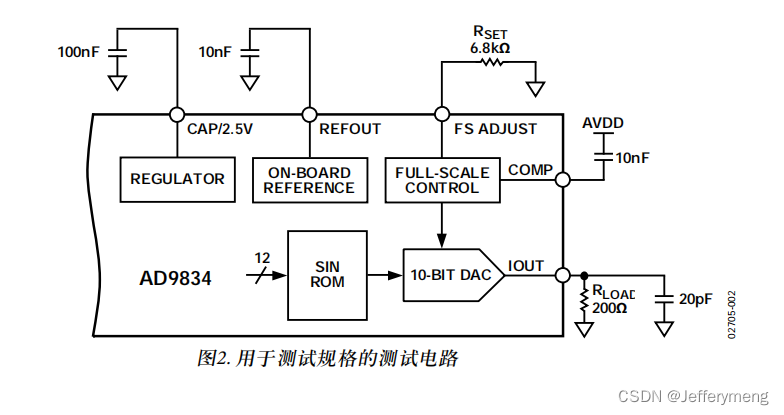

相较于其他芯片,AD9834具有正弦、方波、三角波三种信号发生的类型,正弦波和三角波是可以通过修改寄存器值来输出的,(修改寄存器数值以达到旁路sin rom输出三角波的效果)并且是差分电流输出,电流输出的满量程是3mA,电流的非线性误差在1个LSB以内。

而方波是通过AD9834内置了的比较器实现的。这个比较器整个都集成在了芯片内部,因此输出方波的占空比总是50%。(方波也是差分电流输出的)

AD9834虽然没有程控的调幅功能,但是可以通过改变满量程电流,控制输出幅值,这种方案的可行性有待考察,因为满量程的控制是电流控制,需要从FS ADJUST引脚灌入一个电流来确定满量程电流。如果要程控这个电流,有两个路径:

1是用MCU控制数字电位器,从而控制电流

2是用MCU内置dac来控制电压,从而控制电流

很明显,由于一般的数字电位器精度都很低,而且阻值一般都是10k欧姆以上的量级,因此第一种的可行性较低,第二种的可行性较高,但还需考虑单片机引脚是否可以流出足够大的电流。

2.芯片调试记录:AD9850

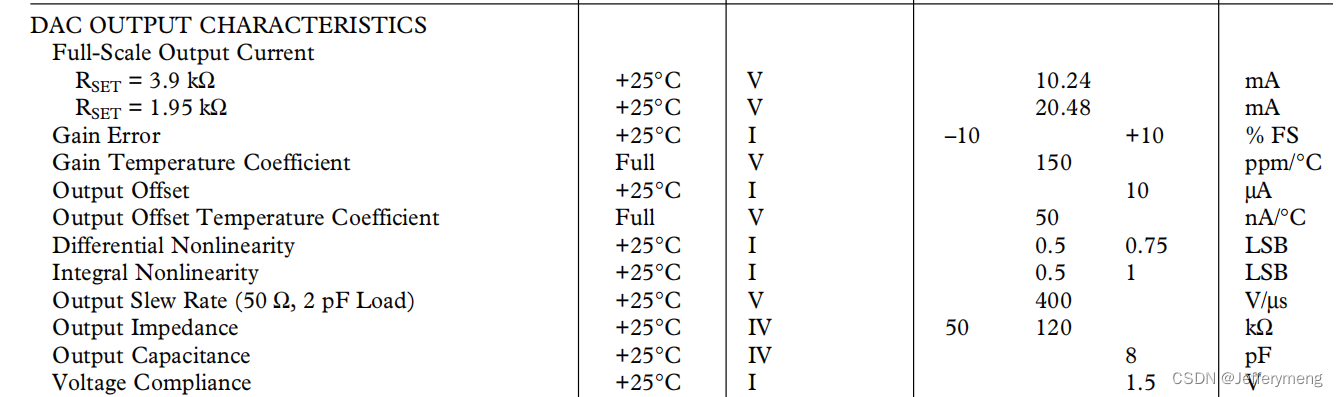

AD9850和AD9834相比,不能输出三角波,但频率更高,达到了50MHz。DAC量化位数还是10位,对DAC来说已经是一个很高的数值了。

这个芯片的比较器没有将电压基准进行集成,因此我们可以在片外的比较器引脚加上电阻网络,从而调节方波的占空比。

同时,相较于其他dds,9850的输出电压范围更大,达到了1.5V,输出电流也可以达到20mA以上。

但是,9850不具有调幅的功能,必须通过后级的运放电路进行幅度控制和放大。

3.芯片调试记录:AD9959

AD9959其实是一款专用于射频领域的dds,输出频率高达200MHz,只能够发生正弦波,量化精度是10位,输出幅度为±500mV。

但是,这个芯片在低频时的工作不是很理想。这是因为,我们总需要提供一个1.8V的AVDD电压,并且这个电压必须经过严格的滤波。输出的差分信号是有1.8V的偏置的,要滤除这个偏置,则必须加上一个电容隔直,从而构成低通。同时,由于9959的输出安全电压只有正负0.5V,电流为最大10mA恒定,因此输出端的电阻一定为50欧姆或者更小,太大了有可能损坏芯片。这样就会在输出端构成高通,是的低频信号无法正常产生。这需要对电容容值继续准确的确定,但一旦容值变大,又会导致高频时候信号的衰减。因此,这个芯片确实是不适合工作在低频下的。

4.调幅方案总结

①满量程调节:芯片的输出满量程可以受引脚电流控制,例如AD9834。这时可以通过单片机dac输出程控电压,或者单片机控制一个数字电位器控制该满量程电流。dds一直保持满量程输出,而程序是通过控制满量程电流达到幅度调节的效果。

②可调幅dds:AD9854、AD9959等芯片内置了幅度调制的功能,通过写寄存器就可以实现幅度调节的功能。

③后级程控增益放大器:在dds后级设计一个程控增益放大器,达到幅度调节的功能。这部分也有多问题需要解决,也有很多不同的方案,比如差分电流放大器,程控的数字电位器构成运放负反馈放大电路、压控增益放大器(AD603、VCA821)。需要注意的问题也有很多,比如电流输出和电压输出进行放大的异同、差分信号的放大方案、以及直流偏置的消除、后级隔直和放大器带宽的影响。

虽然这些方法都已经有了成熟的方案,但是在不同应用场景的差异比较大,需要具体问题具体分析,放在以后再进行总结。

总结

本文主要是围绕数字信号发生方案继续了系统的介绍,着重于泛泛而谈,主要是提供了对ADC、DDS芯片选型的指南,以及幅度可调dds的方案的总结,仅供参考。

上面提到的几款芯片的stm32、TM4的驱动程序,以及相应的驱动电路都已经完成了(一些是在tb上直接购买的模块),如有需要也可以私信我。

这篇文章是我依照电赛备赛期间的经验来写的,主要是回顾了一下dac的基本原理(模集专业课上学的),以及总结一些(惨痛的)经验和教训,行文和用词都非常不专业以及不严谨,欢迎批评指正,感谢阅读!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)