同步时钟、异步时钟----概念解析

目录同步时钟异步时钟时钟约束分组相位同步、频率同步相位同步频率同步同相位时钟、同源时钟、同时钟域时钟和异步时钟同相位时钟同源时钟同时钟域时钟同步时钟当两个时钟间的相位是固定关系的,则可以称这两个时钟为同步时钟(synchronous clock)。一般同源,如由同一个MMCM or PLL产生的两个时钟可以称为同步时钟。因此可以将主时钟和与之对应的衍生时钟约束成同一个时钟组。异步时钟无法判定两个时

目录

同步时钟

当两个时钟间的相位是固定关系的,则可以称这两个时钟为同步时钟(synchronous clock)。一般同源,如由同一个MMCM or PLL产生的两个时钟可以称为同步时钟。因此可以将主时钟和与之对应的衍生时钟约束成同一个时钟组。

异步时钟

无法判定两个时钟间相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)。两个来自不同晶振的时钟,一定是异步时钟。通常情况下设计中不同的主时钟肯定是异步时钟,因此可以将这两个主时钟及其衍生时钟约束成不同的时钟组

时钟约束分组

两个有分频关系的同源时钟 可以认为是同步时钟域,也可以认为是异步时钟域 认为是异步时钟域之后放在不同的clk group,clk domian之间需要异步处理,但不需要分析静态时序;

如果作为同步时钟域,可以做异步处理也可以不做异步处理,做异步处理之后相应的时序路径设为falsePath可以不去分析sta。不做异步需要下SDC并由后端保证时序(调相位,设multicycle等)。之所以能作为同步时钟域是因为无论整数分频还是分数分频,同源时钟的相位都是固定的在时序处理时就可以固定调相位。

异步时钟只能划分到不同的group,异步时钟域之间的信号不做静态时序分析

相位同步、频率同步

相位同步

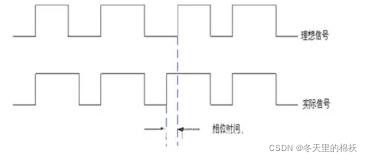

相位时间(Phase Time)指时钟信号与理想信号在对应的有效瞬间(一般指上升沿或者下降沿)的延迟时间,简称为“相位”。相位即时延。

相位同步又称为时间同步(时间延迟同步),指时钟信号的有效沿(上升沿或者下降沿)同步。

如图所示,信号A和B是相位同步,信号C和A、B不是相位同步。

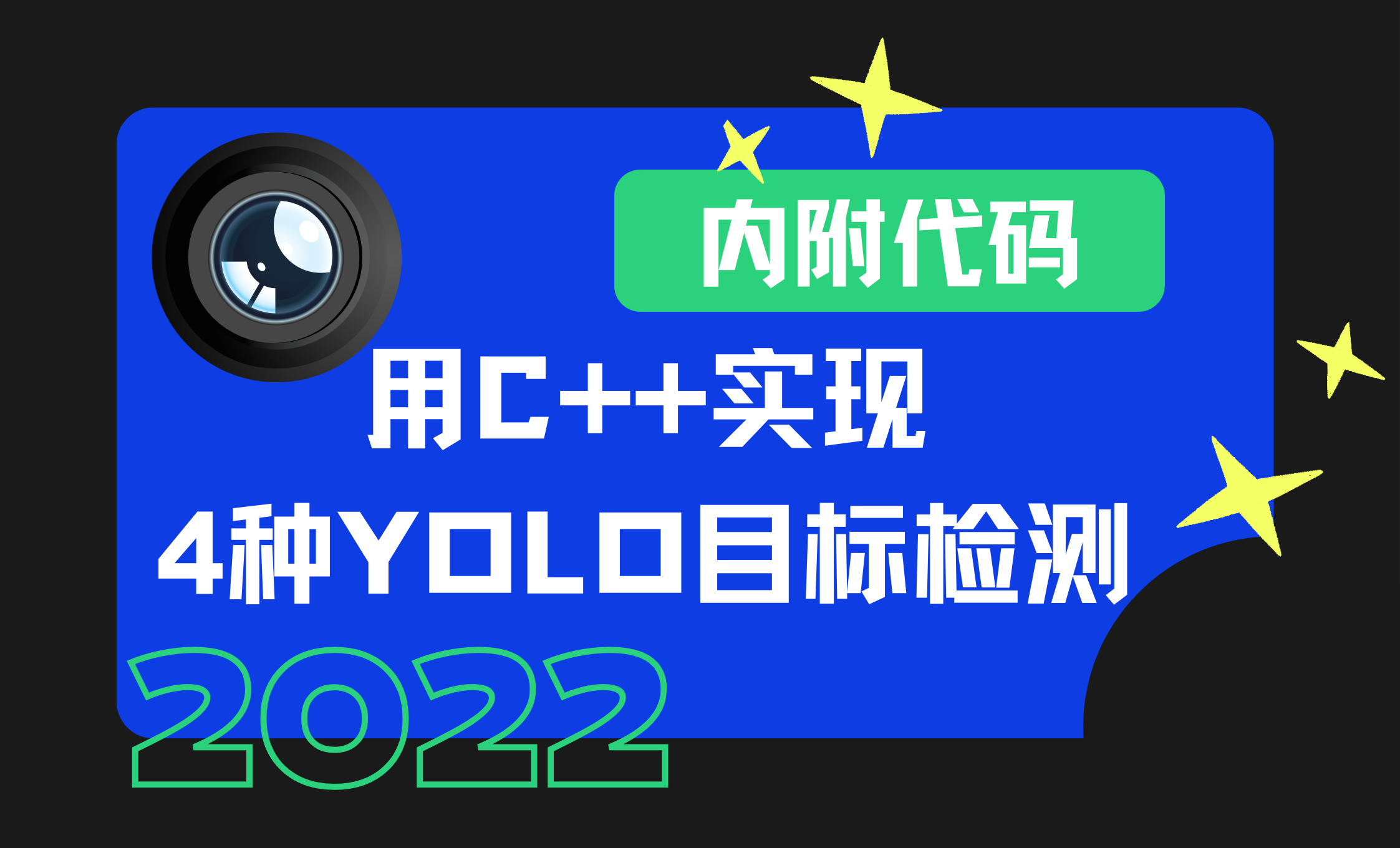

频率同步

频率同步指两个信号的变化频率相同或者保持固定的比例。信号的相位可以不一致,频率也可以不一致。如图所示,信号A、B和C是频率同步。

时间同步和频率同步区别:

如图所示的Watch A与Watch B,如果二者每时每刻的时间都保持一致,这种状态叫时间同步(Phase synchronization)。如果二者的时间不一样,但保持一个恒定的差值(如,6小时),那么这种状态称为频率同步(Frequency synchronization)。

http://blog.sina.com.cn/s/blog_5465ea2e0102xghg.html

同相位时钟、同源时钟、同时钟域时钟和异步时钟

同相位时钟

同相位时钟:即相位相同,也就是说时钟的有效沿必须同步。(有效沿为上升沿或者下降沿)。

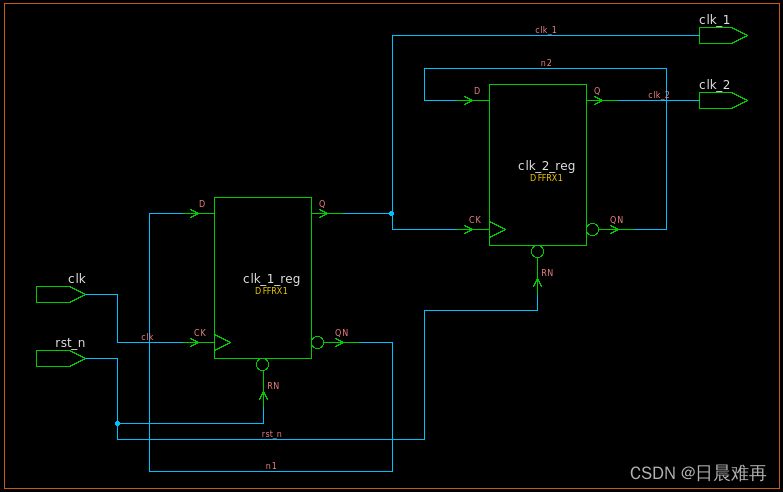

以上升沿为有效沿,则clk0为慢时钟,clk1为快时钟,clk0的时钟沿始终与clk1的时钟沿对齐,两个时钟相位相同。

同源时钟

同源时钟,通常由一个PLL或者DLL产生,相位不需要相同,只要求相位固定。同源时钟一般可以称为同步时钟。

同源时钟即时钟产生的源头相同,同源时钟在传输过程中通过的组合逻辑电路如果不相同,则两个同源时钟的有效沿的延迟也就不同,但是却是固定的,也就是相位是固定的。

同时钟域时钟

同时钟域的时钟既是同源时钟,还要求相位相同并且频率相同,通常是同一个PLL产生的频率相同相位相同的时钟,PLL能够保证两个时钟在不同的情况下(如温度不同)的偏差在精度范围内。从波形上看,同时钟域两个时钟频率一样,跳变沿完全对称。但是从波形上看两个时钟频率一样,跳变沿完全对称的不一定是同时钟域时钟,如两个PLL输出的看似相同的时钟不是同一个时钟域的,例如在不同的温度下,就不能保证两个时钟的偏差。

参考链接

https://blog.csdn.net/kongbeiruhai/article/details/109337177

https://blog.csdn.net/cy413026/article/details/102660331

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)