ZYNQ学习--DDSIP核

Vivado DDS; DDS(Direct Digital Synthesis,直接数字频率合成),作为信号发生器使用,在Quartus中也叫NCO(Numerically Controlled Oscillator,数字控制振荡器),是软件无线电中的重要组成部分。

DDS Compiler(6.0)

参考资料:

可搜索Vivado DDS Compiler(6.0)模块使用

Vivado 的DDS Compiler(6.0)IP核参考手册

注:创建工程省略

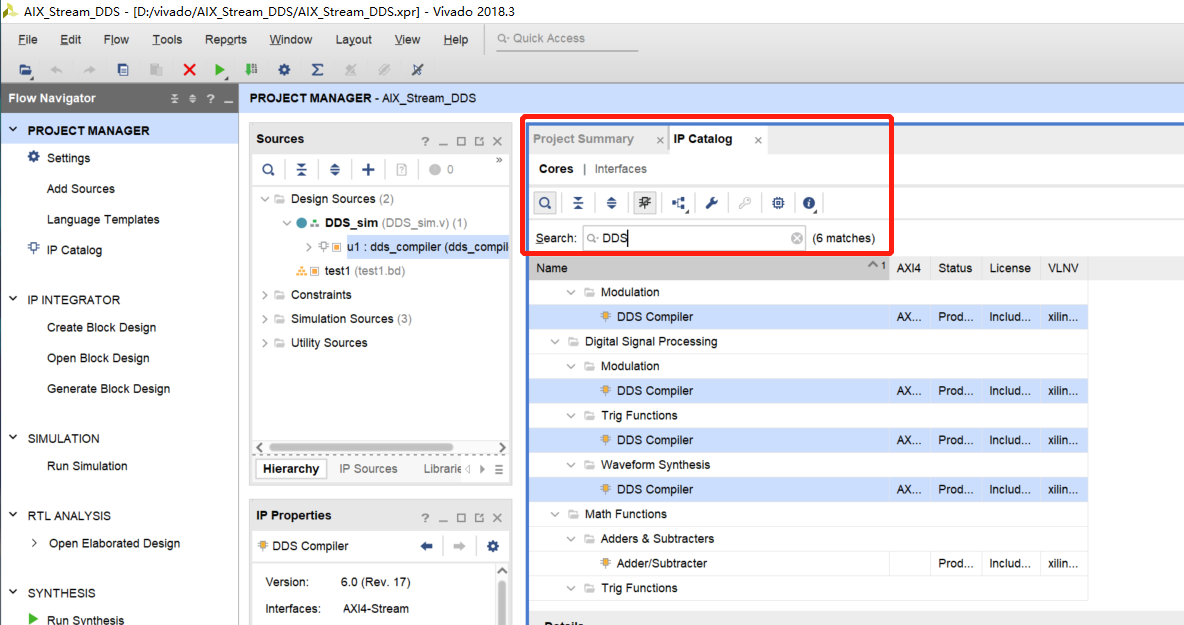

IP核调用

在IP Catalog 中搜索DDS

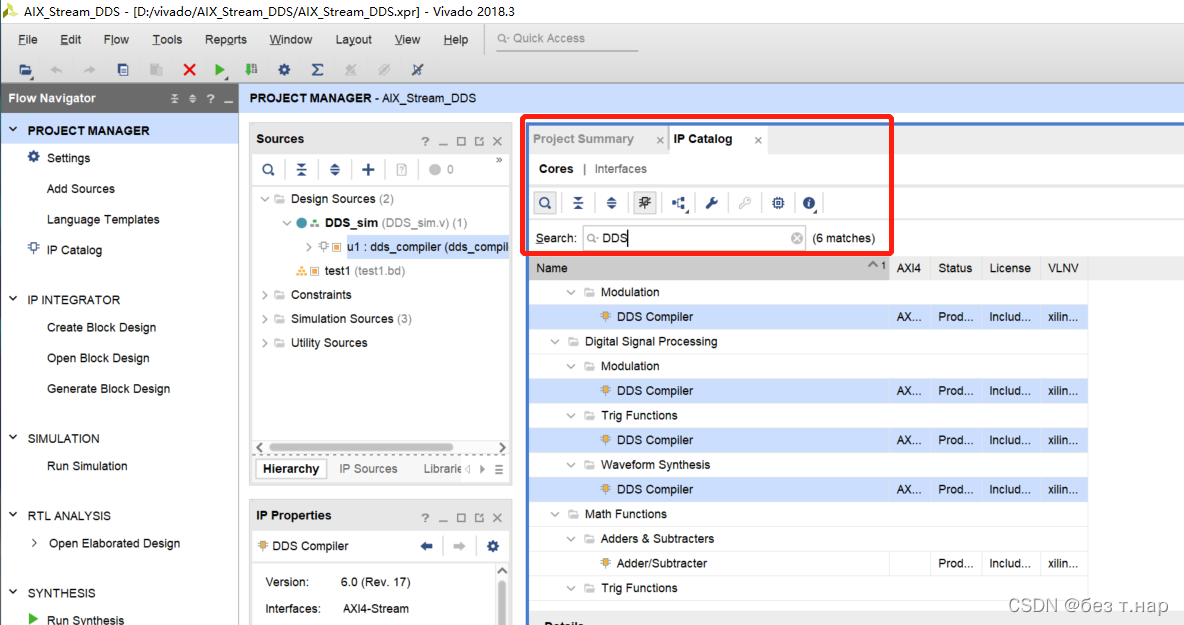

参数设置界面

一、基础设置

1、模式选择–(1)相位和波形数据 (2)相位数据 (3)波形数据

2、系统时钟设置

3、设置通道数

4、模式选择,两种模式的区别在于参数计算的方式不同

5、选择在System Parameters下进行参数设置

6、输出数据宽度和频率精度

SFDR 决定了输出的数据位宽。

二、运行设置

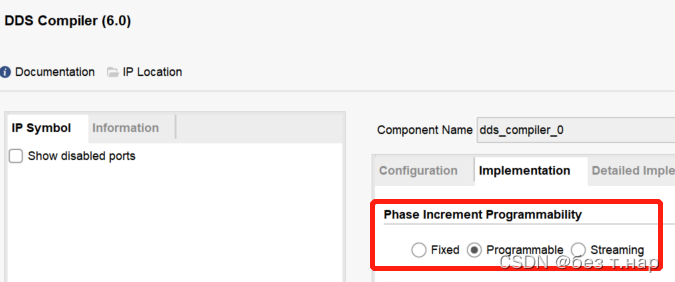

A、相位的增量(PINC)和偏移(POFF)

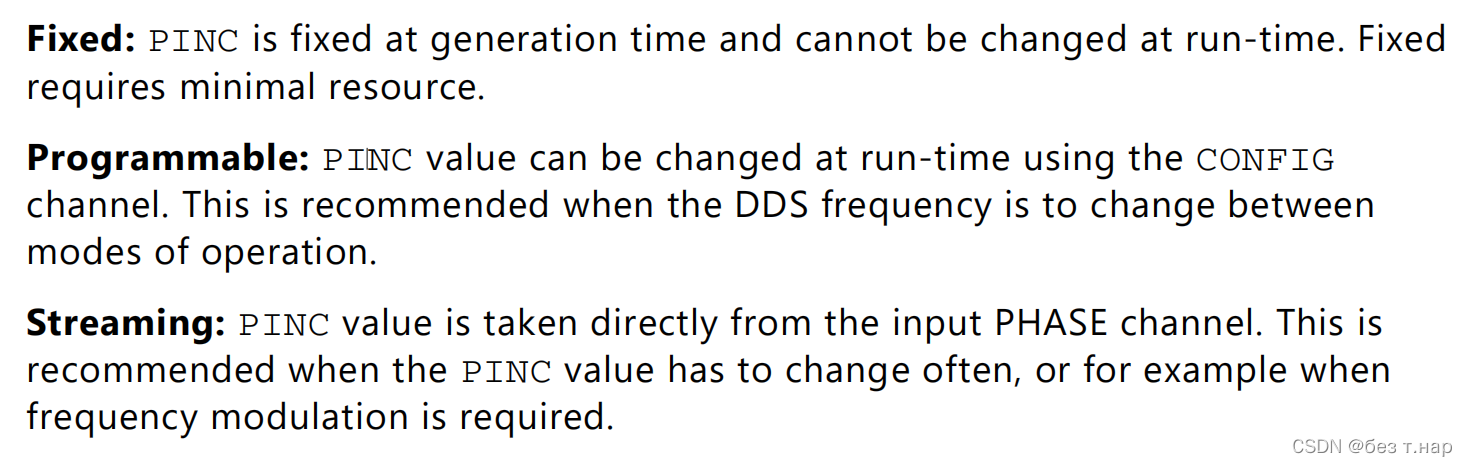

两个参数都是这几个选项:手册中解释都是相同的

Fixed(固定模式):运行前确定,运行中不可更改,占用资源最少

Programmable(编程模式): 运行时可修改,DDS频率在不同模式下进行切换

Streaming(流模式):参数取决于输入的相位值,适用于DDS频率频繁变动的模式

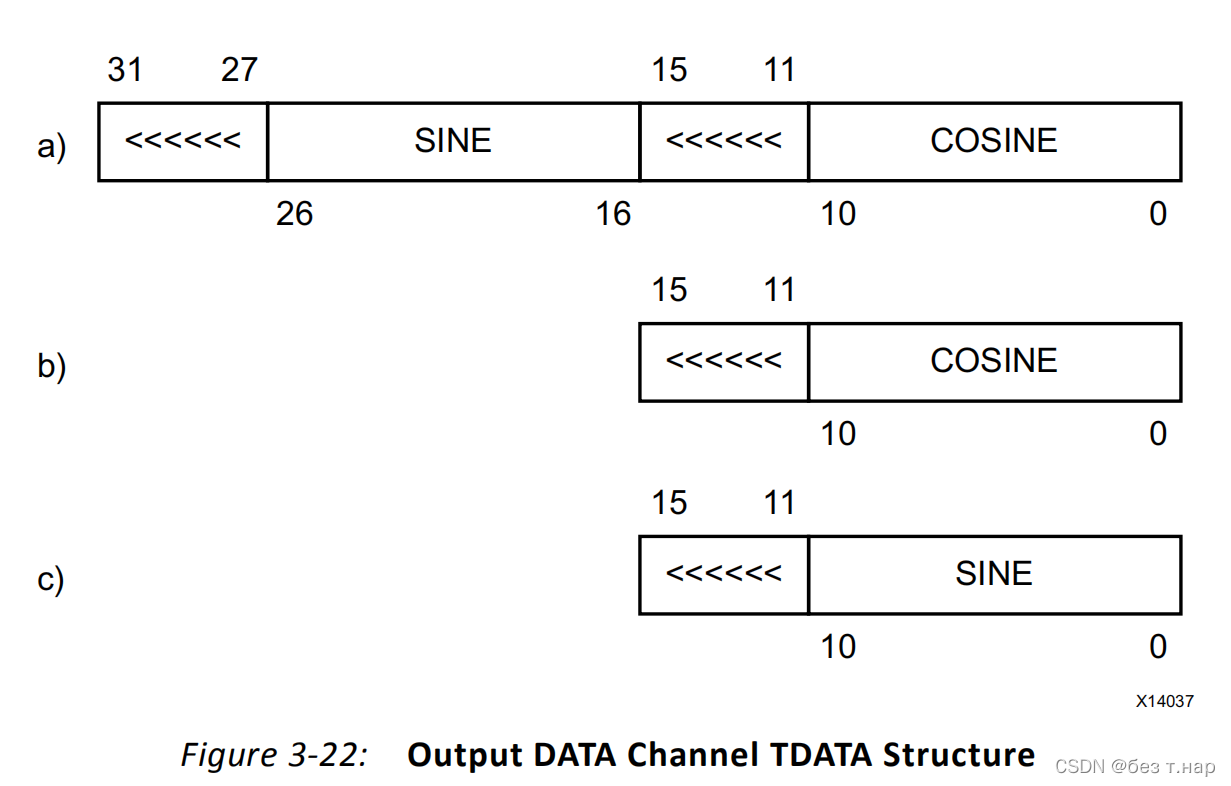

B、输出格式设置

output selection 中几个不同模式的输出时序

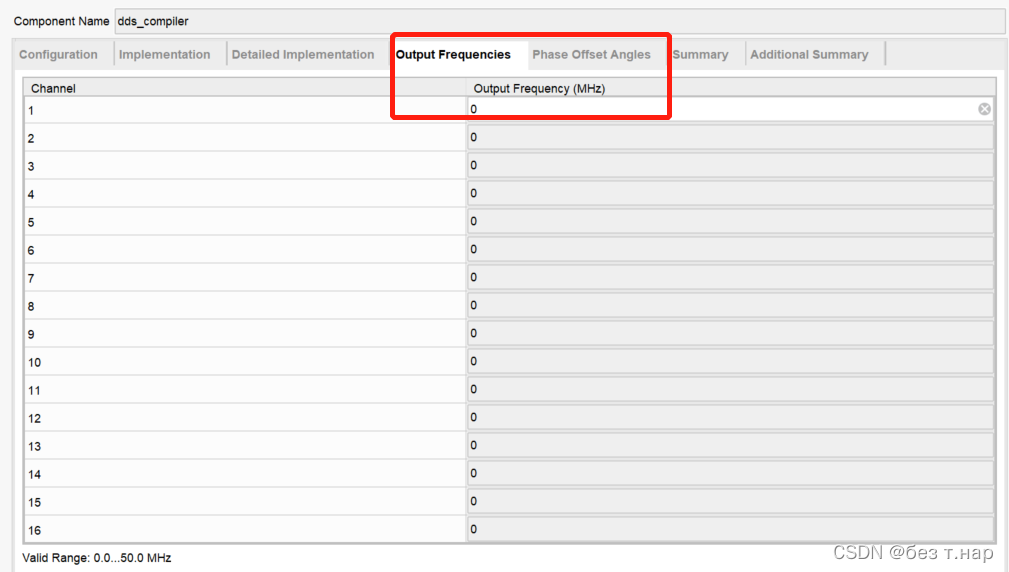

三、通道的频率和相位偏移设置

设置想要得到的正余弦频率

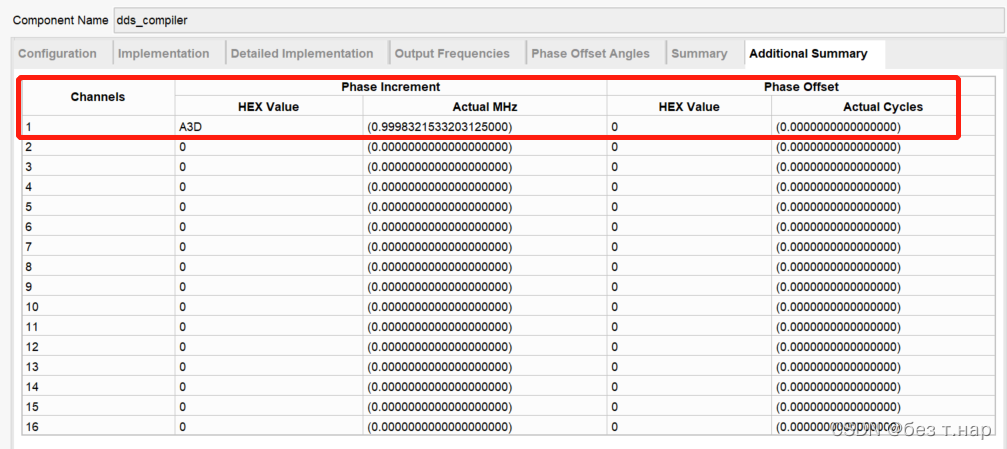

四、设置汇总及补充

在这里可以核对设置的参数是否为预期设置,便于检查

汇总补充实际的输出频率

五、 编写Testbeach进行仿真

设置时钟+实例化即可

注:

即,不能以 TestBench中的 reg 型赋值给被测模块作为输出的 wire 型;

同,不能以 TestBench中的 reg 型赋值给被测模块作为输出的 reg 型;

只能以TestBench中的 wire 型赋值给被测模块作为输出的 wire 型,

对于输入来说用 reg 可行。

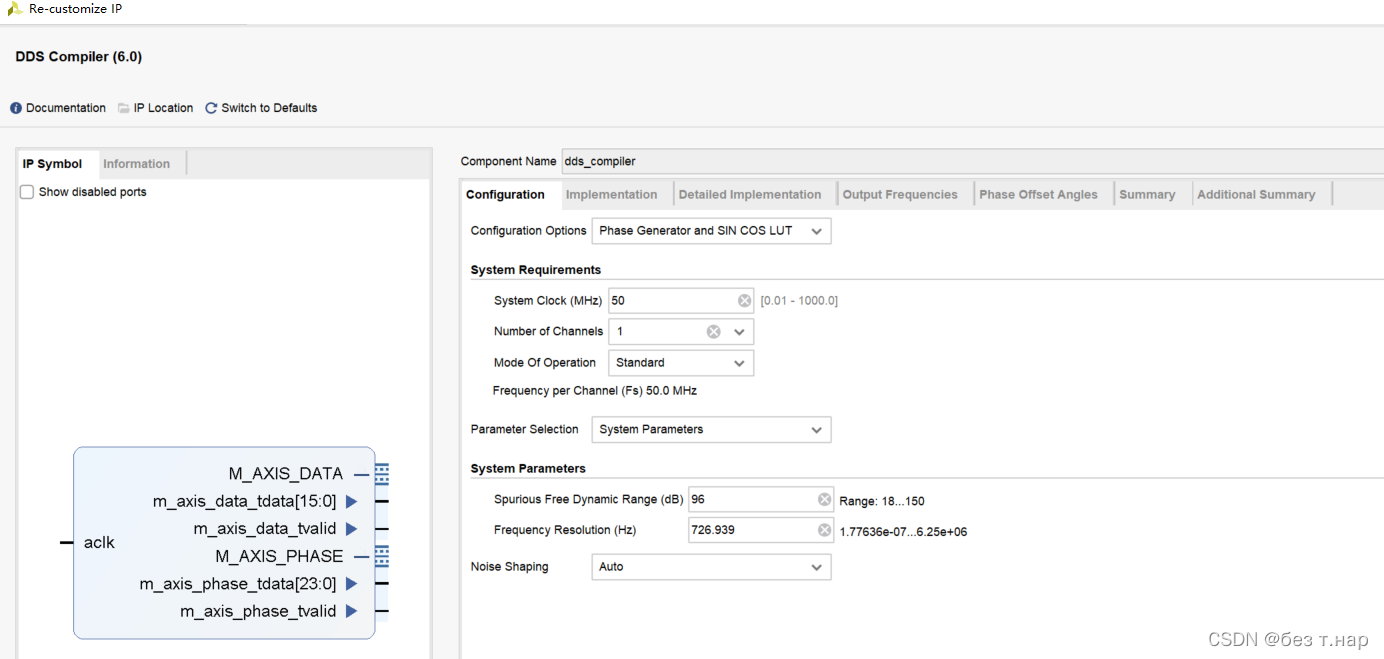

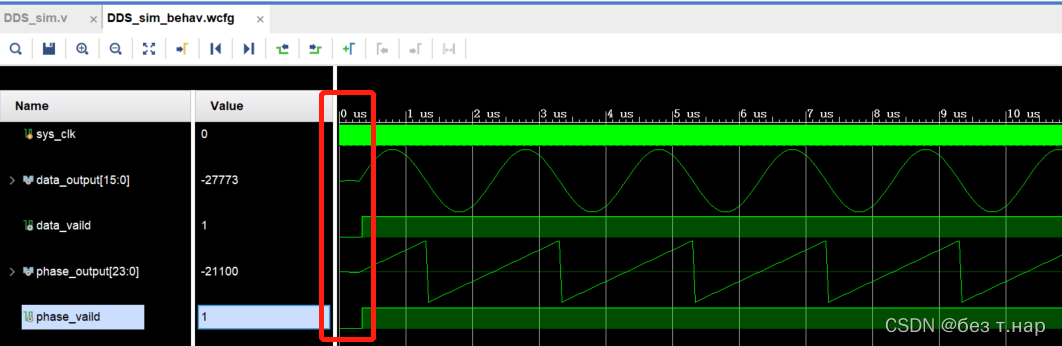

module DDS_sim;

reg sys_clk;

wire [15:0]data_output;

wire data_vaild;

wire [23:0]phase_output;

wire phase_vaild;

dds_compiler u1

(

.aclk(sys_clk),

.m_axis_data_tvalid(data_vaild),

.m_axis_data_tdata(data_output),

.m_axis_phase_tvalid(phase_vaild),

.m_axis_phase_tdata(phase_output)

);

initial

begin

sys_clk=0;

end

always #20 sys_clk=~sys_clk;

endmodule

AXI4-Stream的接口规范下,只有时钟和Vaild同时有效时才能成功输出数据

DDS IP 数字波形合成

首先得了解DDS IP核是参数设置,增加相位增量(频率字)

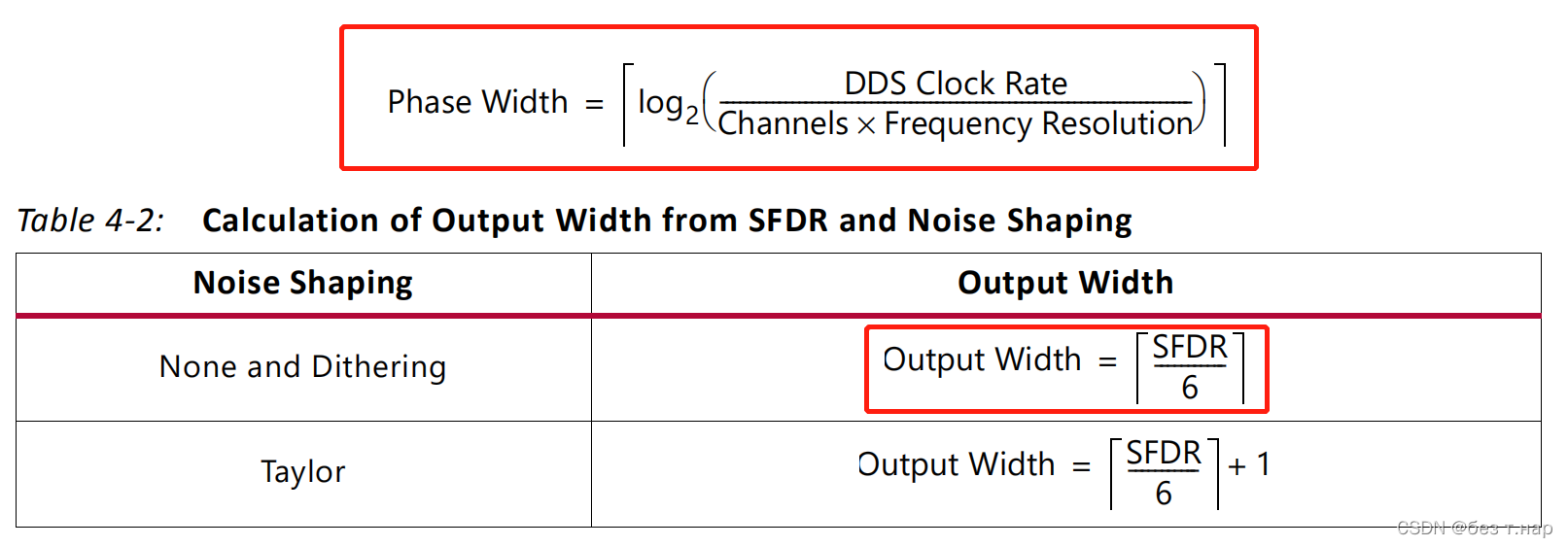

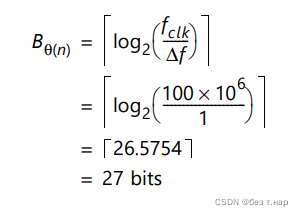

频率字的位宽计算,Δf 自己根据需求填写,再根据fCLK即可算出相位增量的位宽

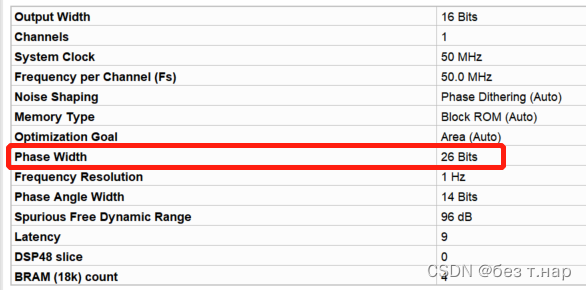

设计中fCLK=50MHz Δf=1,所以频率字位宽为26bit

标准模式下的输出频率计算Δθ即为频率字

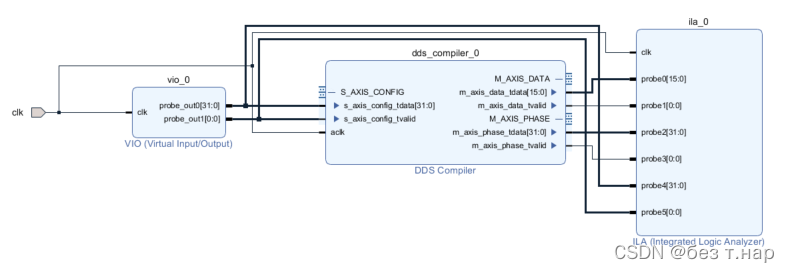

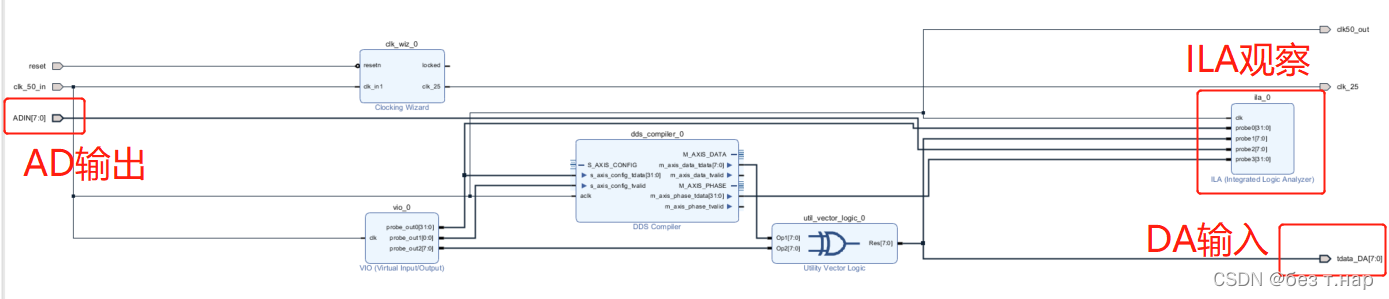

使用 Vivado的IPI工具,例化DDS IP,DDS需要能够配置频率字(相位增量)

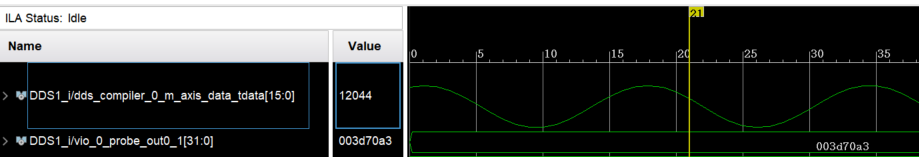

DDS工作时钟使用PL的板载50MHz时钟,使用ILA工具观察波形, 使用VIO设定频率字

设计Block Design

在最后加ILA观察每一路信号,下图为实际观察结果

3MHz频率输出 频率字(26位)=0X 003D_70A3

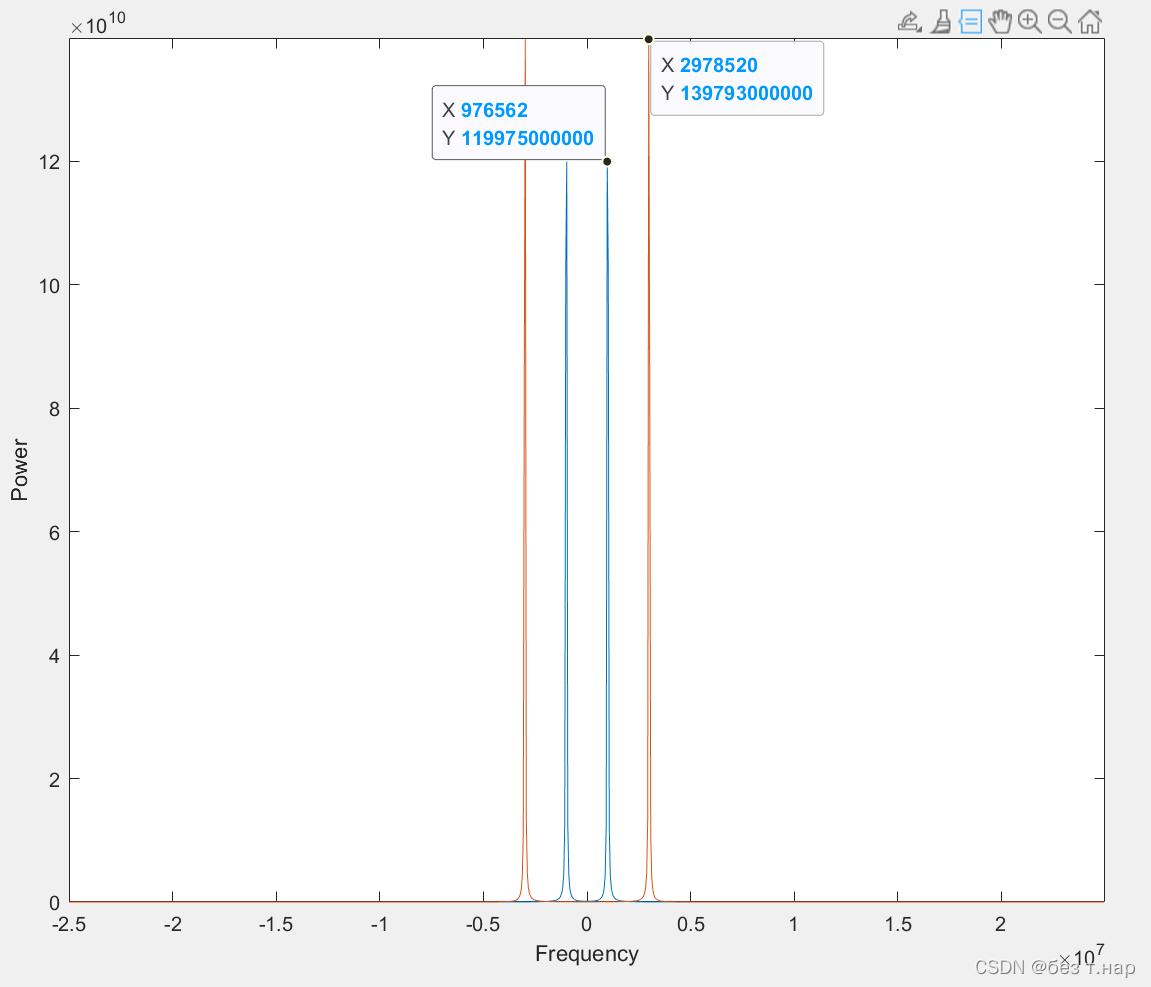

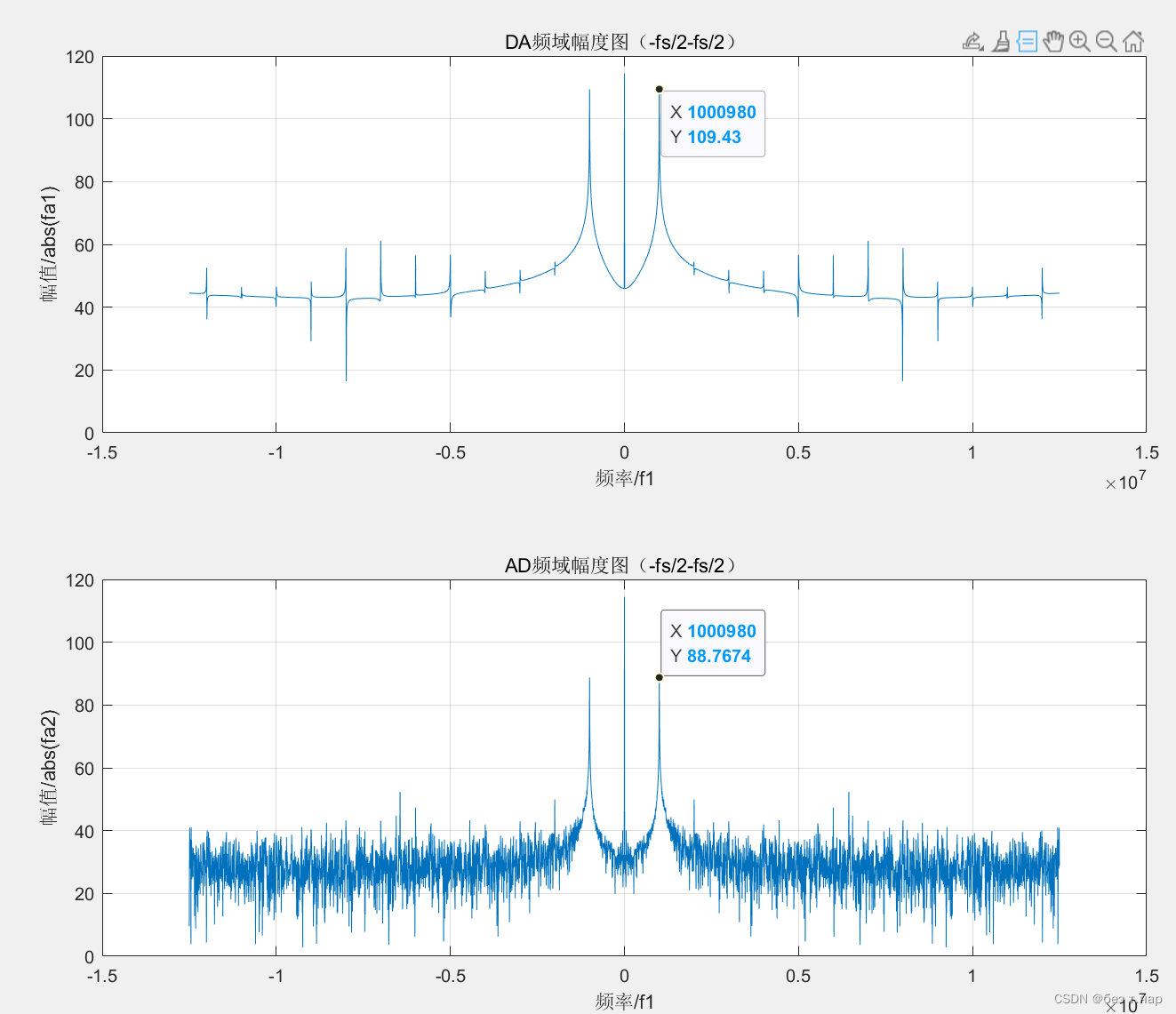

将输出数据导出在matlab中生成频谱1MHz、3MHz

蓝色线为1MHz,红色线为3MHz。

误差可能是导入matlab转化数据格式时数据进位或者省和数字化过程中产生的

DDS IP & ADDA使用

基于“DDS IP 数字波形合成DAC ” 实验方案,使用50MHz时钟频率,使用DAC输出正弦波。把DAC输出模拟信号自环给ADC的输入

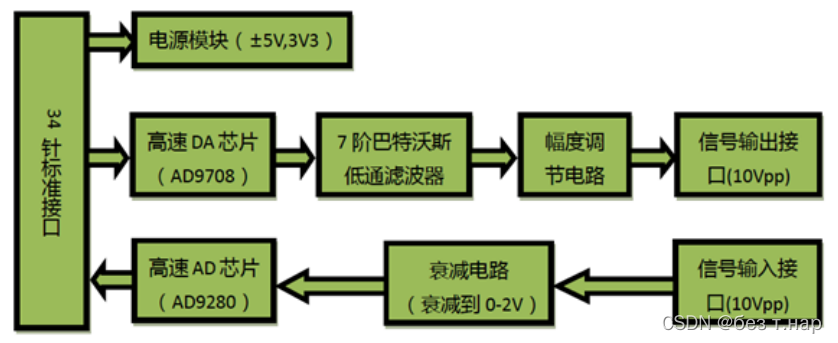

一、ADDA模块

使用的黑金配套的高速 AD/DA 模块 AN108

功能结构图

DA芯片AD9708 是 8位,125MSPS的 DA 转换芯片

AN108板载幅度调节,使用的是 5K 的电位器,最终的输出范围是-5V~5V(10Vpp)

AD芯片AD9280 芯片为8 位,最大采样率 32MSPS

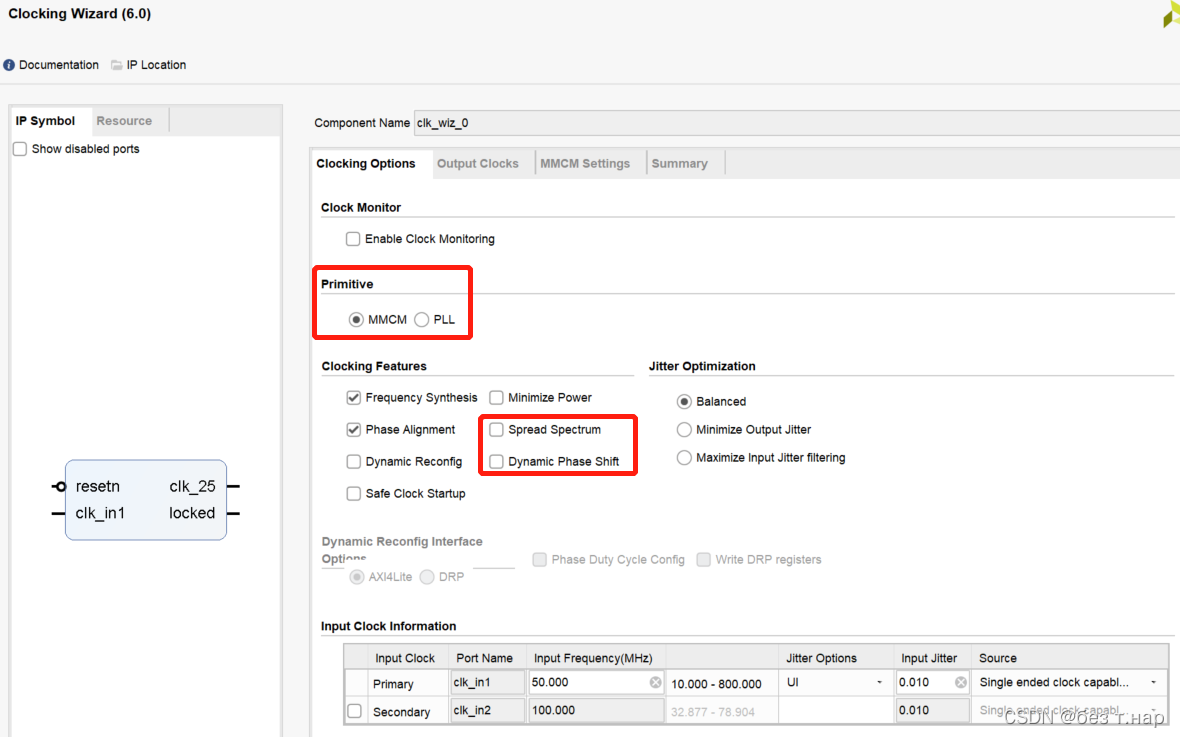

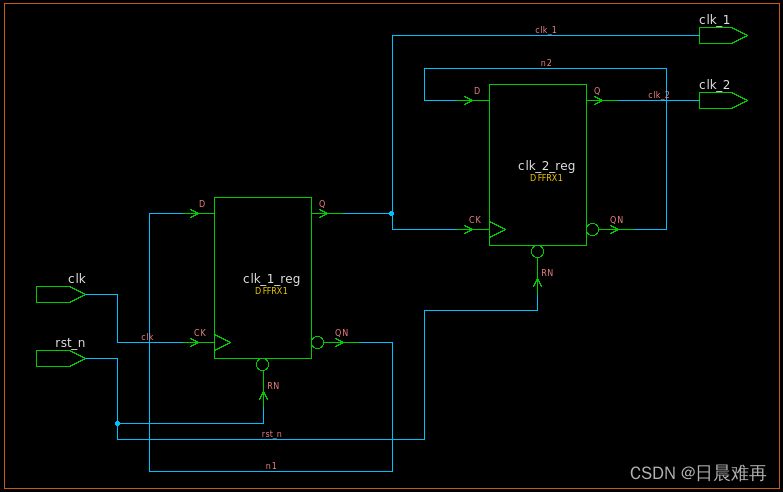

Clocking Wizard (产生时钟) MMCM模式

MMCM是基于PLL的优化,MMCM相对PLL的优势就是相位可动态调整,但PLL占用的面积更小。

二、DDS IP核

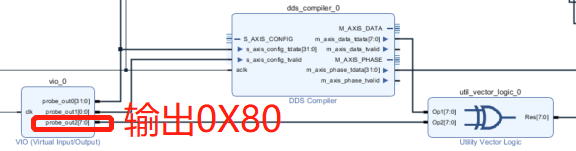

IP核设置基本沿用上一个实验:最终输出为8位,频率字为26位;同样的DDS的频率字使用VIO生成。DDS的输出为有符号数,芯片的输入DAC CODE范围为无符号数0-255,所以DDS数据输出后需要与0X80进行异或,将数据最高位取反(相对于原始数据+128)

三、整体设计

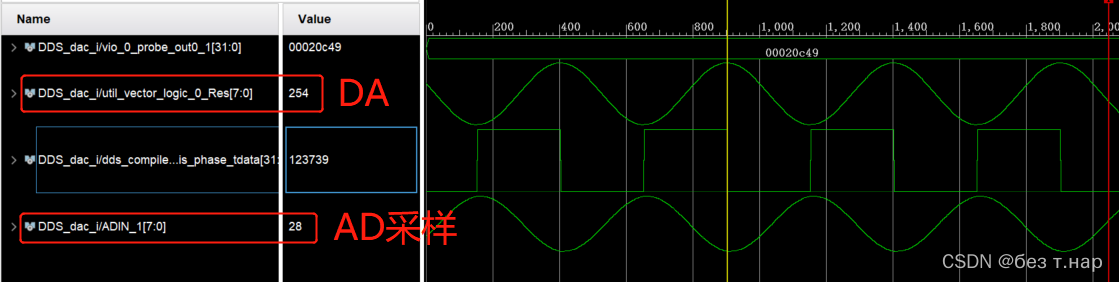

ILA观察信号:频率字、DDS相位、DA输入、AD输出

100kHz的实验–频率低,AD输出较平滑

相位因为数字(32bits)过大显示范围太小而显示不全

matlab频谱图

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)