RISC-V Rocket-Chip环境安装过程和RTL生成总结(基于Ubuntu虚拟机)

基于github上面的rocket-chip setup过程,实际操作过程中有不少问题:https://github.com/chipsalliance/rocket-chiphttps://github.com/chipsalliance/rocket-chip一、环境准备工作RISCV指定使用Ubuntu操作系统环境,因此最好基于Virtualbox或VMware安装虚拟机。除了在我之前写的这

基于github上面的rocket-chip setup过程,实际操作过程中有不少问题:

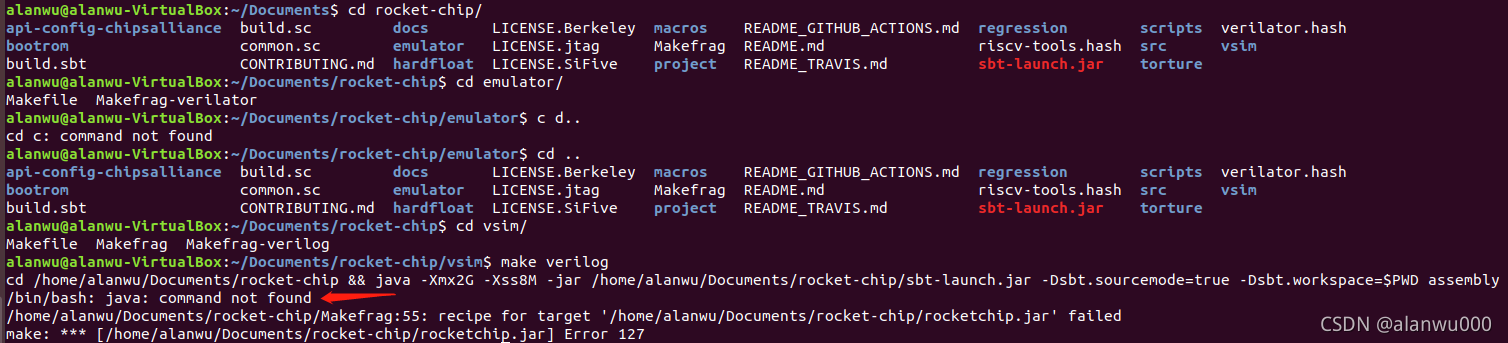

RISCV指定使用Ubuntu操作系统环境,因此最好基于Virtualbox或VMware安装虚拟机。除了在我之前写的这篇文章中的环境准备工作以外,还需要提前安装好java,否则后续命令会报错。另外,如果你需要跑程序,则需要准备好VCS和verdi等EDA工具。

https://blog.csdn.net/heyuming20062007/article/details/120522175?spm=1001.2014.3001.5501https://blog.csdn.net/heyuming20062007/article/details/120522175?spm=1001.2014.3001.5501![]() https://blog.csdn.net/heyuming20062007/article/details/120522175?spm=1001.2014.3001.5501java未安装导致的失败提示:java:command not found

https://blog.csdn.net/heyuming20062007/article/details/120522175?spm=1001.2014.3001.5501java未安装导致的失败提示:java:command not found

安装java,选择第二个即可:sudo apt install openjdk-11-jre-headless

VCS安装过程较为复杂,我会单独写个专栏,也可以参考下别人的做法,怎么安装VCS,这里就跳过了。

二、rocket chip riscv代码同步

同步过程按照GitHub下面的Readme进行,同步完成会多出两个文件夹:rocket-chip和rocket-tools两个文件夹,同步完成后不要忘了使用git submodule update --init注册license和校验文件夹。rocket-chip是主文件夹,编译、运行、生成代码、仿真都在该文件夹下面,有很多文件,生成RTL主要用到vsim文件夹:

rocket-tools文件夹:放了很过工具类的东西,需要指定环境变量到该目录下:

export RISCV=/home/alanwu/Documents/rocket-tools

//指定下几个核工作,笔者虚拟机只分配了一个核

export MAKEFLAGS="$MAKEFLAGS -j1"代码同步使用指令:

git clone https://github.com/ucb-bar/rocket-chip.git

cd rocket-chip

git submodule update --init

git clone https://github.com/freechipsproject/rocket-tools

cd rocket-tools

git submodule update --init --recursive三、RTL代码生成

RTL代码生成前,需要进入rocket-tools文件夹下运行./build.sh命令,会很长时间的联网更新,主要是下载.jar格式的各种java包。

完成后继续安装Ubuntu适配包,又是一段时间的联网更新和安装。

./build.sh

//32位RISCV使用下面脚本

./build-rv32ima.sh

//ubuntu适配包

sudo apt-get install autoconf automake autotools-dev curl libmpc-dev libmpfr-dev libgmp-dev libusb-1.0-0-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev device-tree-compiler pkg-config libexpat-dev

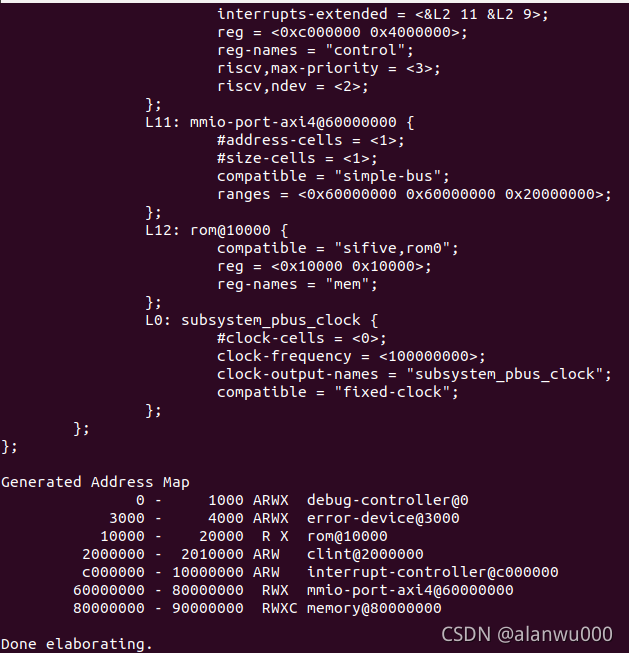

上述过程完成后,进入vsim文件下,使用make verilog生成RTL代码。

cd rocket-chips/vsim

make verilog该命令生成的是默认配置的可综合RISC-V RTL代码,代码生成在vsim/generated-src/文件夹下。最终完成RTL代码的生成工作,当然该部分代码为默认配置代码,后续如果想定制代码需要修改配置,后续有时间再介绍怎么修改配置,生成定制RTL代码。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)