Xilinx中DDS IP的讲解与使用

·

一、DDS概念

DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

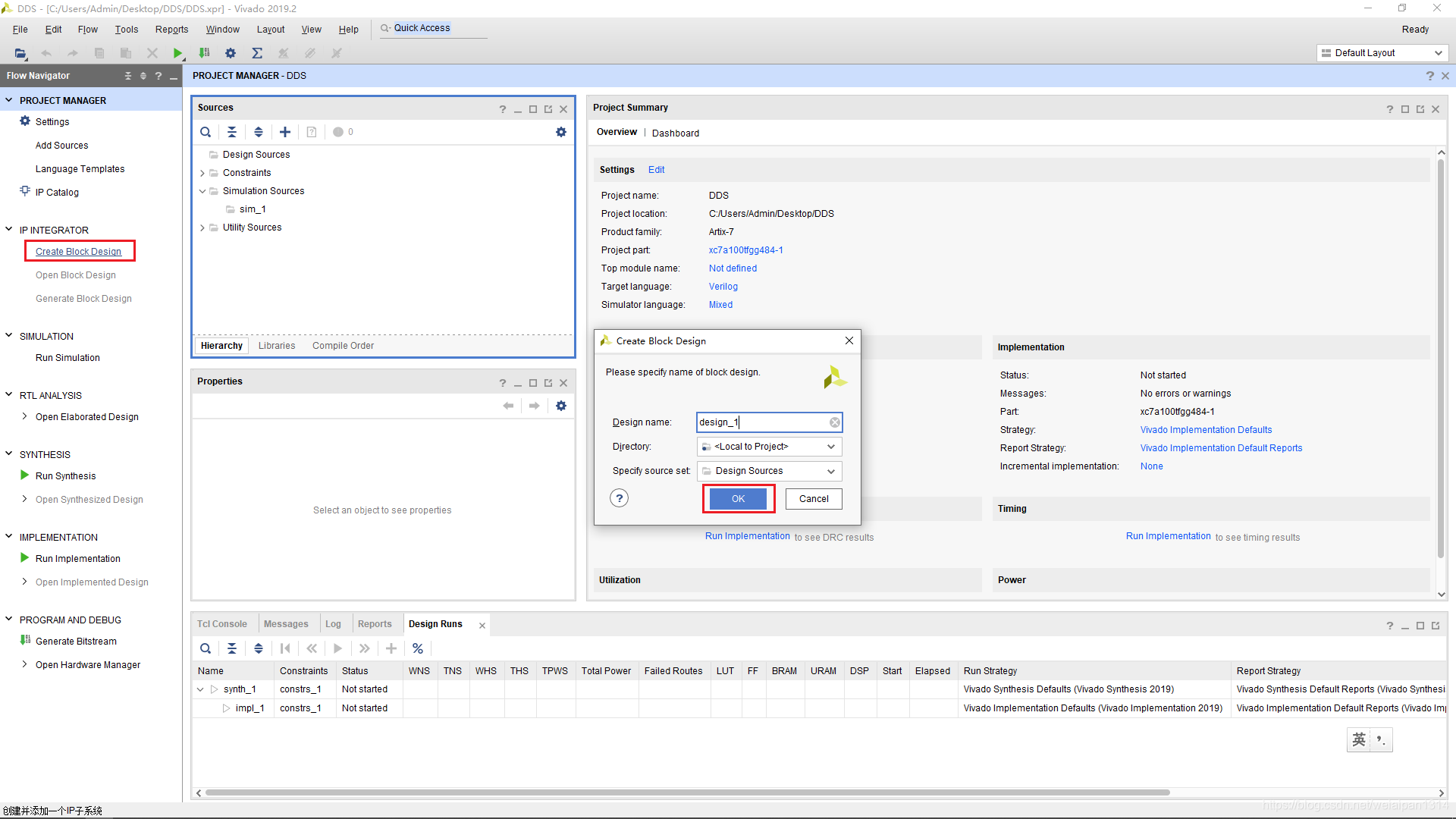

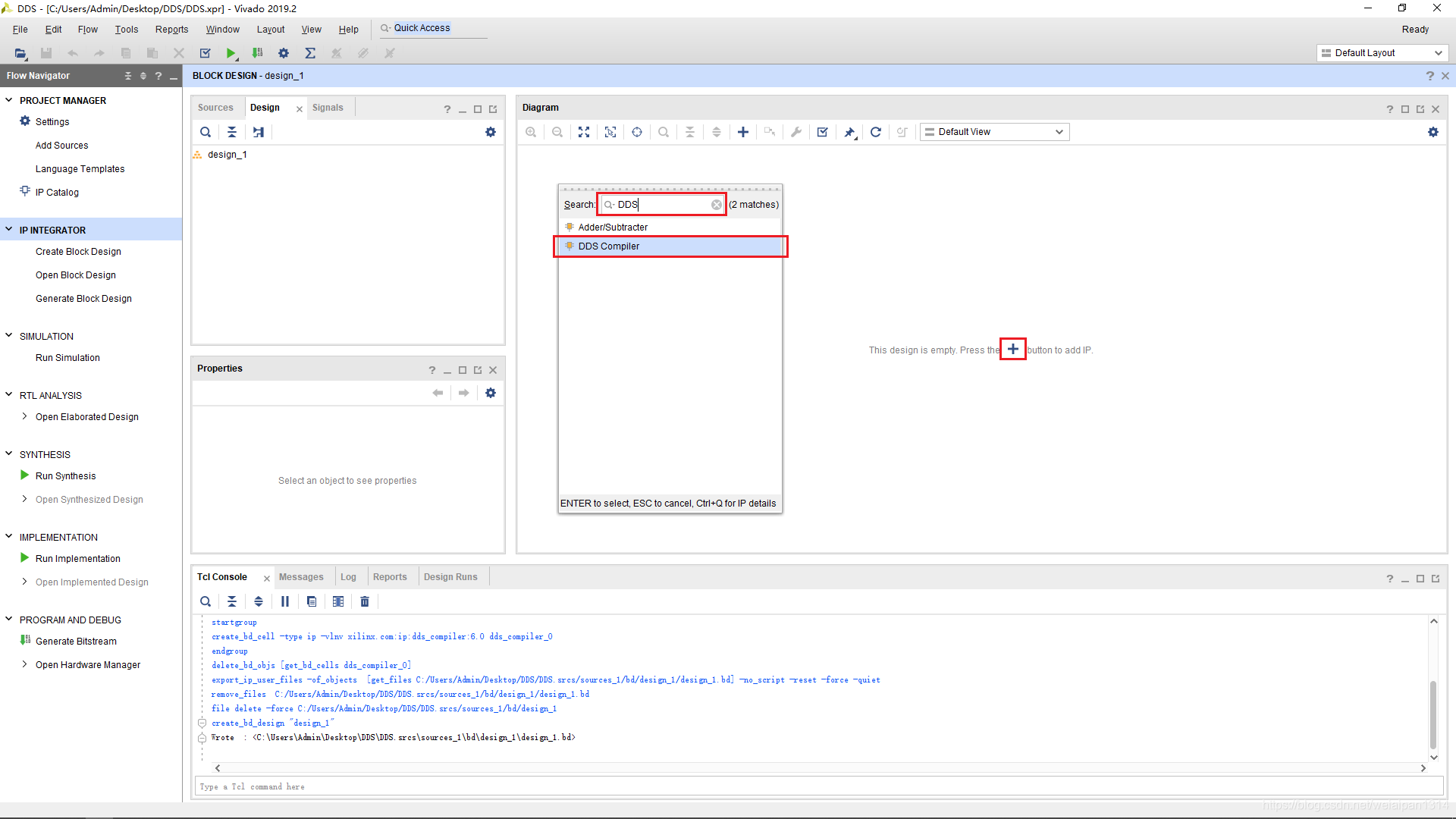

二、IP的定制及讲解

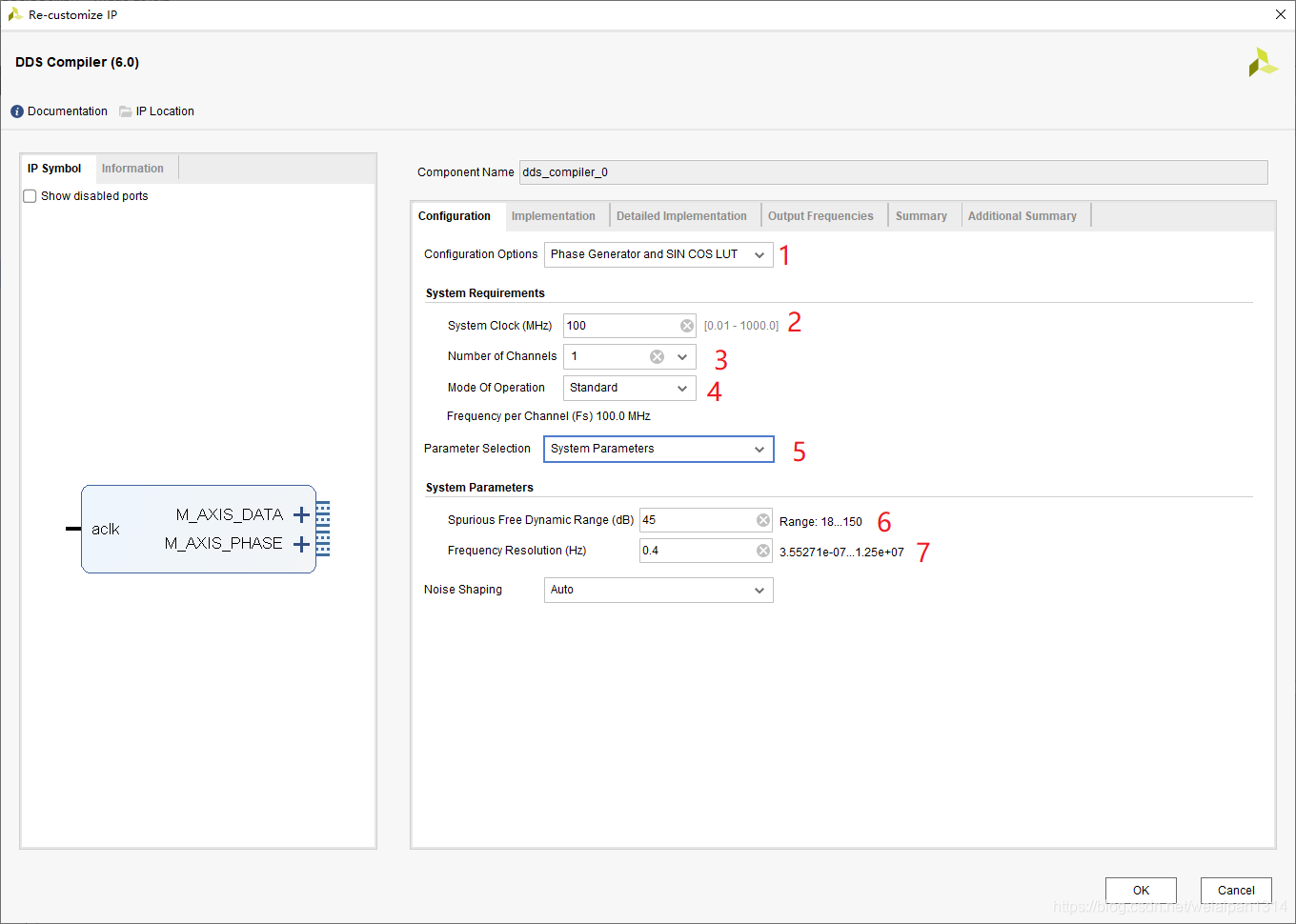

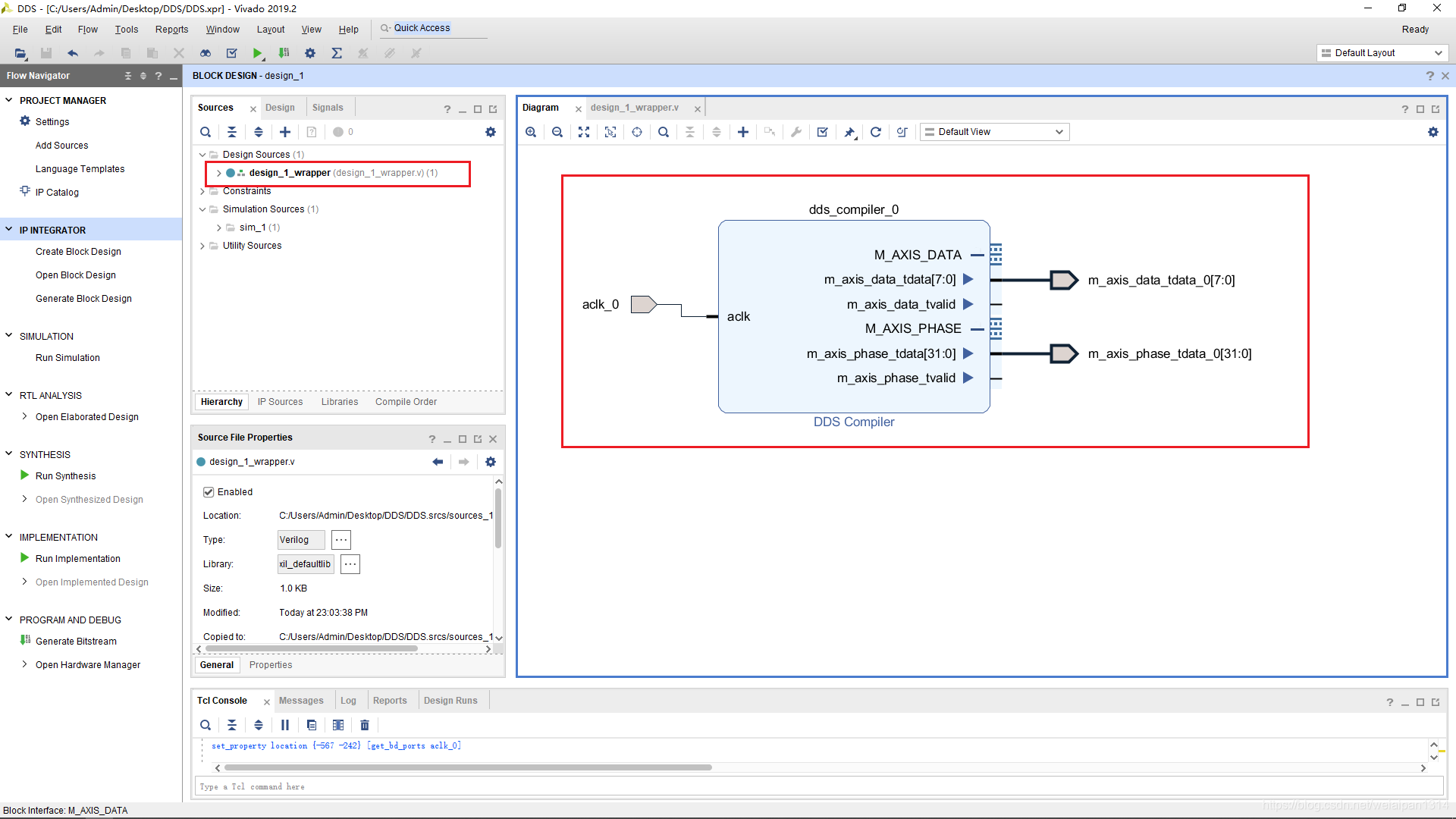

1、我们选择波形与相位同时存在的情况。

2、选择DDS IP输入的系统时钟频率,这里我们选择100MHz。

3、DDS通道的数目,我们这里选择一个。

4、整个IP配置的模式,我们这里选择标准模式即可。

5、参数选择的模式,我们这里选择系统参数,这个选择主要影响IP的定制界面所涉及到的参数。

6、频率的动态范围,主要和DDS内部RAM的数据位宽有关,计算方法是20log2n,其中n为RAM的位宽。

7、选择DDS的最小的频率分辨率。

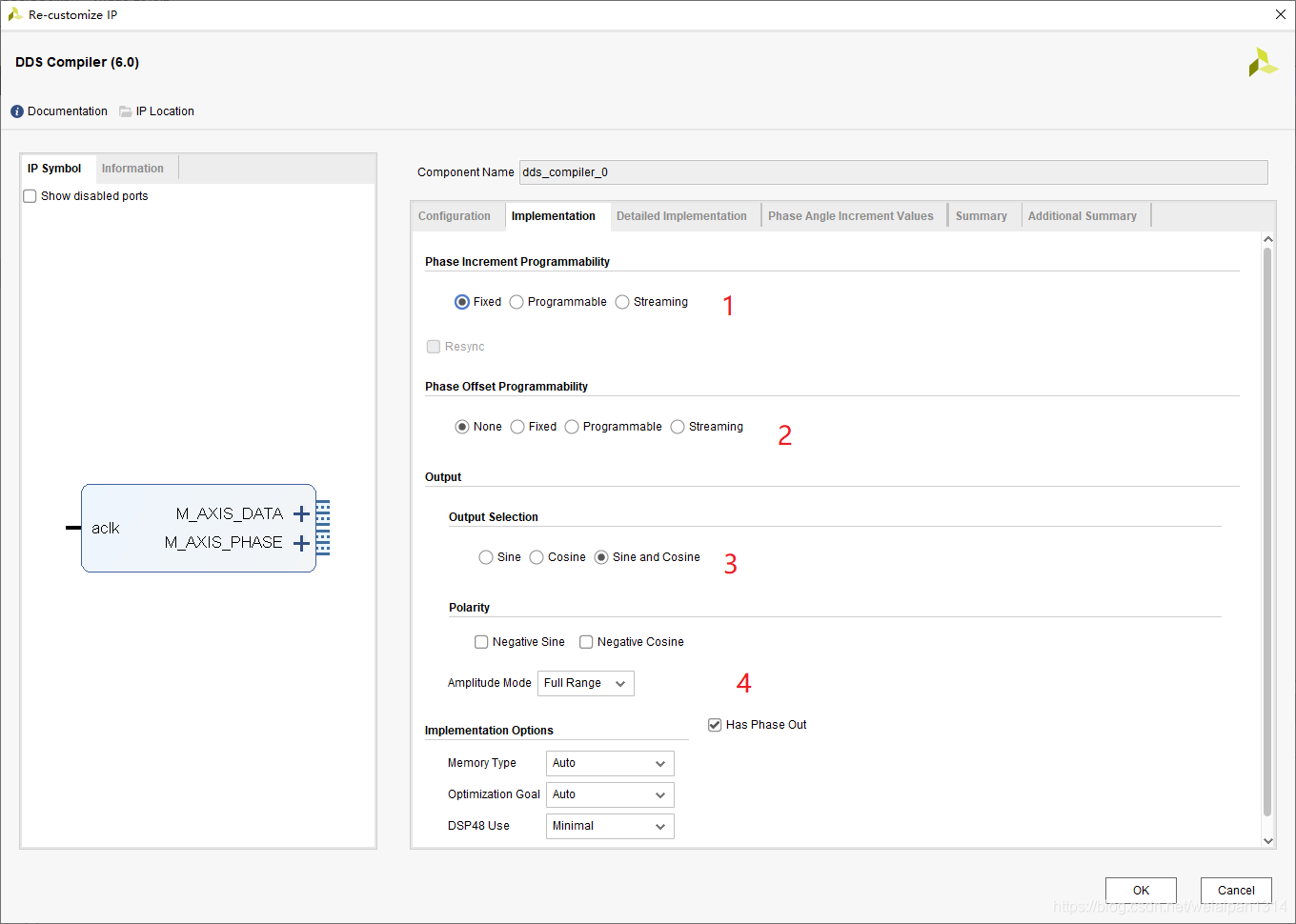

1、相位增量我们选择固定

2、相位偏执我们也选择成固定,这两个参数可以动态控制输出的频率。

3、我们这里产生正弦波和余弦波

4、因为我们只考虑正弦波的频率,所以这里不再输出相位信息

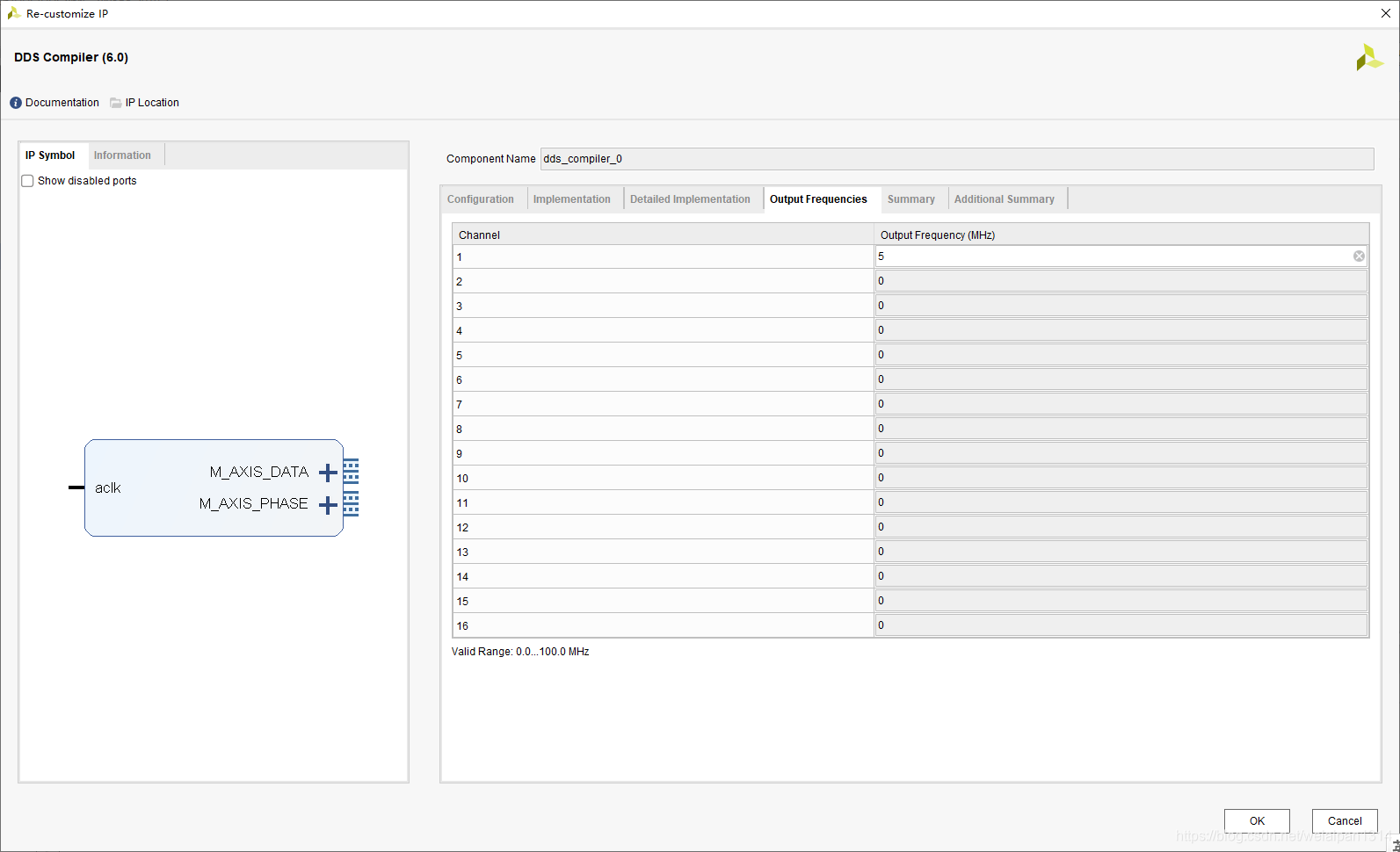

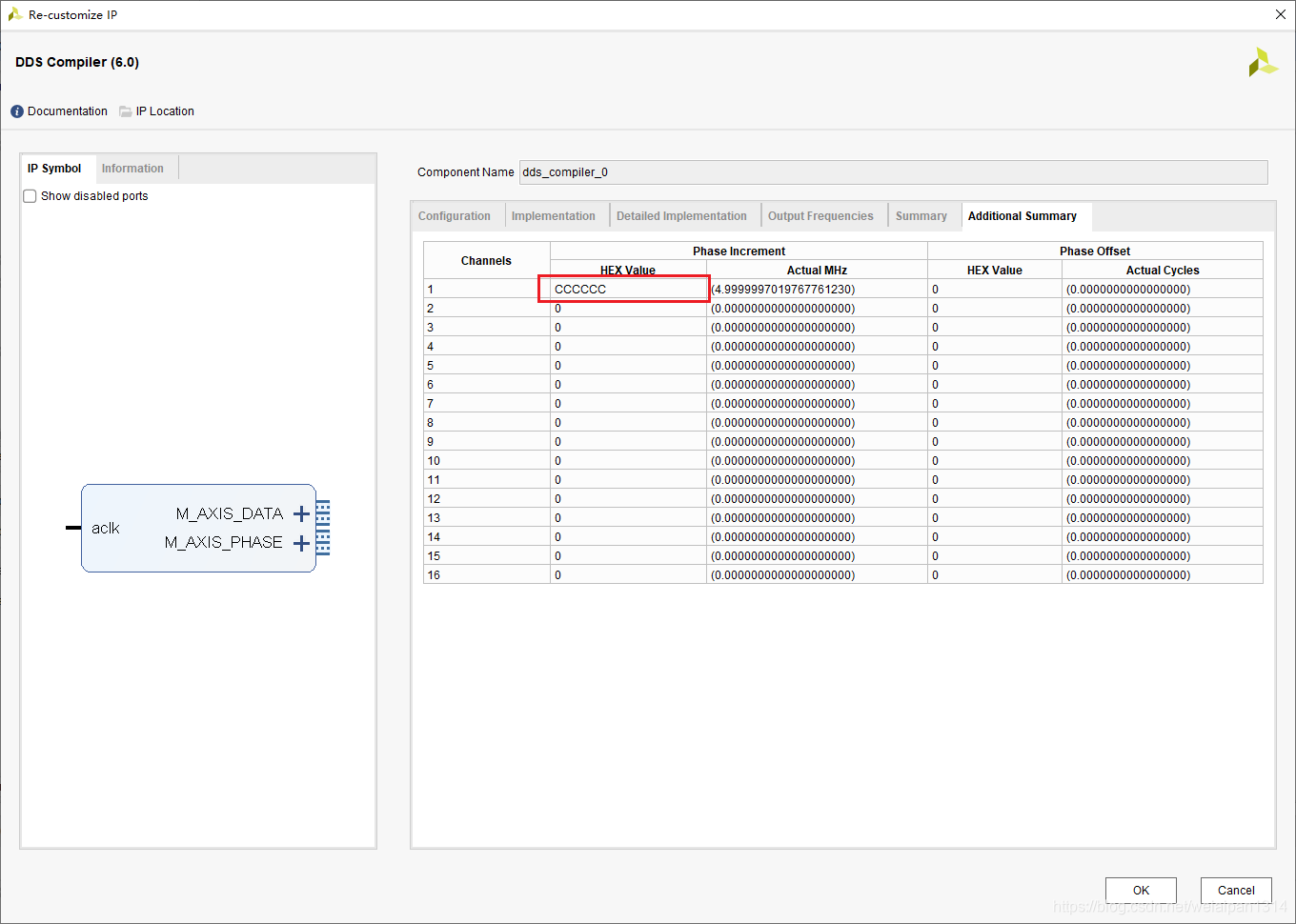

输入我们需要DDS输出的频率,这里我们输入5MHz。其余选项,我们选择默认即可。点击确定

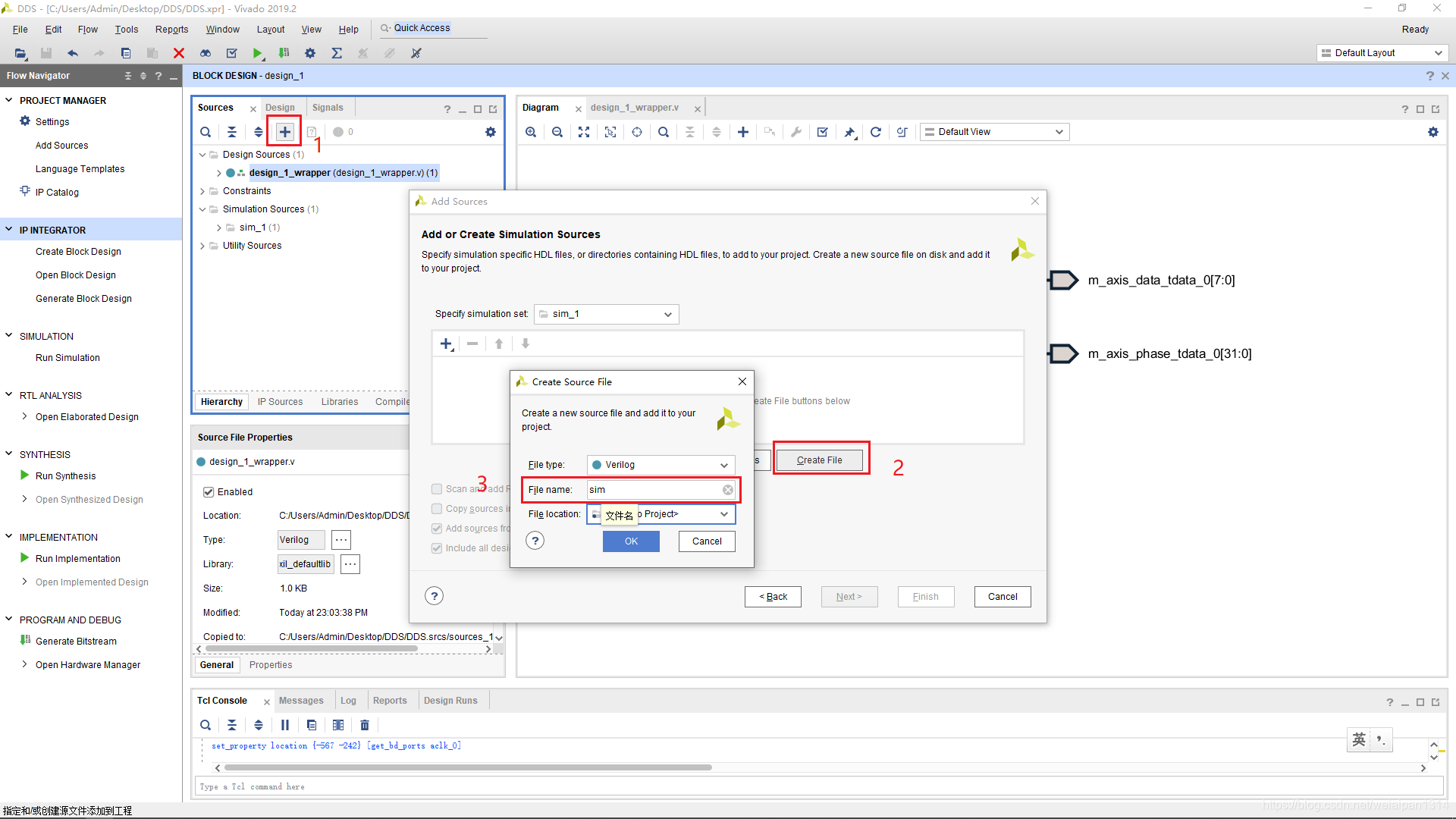

三、Testbench编写

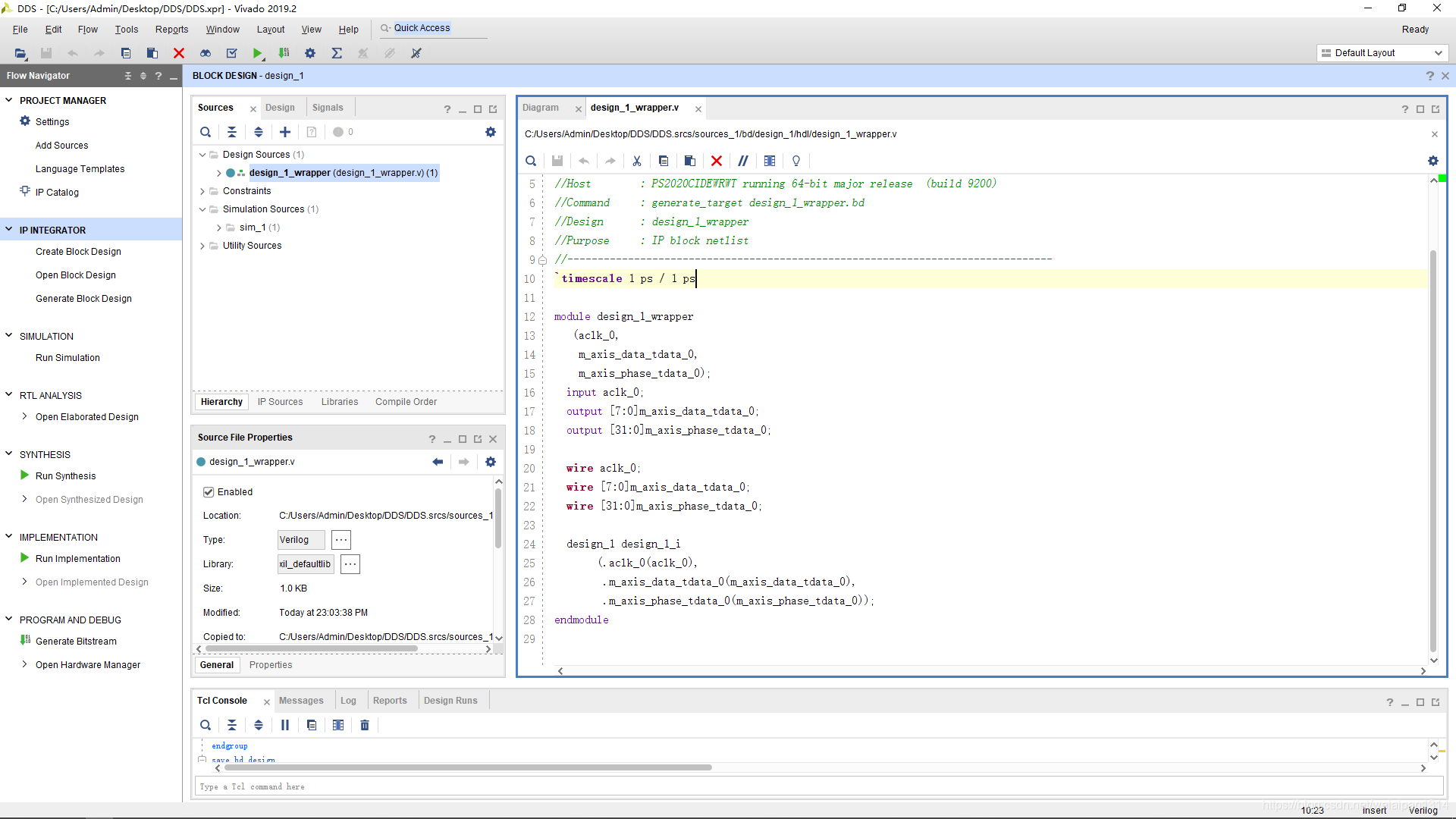

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/12/01 23:08:37

// Design Name: 技术先生

// Module Name: sim

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module sim(

);

wire [7:0] m_axis_data_tdata_0 ;

wire [31:0] m_axis_phase_tdata_0 ;

reg aclk ;

initial begin

aclk = 1'b0;

end

always #5 aclk = ~aclk;

design_1_wrapper design_1_wrapper_u0(

.aclk_0 (aclk ),

.m_axis_data_tdata_0 (m_axis_data_tdata_0 ),

.m_axis_phase_tdata_0 (m_axis_phase_tdata_0 )

);

endmodule

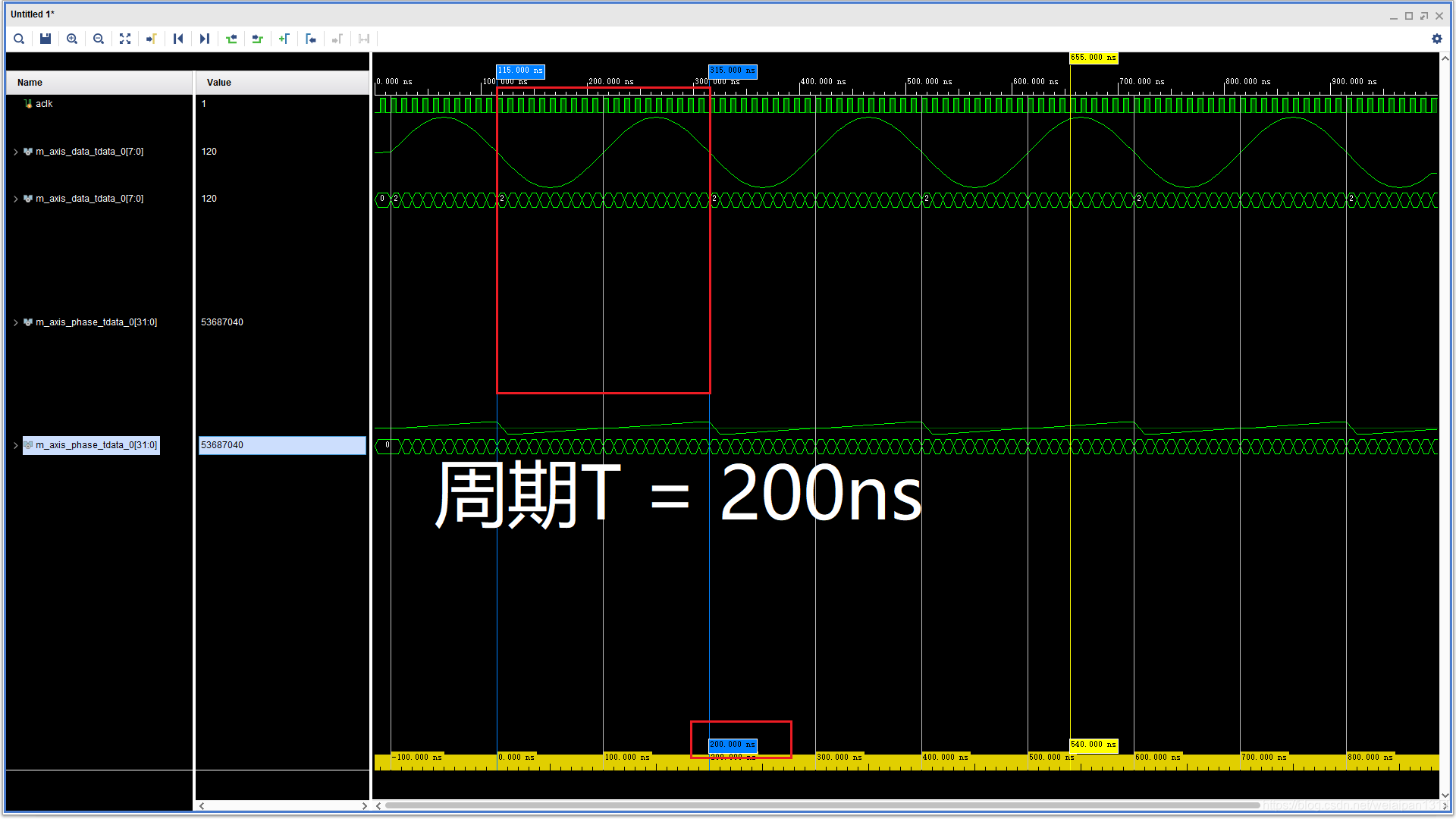

四、波形分析

(1)核心的核心:5M的波形周期则为200ns,因为时钟只有100M,所以一个周期只能输出20个点。

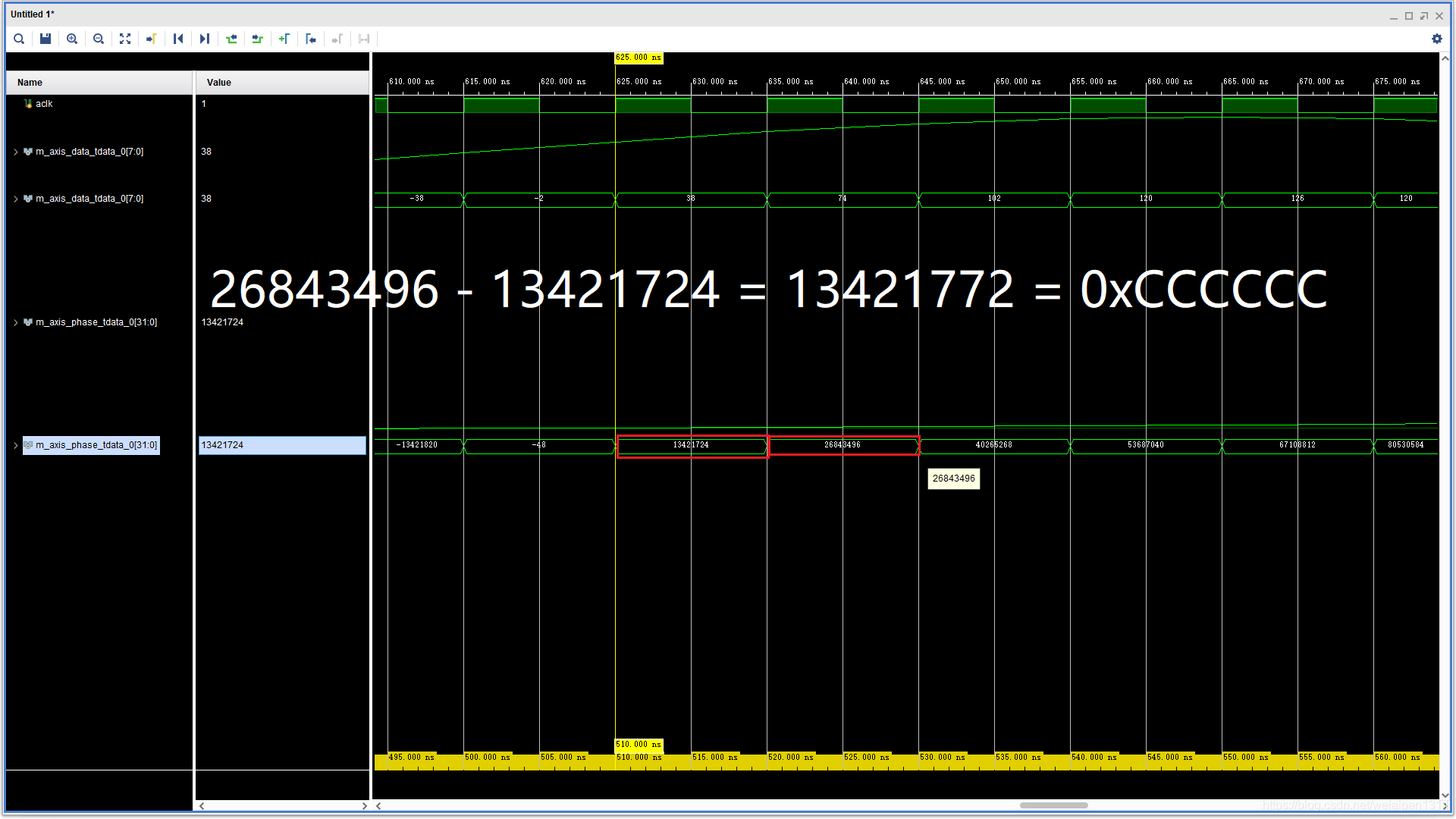

(2)核心的核心:设置界面Summary显示Phase Increment值为0xCCCCCC,从波形上也可以看出,两个点角度差0xCCCCCC。

五、源代码下载

链接:https://pan.baidu.com/s/1vR92zQ3Xu4Cfbf7f4Dy3cQ

提取码:mh0r

推荐内容

阅读全文

AI总结

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

相关推荐

查看更多

A2A

谷歌开源首个标准智能体交互协议Agent2Agent Protocol(A2A)

adk-python

一款开源、代码优先的Python工具包,用于构建、评估和部署灵活可控的复杂 AI agents

Second-Me

开源 AI 身份系统,通过本地训练和部署,模仿用户思维和学习风格,创建专属AI替身,保护隐私安全。

热门开源项目

活动日历

查看更多

直播时间 2025-04-09 14:34:18

樱花限定季|G-Star校园行&华中师范大学专场

直播时间 2025-04-07 14:51:20

樱花限定季|G-Star校园行&华中农业大学专场

直播时间 2025-03-26 14:30:09

开源工业物联实战!

直播时间 2025-03-25 14:30:17

Heygem.ai数字人超4000颗星火燎原!

直播时间 2025-03-13 18:32:35

全栈自研企业级AI平台:Java核心技术×私有化部署实战

所有评论(0)