STM32F103电路引脚功能定义及部分参考电路设计

STM32F103各引脚(LQFP64)功能定义NOTE:1.供电方案●VDD = 2.0至3.6 V:用于I / O的外部电源和内部稳压器,通过VDD引脚从外部提供。●VSSA,VDDA = 2.0至3.6 V:用于ADC,DAC,复位模块,RC和PLL(当ADC或DAC模块使用,施加到VDDA的最小电压为2.4 V), VDDA和VSSA必须分别连接到VDD和VSS。●VBA...

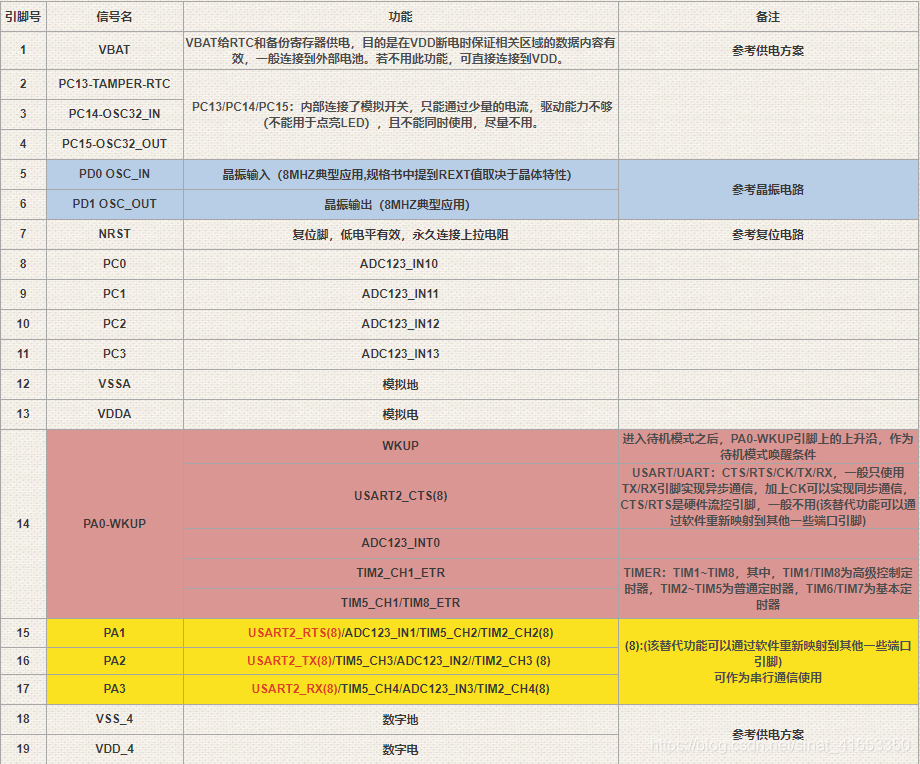

STM32F103各引脚(LQFP64)功能定义

NOTE:

1.供电方案

●VDD = 2.0至3.6 V:用于I / O的外部电源和内部稳压器,通过VDD引脚从外部提供。

●VSSA,VDDA = 2.0至3.6 V:用于ADC,DAC,复位模块,RC和PLL(当ADC或DAC模块使用,施加到VDDA的最小电压为2.4 V), VDDA和VSSA必须分别连接到VDD和VSS。

●VBAT = 1.8至3.6 V:当不存在VDD时,用于RTC,外部时钟32 kHz振荡器和备用寄存器(通过电源开关)。

从上图可知:

每个VDD各接一个100nF陶瓷电容,其中VDD3需要再接一个4.7uF的钽电容;

VDDA:接10nF陶瓷电容+1uF钽电容;

VREF+:可接VDDA,也可接外部参考源,此时也需要接10nF陶瓷电容+1uF钽电容;

2.通信接口

1.I2C总线

STM32F103提供两个I2C总线接口,作为从机时,支持7/10位寻址模式和7位双寻址模式,I2C总线配置可由DMA控制器提供服务。

2.SPI接口

在全双工和单工通信模式下,从机和主机模式下,提供三个SPI接口能够以18Mbit/s速率通信,所有SPI接口配置均可由DMA控制器提供服务。

3.I2S接口

I2S(Inter-IC Sound)是飞利浦公司针对数字音频设备(如CD播放器、数码音效处理器、数字电视音响系统)之间的音频数据传输而制定的一种总线标准。它采用了独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。标准的I2S总线电缆是由3根串行导线组成的:1根是时分多路复用(简称TDM)数据线;1根是字选择线;1根是时钟线。

STM32F103提供两个I2S总线接口(与SPI2和SPI3复用),音频采样频率支持8KHz至48kHz。

I2S有3个主要信号:

1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

2. 帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

3.串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

4.USART接口

STM32F103系列嵌入了三个通用同步/异步接收器发送器(USART1,USART2和USART3)和两个通用异步接收器发送器(UART4和UART5)。

USART1接口能够以高达4.5Mbit/s速率通信,其余可用接口通信速率最高为2.25Mbit/s,USART1,USART2和USART3还提供CTS和RTS信号的硬件管理。DMA控制器可以为所有接口提供服务,但UART5除外。

引脚功能定义:

TX:发送数据输出引脚。

RX:接收。

nRTS:请求以发送,n表示低电平有效。如果使能 RTS 流控制,当USART接收器准备好接收新数据时就会将nRTS变成低电平;当接收寄存器已满时,nRTS将被设置为高电平。该引脚只适用于硬件流控制。

nCTS:清除以发送(Clear To Send),n表示低电平有效。如果使能 CTS流控制,发送器在发送下一帧数据之前会检测 nCTS 引脚,如果为低电平,表示可以发送数据,如果为高电平则在发送完当前数据帧之后停止发送。该引脚只适用于硬件流控制。

SCLK:发送器时钟输出引脚。这个引脚仅适用于同步模式。

下图是STM32F103(LQFP64)的USART引脚分布的总线示意,可以看出USART1的时钟来源于APB2总线时钟,最大频率为72MHZ,其他4个时钟来源于APB1总线时钟,最大频率36MHZ。UART只有异步传输功能,没有SCLK(CK)、nCTS(CTS)和nRTS(RTS)功能引脚。

3.功能概述

1.温度感应器

温度传感器必须产生随温度线性变化的电压。转换范围在2 V <VDDA ❤️.6 V之间。温度传感器内部连接到ADC1_IN16输入通道,该通道用于将传感器输出电压转换为数字值。

2.ADC(模数转换器)

STM32F103系列嵌入了三个12位模数转换器,ADC可由DMA控制器提供服务,模拟看门狗功能可以精确地监视所有选定通道的转换电压,当转换后的电压超过设定的阈值后,将产生中断。

3.DAC(数模转换器)

STM32F103系列提供二个12位缓冲DAC通道,可用于将两个数字信号转换为两个模拟电压信号输出,设计结构有集成电阻串和反向配置的放大器组成。

参考电路:

1.晶振电路

2.复位电路

3.MCU电路

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)