简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

芯片流片完成后需要上板进行测试,考虑到PCIe高速协议的复杂性,需要采用一系列手段对信号质量进行测试,以确保误码率在一定范围内,从而不会引起通信错误。

边缘端侧AI芯片专场

此前写过向量扩展0.9的阅读记录,三年已过,本以为不再参与RVV的相关开发,奈何造化弄人,旧业重操,真就世事难料呀。总的来说1.0版本相比0.9版本的扩充了较多内容,但大部分为指令功能的扩充,指令编码、向量的运行机制等几乎没有变化,也就是说0.9版本的工具链可以兼容1.0的共性的指令。本文主要针对1.0新的版本作阅读记录,与0.9相同功能将不再赘述,若有所区别将在下文中体现。

大模型基于llama.cpp在Qemu-riscv64向量扩展指令架构的模拟器上部署

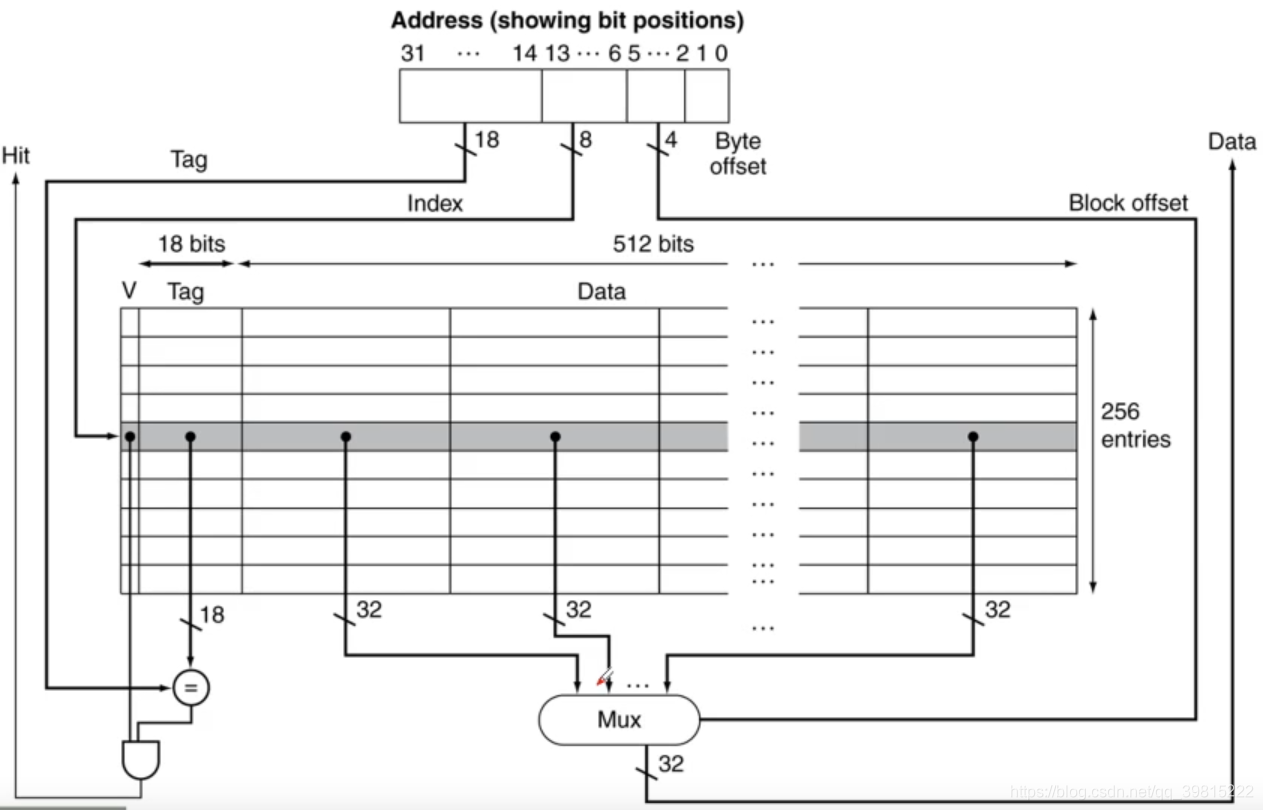

cache是小容量、高速缓冲存储器,由SRAM组成,速度几乎和CPU一样快。一般将cache和主存的存储空间都划分为若干大小相同的块

边缘端侧AI芯片专场

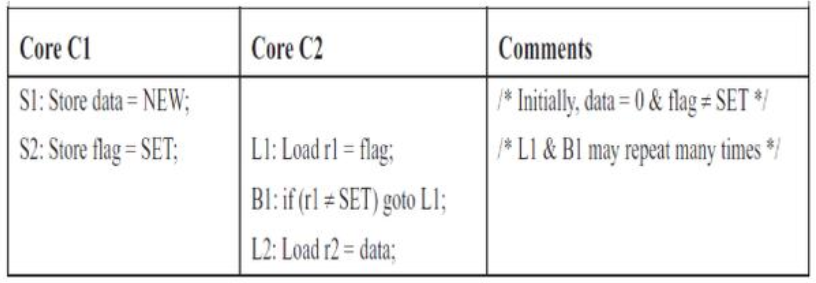

根据内存一致性模型,多核多线程的程序无约束执行的结果是不可确定的,因此为限制指令的执行顺序,便引入了特殊的存储器屏障指令(memory fence)。FENCE指令用于屏障“数据”存储器访问的执行顺序。如果在程序中添加一条FENCE指令,则该FENCE能够保证“在FENCE前所有指令的数据访存结果”必须比“在FENCE后所有指令数据访存结果”先被观测到,即FENCE前的访存指令必须比FENCE后的

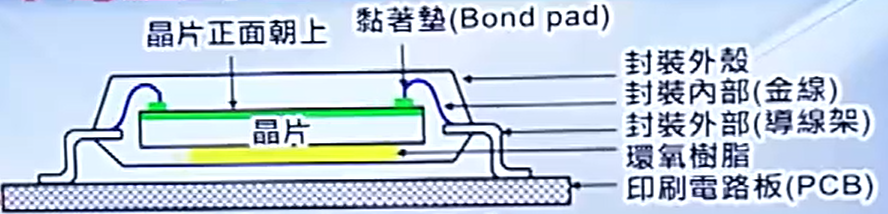

芯片封装技术介绍

芯片封装技术介绍

STM32:逻辑错误:1、若要用引脚重映射,一定要把该引脚原来的功能DISABLE,不然永远都没有想要的结果。例如:将TIM4_CH1映射到PB4,PB4原功能是JRST,因此需要调用GPIO_PinRemapConfig(GPIO_PartialRemap_TIM3,ENABLE);//PB4 TIM3_CH1GPIO_PinRemapConfig(GPIO_Remap...