简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

这两天在捣鼓ZYNQ的PS-PL的相关内容,想试着自己在PL端创建一个AXI IP核来给PS进行控制,顺便写一写驱动代码,但是在实验的中途就遇到了几个比较奇怪的问题,最主要的是在生成完IP核后我再去修改驱动,发现在使用XSA文件导入硬件平台后,vitis中显示我的修改并没有生效,在到处搜索了一下答案后发现了问题所在,这里记录一下。

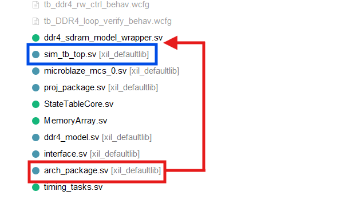

摘要:作者在仿真DDR4 IP核时遇到两个编译错误:'arch_package'和'_8G'未声明。通过检查确认arch_package.sv文件已包含在工程中,并在编译顺序设置中将该文件调整到sim_tb_top.sv文件之上后,问题得到解决,仿真可正常启动。

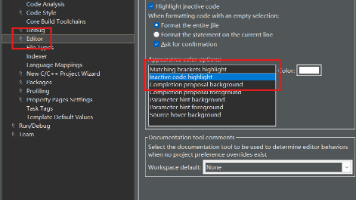

VITIS切换暗色主题后,发现C文件中if块高亮显示异常。解决方法是在Windows→Preference→C/C++→Editor中修改Inactive Code Highlight颜色,选择较深色即可。注意需在C/C++的Editor设置中修改,在General下的Editor修改无效。调整后if块高亮显示恢复正常。

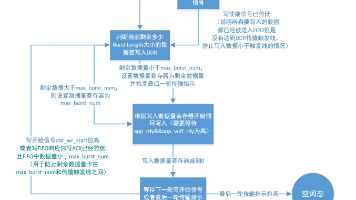

本文介绍了DDR4存储器与FIFO缓冲协同工作的Verilog实现方案。针对高低带宽转换问题,提出使用深度FIFO进行缓冲,并分析了单次与多次突发传输对DDR效率的影响。重点阐述了FIFO配置原则(写FIFO需采用FWFT模式)、状态机设计(包含初始化/空闲/读/写4个状态)以及关键控制信号处理。提供了完整的DDR读写控制模块代码,包含地址计算、突发长度管理和FIFO交互逻辑。文章最后指出将进行下

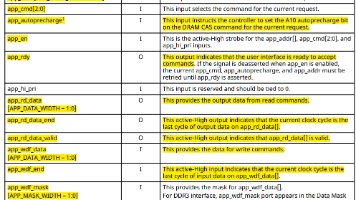

本文总结了DDR4内存控制IP核MIG的使用方法。主要内容包括:1)MIG IP核的创建界面和关键参数(如BurstLength=8)的说明;2)MIG控制信号分类详解,包括全局接口、命令接口、写接口和读接口;3)重点分析了写操作的两种时序(非背靠背和背靠背)和读操作的时序特点;4)指出在高速应用中需要配合FIFO实现跨时钟域数据传输的问题。文章为后续DDR4的实际应用提供了基础性的控制信号操作指