简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

在这个创新加速的时代,理解柔性电路板的特性与价值,将成为硬件开发者的必修课。当我们在享受智能设备带来的便利时,不妨多关注那些隐藏在设备内部、正在悄然改变世界的柔性"神经网络"。现代电子设备轻量化、微型化的浪潮中,一种特殊的电路板正悄然改变着技术格局——它既能像纸张般弯曲折叠,又能承载精密电路传输信号,这就是被称为"电子设备血管"的FPC柔性线路板。值得关注的是,其全自动生产线可处理最小0.1mm的

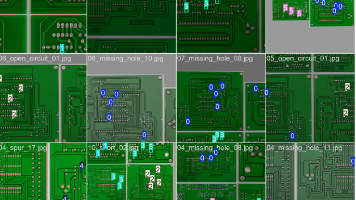

摘要:PCB缺陷检测正转向机器学习自动化方案,以解决传统人工检测效率低、误判率高的问题。针对工业场景中的缺陷多样性(0.1mm²微小空洞至0.5mm焊盘偏移)、数据不均衡(部分缺陷样本<5%)和实时性要求(200ms/板检测)三大痛点,需采用CNN+注意力机制等模型(最高98.7%准确率),配合高分辨率采集(≥2448×2048像素)和数据增强策略。关键技术包括Focal Loss处理样本不

摘要:针对PCB制造中AOI设备误报率过高问题,本文提出从算法、硬件、数据三个维度优化误报率的解决方案。通过深度学习分类、动态阈值算法等技术将误报率降至3%以下,结合智能光源、高精度运动控制等硬件协同优化,并构建缺陷知识库实现数据闭环管理。实际应用显示,该方案可将误报率从14.6%降至2.1%,减少83%人工复检工作量,综合检测成本下降37%,有效提升PCB制造品质管控效率。

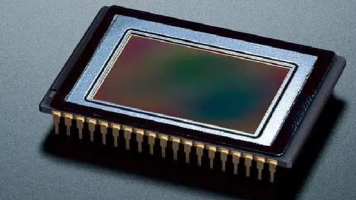

计算机主板的CMOS芯片是特殊RAM,存储BIOS配置参数(时间、启动顺序等),依赖纽扣电池供电保持数据。BIOS(基本输入输出系统)是固化在ROM芯片上的程序,负责开机自检、硬件初始化和启动引导。BIOS芯片:多采用PLCC32或SOIC8封装的Flash ROM(如Winbond W25Q128)CM芯片:通常为DIP8或SOP8封装的RAM(如ST M48T86)BIOS芯片:LPC或eSP

嵌入式元件封装(Embedded Component Technology, ECT)是指将电阻、电容、电感、IC等电子元件集成到PCB内部层间,而非传统表面贴装(SMT)。四层板结构(Top-L1-L2-Bottom)为嵌入式元件提供了更优的布线空间和信号完整性,适用于高密度、高性能电子设备,如5G通信、航空航天、医疗电子等领域。适用芯片埋入(Die Embedding)工艺,需进行金线键合(W

将 PCB 装配层数据导入结构设计软件(如 SolidWorks、ProE),与产品外壳、结构件、显示屏、电池等进行匹配,确保 PCB 能顺利装入整机,无结构干涉。可生成 3D 装配图纸、3D PDF 文件,指导生产、维修人员直观理解元器件安装位置、方向、结构,降低装配与维修难度。:标注元器件关键结构尺寸(长、宽、高、引脚间距、安装孔距、散热片尺寸),为结构设计、装配夹具设计提供精准数据。:常用元

文深入解析5G/AI芯片封装载板翘曲控制技术,聚焦塞树脂与盖帽工艺的协同优化。翘曲主因在于材料热膨胀系数差异(铜17ppm/℃ vs 树脂25-50ppm/℃)和薄型化趋势(厚度<0.15mm)。塞树脂通过填充过孔(CTE≤15ppm/℃)可降低60%局部应力,真空灌胶工艺使气泡率<1%。盖帽工艺(5-20μm铜层)提升2.3倍抗弯刚度,通过电镀应力调控实现翘曲矫正。二者协同需满足CTE梯度匹配(

FCT和ICT是PCBA制造中的两种核心测试技术,FCT通过动态功能验证确保系统级性能,ICT则进行静态参数检测定位元件级缺陷。二者在测试维度、流程协同和设备选型上存在显著差异。优化策略包括测试点设计规范、故障诊断案例分析和覆盖率提升方案。通过FCT/ICT后还需进行环境适应性和寿命加速等可靠性验证。随着技术发展,测试正向着智能化和三维化方向演进。这两种测试技术如同电子制造的"双保险&q

例如,在一些高端的 AI 芯片 PCB 中,会采用罗杰斯 RO4350B 等高频材料,其 DK 值低至 3.48,DF 值仅为 0.0037,大大降低了信号的损耗,使得信号能够在长距离传输中依然保持强大的活力。例如,对于差分信号,要求线距≥20mil,在 3.125G 以下的频率下,误差要<5mil,而在更高频率下,误差需<2mil,以此保证信号的稳定性和准确性。随着 AI 技术的不断发展,芯片的

本文系统阐述了四层PCB板叠层架构的设计原理与接口电路优化方案。通过TOP-GND-PWR-BOTTOM层叠结构实现电源完整性(纹波<10mV)、信号完整性(回波损耗<12dB)和EMI控制(辐射降低40%)。重点解析了高速信号控制、电源解决方案、EMI防护和可靠性设计四大维度,包括阻抗匹配、去耦电容布局、屏蔽结构和应力释放等关键技术。实例分析USB3.2和千兆以太网接口设计,并介绍L