简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

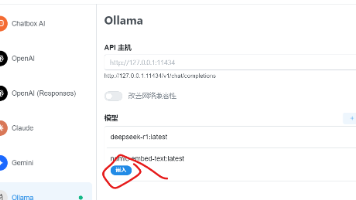

本文介绍了三种企业知识库构建方案:1)本地部署方案(Ollama+Chatbox),强调数据安全;2)云端API集成方案(CherryStudio/Confluence),适合企业级管理;3)混合模式,平衡安全与效率。详细说明了核心配置要点,包括模型选择(nomic-embed-text/bge-m3)、文档处理策略及性能优化方法。针对常见问题提供解决方案,如检索相关性低、响应速度慢等。最后根据不

是一个基于大语言模型(LLM)的工具,主要用于构建和管理个人或企业知识库。虽然它主要提供图形化界面(GUI)进行操作,但也可以通过代码进行一些高级配置和集成。以下是使用代码与 AnythingLLM 交互的基本方法和示例。

是两种不同的模型,主要区别在于架构、性能和应用场景。可能是更先进的版本,架构可能经过优化,参数量或层数有所调整。适合更大规模或更复杂的任务,如跨语言检索或多模态任务。可能使用了更多样化的数据集,包括多语言或多模态数据。性能可能更优,尤其是在大规模数据集或复杂任务上。可能在资源效率上进行了优化,适合资源有限的环境。需要较多计算资源,适合有较强硬件支持的环境。:可能是升级版,性能更强,适合更复杂的任务

满标度增益误差是理想ADC和实际设备在满标度输出时的输出误差的度量。实际ADC的V[0]是第一次代码转换的输入电压减去0.5LSB。偏移误差是根据代码零处的输入电压计算的。FSnom是理想ADC的满量程输入电压。

DFT-- design for test三要素:辅助性设计, physical defects结构性测试向量是一种辅助性设计,利用这种辅助性设计 对根据 physical defects 建立的 fault model 进行求解产生的结构性测试向量,这些结构性测试向量用于检测制造出来芯片的能否正常工作。scan chain 包含两个步骤: scan replacementscan stitchi

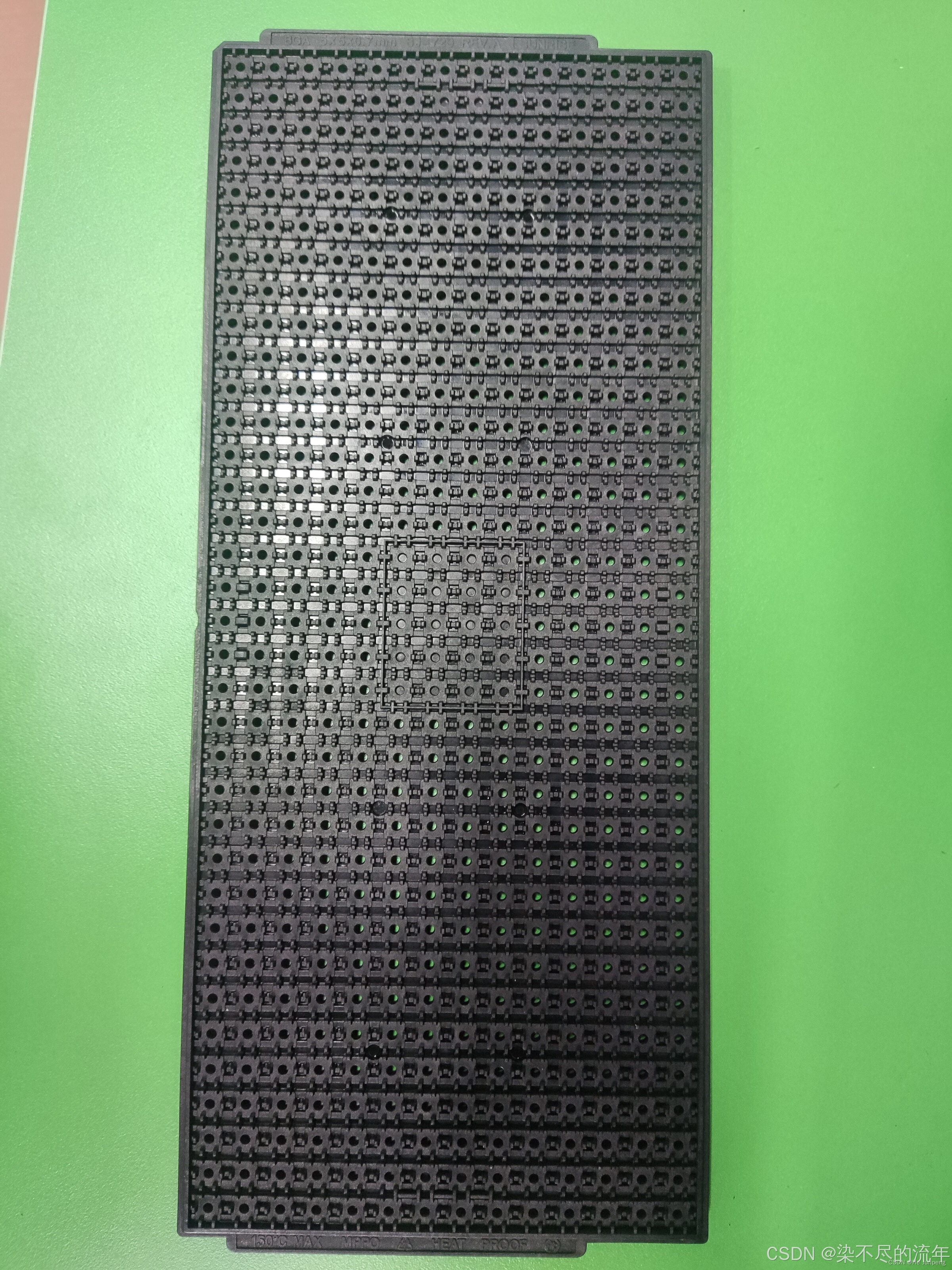

测试负载板(Load Board)是一种连接测试设备与被测器件的机械及电路接口,主要应用在半导体制造后端IC封装后的良率测试,透过此阶段 的测试,可以剔出功能不良的IC,避免后续电子产品因不良IC产生报废。它是一个IC和PCB之间的静态连接器,它会让芯片的更换测试更为方便,不用一直焊接和取下芯片,这样的话,就不会损伤芯片和PCB,从而达到快速高效的测试。ATE测试用的治具,安装与Handler,不

本文首先详解半导体芯片行业的三种运作模式,分别有IDM、Fabless和Foundry模式。其次介绍了半导体芯片及半导体芯片产业链重要环节,具体的跟随小编一起来了解一下。半导体芯片行业的运作模式1、IDM(Integrated Device Manufacture)模式主要的特点如下:集芯片设计、芯片制造、芯片封装和测试等多个产业链环节于一身;早期多数集成电路企业采用的模式;目前仅有极少数企业能够

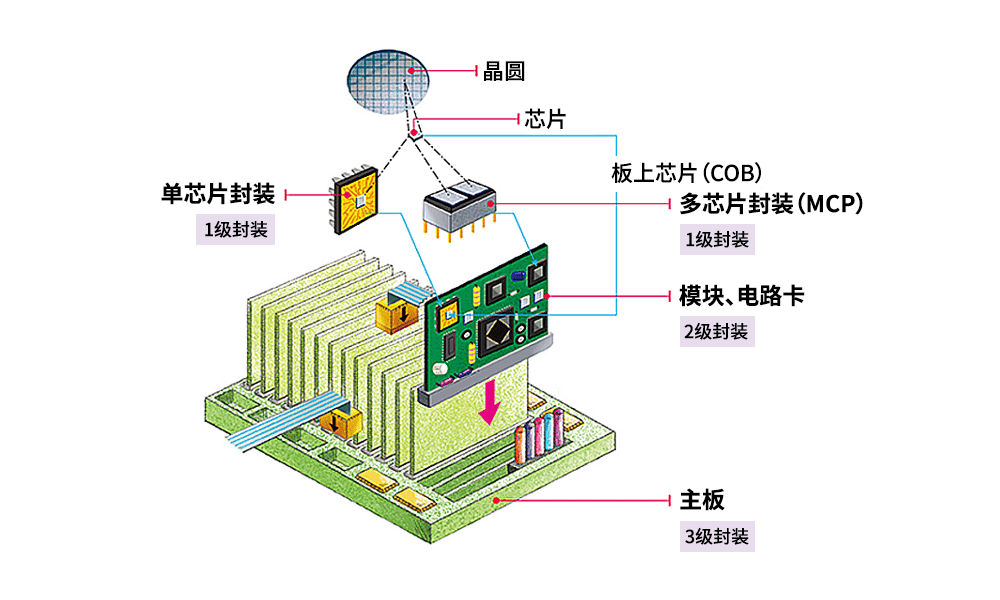

在邮寄易碎物品时,使用合适的包装材料尤为重要,因为它确保包裹能够完好无损地到达目的地。泡沫塑料、气泡膜和坚固的盒子都可以有效地保护包裹内的物品。同样地,封装是半导体制造工艺的关键环节,可以保护芯片免受物理性或化学性损坏。然而,半导体封装的作用并不止于此。本文是半导体后端(Back-End)工艺系列的第二篇文章,我们将详述封装技术的不同等级、作用和演变过程。

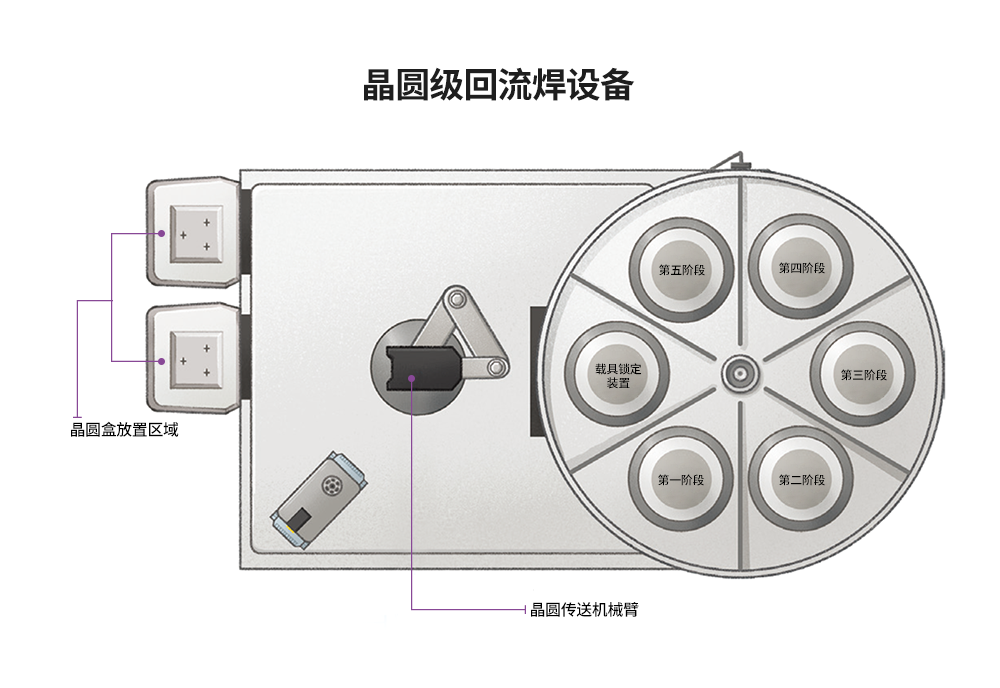

在本系列第七篇中,介绍了晶圆级封装的基本流程。本篇文章将侧重介绍不同晶圆级封装方法所涉及的各项工艺。晶圆级封装可分为扇入型晶圆级芯片封装(Fan-In WLCSP)、扇出型晶圆级芯片封装(Fan-Out WLCSP)、重新分配层(RDL)封装、倒片(Flip Chip)封装、及硅通孔(TSV)封装。此外,本文还将介绍应用于这些晶圆级封装的各项工艺,包括光刻(Photolithography)工艺、

PCB贴片元件封装焊盘设计尺寸标准