简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

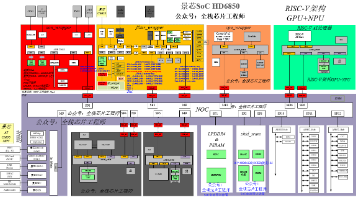

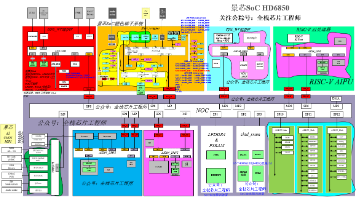

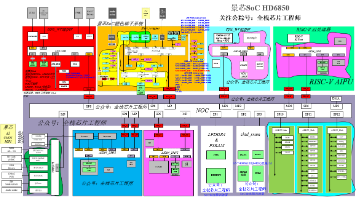

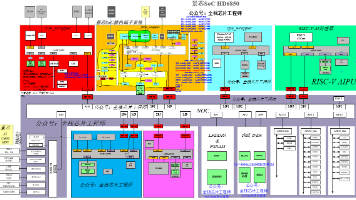

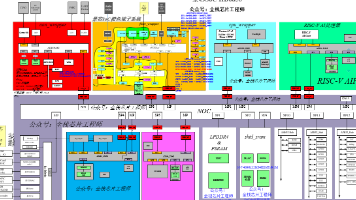

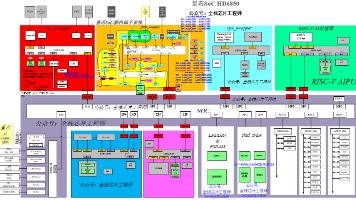

景芯团队推出DFT实战系列课程,采用40nm和12nm工艺节点,通过HD6850芯片项目进行分层教学。课程分为三个部分:基础课程讲解橙色子系统AIMCU芯片设计,进阶课程深入hierarchy流程实战,最终完成全芯片DFT设计。课程特色包括:RISC-V自研架构实现、AXI/AHB总线矩阵设计、MBIST/SCAN/OCC/EDT等DFT技术实战,以及12nm工艺节点下的综合、形式验证等完整流程。

景芯团队推出DFT实战系列课程,采用40nm和12nm工艺节点,通过HD6850芯片项目进行分层教学。课程分为三个部分:基础课程讲解橙色子系统AIMCU芯片设计,进阶课程深入hierarchy流程实战,最终完成全芯片DFT设计。课程特色包括:RISC-V自研架构实现、AXI/AHB总线矩阵设计、MBIST/SCAN/OCC/EDT等DFT技术实战,以及12nm工艺节点下的综合、形式验证等完整流程。

摘要:IEEE1500标准通过WrapperChain结构解决SoC芯片IP核测试难题。该结构在IP核边界布置可串联的寄存器单元(WBR),配合指令寄存器(WIR)和旁路寄存器(WBY),形成可控的测试通路。测试时,数据通过串行接口(WSI/WSO)流动,WIR解码指令控制测试模式,WBR捕获响应或施加激励。这种设计实现了IP核测试的隔离与重用,无需暴露内部细节,支持并行测试(WPP),并能在测试

摘要:景芯SoC40nm后端实战课提供1v1专家辅导,通过HD6850项目中的橙色域子系统进行全流程实战培训,涵盖设计、验证、中后端流程。课程特色包括终身辅导、低功耗设计(功耗降低98.9%)、版图设计及DRC/LVS检查等实战内容。训练营还涉及异步FIFO实现、PR布线优化等实际问题解决方案,并提供知识星球交流平台。课程面向希望提升芯片设计能力的技术人员,强调实践与经验分享。

【摘要】景芯团队推出系列DFT实战课程,涵盖40nm和12nm工艺芯片设计全流程。课程采用"文档+服务器实战"模式,通过HD6850芯片子系统案例教学,内容包含层次化设计流程、MBIST/Scan/EDT等技术实现。特色包括:1)分Flat和Hierarchy两种流程教学;2)覆盖12nm综合、Formality等高级内容;3)提供知识星球答疑平台。课程配套招聘服务,学员可胜任

Memory Repair(内存修复)是一种在芯片制造测试阶段检测并修复存储器缺陷的技术。其核心思想是在存储器设计中预留“冗余”(Redundancy)资源——额外的备用行(Spare Row)和备用列(Spare Column)基础存储器阵列与 Column MUX 架构示意图当检测到存储单元故障时,用这些冗余资源替换故障单元,从而使芯片恢复正常功能。而这个过程最严苛的要求,就是时序收敛。

现代SoC芯片中存储器占比达50%-80%,先进制程下存储器缺陷导致20%-30%芯片报废。Memory Repair技术通过在存储器设计中预留冗余资源(备用行/列)来修复故障单元,包含硬修复(eFuse永久固化)和软修复(SRAM动态更新)两种方式。核心技术包括MBIST(内存自测试)、BIRA(冗余分析)和BISR(自修复实现),通过检测-分析-修复-存储的流程提升良率15%-25%。该技术已