Verilog之非阻塞赋值(二)——赋值延后一个周期

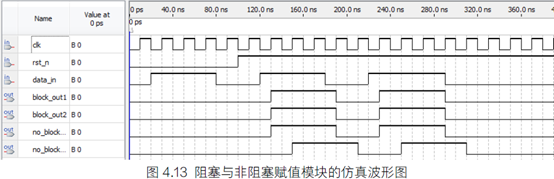

阻塞与非阻塞赋值,当在always块中的每一个条件分支中,仅有一条赋值语句(不管是阻塞与非阻塞,且要满足条件中的条件判断式不含有在本模块中定义并赋值的reg变量(采用非阻塞赋值)),那么阻塞和非阻塞都是在时钟边沿瞬间完成的;(理解非阻塞赋值分两个过程,RHS的计算为第一步,LHS的赋值为第二步,这是第一层面;第二,由于两步时间非常短,变现出来就是在时钟边沿瞬间完成,故表现的和阻塞一样,这是第二个层

阻塞与非阻塞赋值,当在always块中的每一个条件分支中,仅有一条赋值语句(不管是阻塞与非阻塞,且要满足条件中的条件判断式不含有在本模块中定义并赋值的reg变量(采用非阻塞赋值)),那么阻塞和非阻塞都是在时钟边沿瞬间完成的;(理解非阻塞赋值分两个过程,RHS的计算为第一步,LHS的赋值为第二步,这是第一层面;第二,由于两步时间非常短,变现出来就是在时钟边沿瞬间完成,故表现的和阻塞一样,这是第二个层面)

其二,当条件判断式中含有的条件判断式是外部输入的数据,或者是本模块的阻塞赋值变量,那么也是在边沿瞬间完成赋值(外部输入信号边沿对齐时钟边沿时要延后一个周期);

其三,如果条件判断式中含有本模块的非阻塞赋值的reg变量,那么在该条件分支下的非阻塞赋值语句会延后一个周期完成(相对于条件判断式中的变量的赋值完成)。

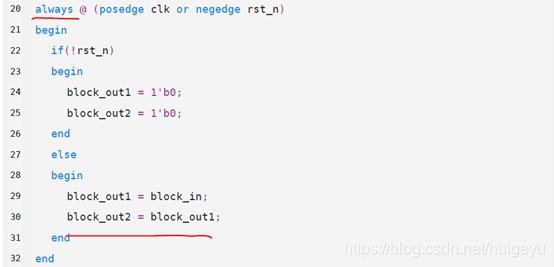

其四,一个条件分支中含有多条非阻塞语句时,若non1(第一条LHS)出现在第二条语句的RHS中,则会出现non2延迟一个周期的情况,如下;

要理解赋值和采样的不同,条件判断式中的条件相当于采样,即在时钟边沿条件变量的值被采样并与条件做对比,之所以条件中含有非阻塞变量时会延后一个周期,本质是被采样的reg变量在其他模块使用了非阻塞赋值,而非阻塞赋值完成有两个步骤,在某一个仿真节拍(不是一个仿真周期),被采样的还没有赋值完成(处在RHS的计算阶段),而采样时同时进行,这样,采样到的就是上一个周期的reg变量的值,虽然马上在边沿完成赋值,但采样已经结束,故在这个仿真周期结束时,被采样的完成赋值,但条件分支(含有被采样reg的判断表达式)下的变量赋值在下一个周期得到目标值,故而表现为相对被采样的变量的赋值,延后一个周期完成赋值。

同理,条件分支下含有多条非阻塞赋值语句时,理解也是一样:在同一个仿真节拍(RHS的计算),下一条非阻塞赋值的变量non2的右端得得到的是上一周期的前一非阻塞赋值的reg的值(non1),而在第二仿真节拍(赋值),non2和non1得到的值就不是一样的,故non2会表现的延后一个周期。

-->总结:非阻塞赋值延后一个周期3种情况

1、条件分支中变量(不管是外部输入还是本模块的非阻塞reg型)的边沿对齐时钟边沿时,采样采的是上一周期的值(历史值),故分支内的非阻塞赋值会延后一个周期。

2、凡是出现在同步时序always块中,条件分支中出现非阻塞变量或者与时钟边沿对齐的情况,采用非阻塞赋值会使变量赋值延后一个周期。

3、多条非阻塞赋值语句;

Case1:外部输入信号(wire型),在条件判断式中出现,波形上与时钟边沿对齐;

Case2:本模块的reg型(非阻塞赋值),send_en与send_bit_cnt;

Case3:见前一页总结的图片

上述描述清晰说明了3种非阻塞赋值使得赋值延后一个周期的情况,同时给出了“采样”的概念,这里是做一个引申,目的是更好地分析为什么会延后一个周期。

到此,结合前一篇博客,对阻塞与非阻塞的说明大概是比较清楚了。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)