史上最全的Logisim运算器实验教程(基于华中科技大学计算机组成原理实验)

本博客是实现了Logisim的运算器设计,有具体的运算器设计的思路和运算器设计的电路,适合一步一步的按照思路做。

目录

看完有收获给我点个赞这对我很重要🌹🌹🌹🌹

你的点赞让我的创作更有动力⭐⭐⭐⭐⭐

第1关:8位可控加减法电路设计

首先此实验是通过Sub来控制是加法电路还是减法电路,我们要知道在电路中没有直接的进行加法迅速的,所以我们可以想要使用补码进行计算,补码是被广泛用于计算机硬件中的计算因为补码可以很好的进行加减法计算。

第一步:我们需要了解是一位全加器是什么,工作的原理是什么样子的

全加器: 三个输入位(被加数、加数和来自低位的进位)相加的结果,并产生两个输出位(和数与进位)。

半加器: 两个输入端(A和B)和两个输出端(S和C)。其中,S表示两个输入位的和(0或1),C表示进位(如果有进位则为1,否则为0)。

第二步:计算机无法直接进行减法运算,故引入补码概念。至此计算机中可将加减法看作一类运算。

[A]补+[B]补=C

[A]补-[B]补=[A]补+[-B]补=[A]补+([B]补)全反+1=C

第三步:溢出判断,关于无符号数溢出判断较为容易,即最高位产生进位时运算结果溢出,故 Cout = 1 为溢出。而对有符号数溢出判断时则有一定难度,就结果而已,其溢出结果可通过符号位与最高位共同判断。

S符号位 ⊕ Z最高位 = 1 为溢出

S符号位⊕ Z最高位 = 0 无溢出

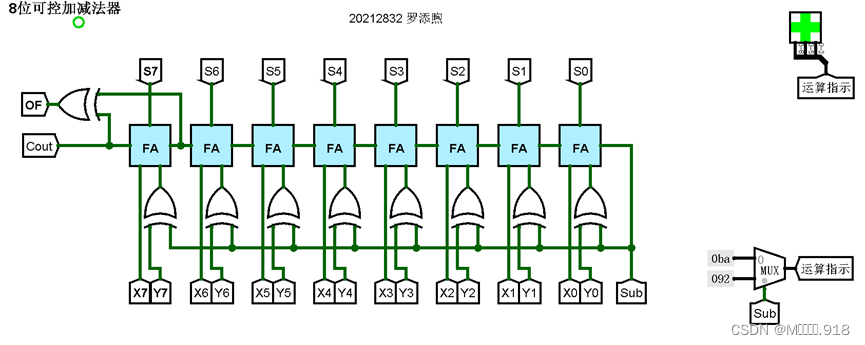

第四步:接下来就可以绘制电路图了,电路图如图2.1所示:

图2.1 8位可控加减法器

第2关:CLA182四位先行进位电路设计

全加器虽然弥补了半加器无法实现多位相加的缺陷,可从前面的实验不难看出,高位进行运算时必须等待低位的进位信号,导致延迟的增加。

所以在当机器数数位是确定的时候,我们可以用一种复制的计算算出每一位的进位,无需等待低位给出进位信号,因此出现了先行进位电路。

- 生成信号(Generate):Gi = Ai · Bi

- 传递信号(Propagate):Pi =Ai + Bi

此电路逻辑表达式:

P = P4 P3 P2 P1

G = P4 P3 P2 G1 + P4 P3 G2 + P4 G3 + G4

C1 = P1 Cin + G1

C2 = P2 P1 Cin + P2 G1 + G2

C3 = P3 P2 P1 Cin + P3 P2 G1 + P3 G2 + G3

C4 = P4 P3 P2 P1 Cin + P4 P3 P2 G1 + P4 P3 G2 + P4 G3 + G4

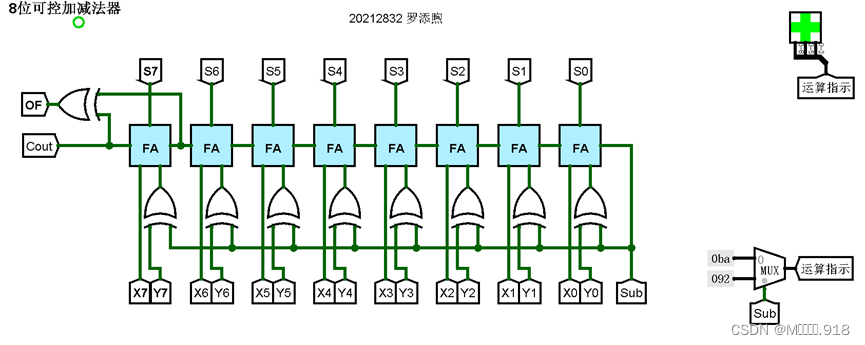

电路图如图2.2所示:

图2.2 四位先行进位电路图

第3关:4位快速加法器设计

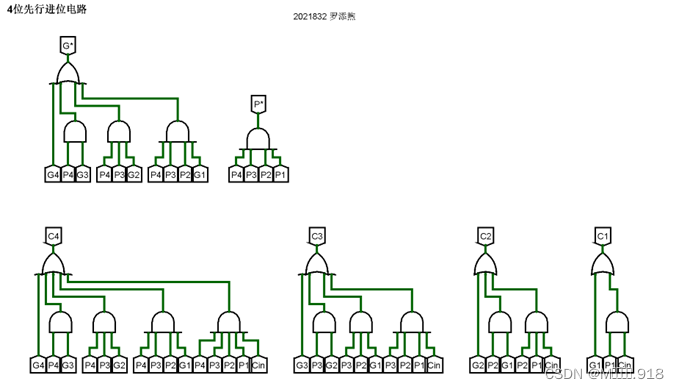

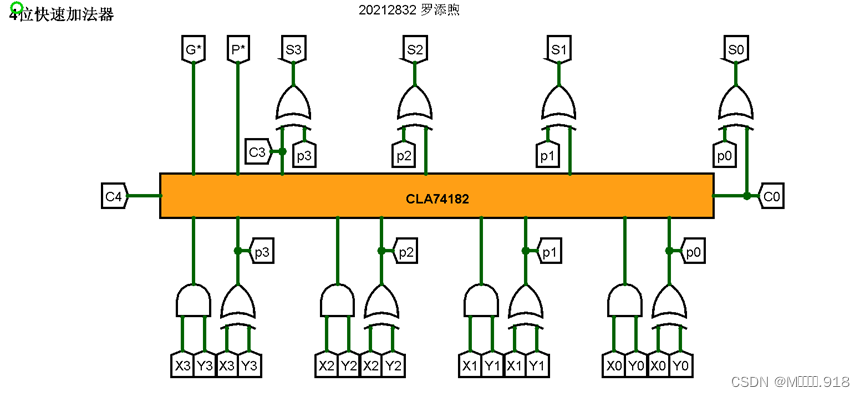

首先是把Pi和Gi对应的值通过与运算和异或运算Xi和Xi的值送到CLA74182中,然后就可以通过74182的输出的进位值直接的计算出每一位二进制数对应的值采用异或运算得到,所以就可以直接得到电路图如图2.3所示:

图2.3 4位快速加法器电路图

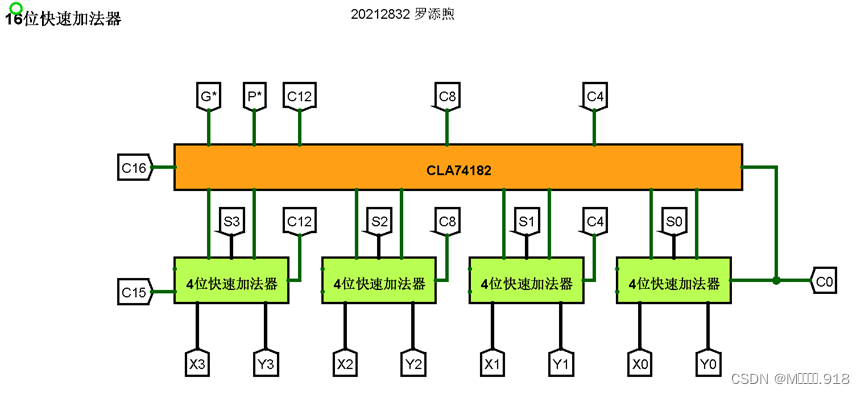

第4关:16位快速加法器设计

这个地方的16位快速加法器就和上面四位的实现差不多一个意思,这个地方就不写思路了,所以直接可以画出电路图电路图如图2.4所示:

图2.4 16位快速加法器电路图

第5关:32位快速加法器设计

这个地方的32位快速加法器就和上面四位的实现差不多一个意思,这个地方就不写思路了,所以直接可以画出电路图如图2.5所示:

图2.5 32位快速加法器电路图

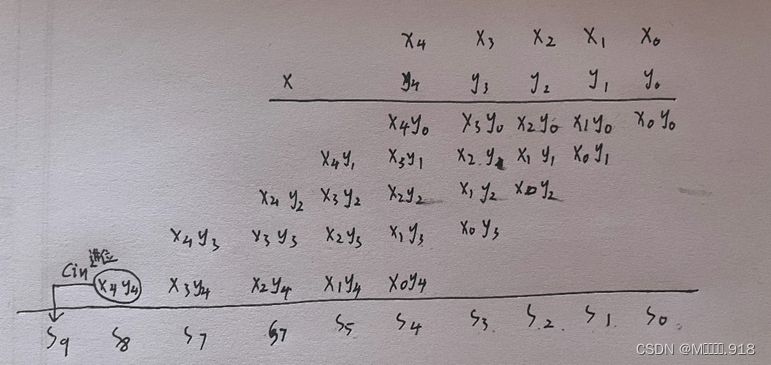

第6关:5位无符号阵列乘法器设计

在计算机硬件中是无法直接实现乘法运算的,对于乘法我们可以用高阶的加法进行计算,五位无符号的计算公式如图2.6所示:

图2.6 列阵乘法器

当然上面的图是没有把进位写上去的,进位我们采用斜向传递发所以可以得到斜向进位乘法器如图2.7所示:

图2.7 斜向进位乘法器

现在我们知道了斜向进位乘法器的构成就可以直接画出电路图如图2.8所示:

图2.8 5位无符号阵列乘法器电路图

第7关:6位有符号补码阵列乘法器

6位有符号补码阵列乘法器,也就是可以把符号位单独的拿出来,先算出来是正数就直接去后五位,不是正数通过补码器就一下得到取反的结果,电路图如图2.9所示:

图2.9 6位有符号补码阵列乘法器电路图

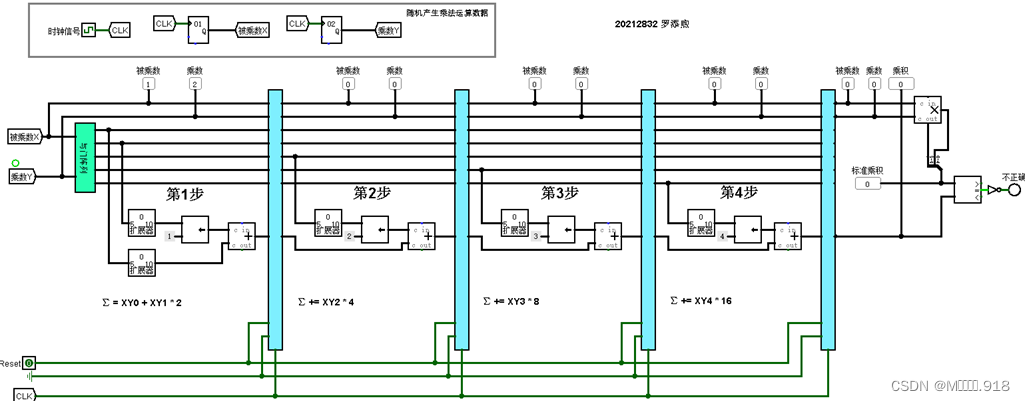

第8关:乘法流水线设计

当前的电路需要使用扩展器把5位的数据扩展为十位的因为乘法出来的结果为10位,我们只需要按照下面的公式就可以画出电路图,当然下面的公式中的乘2运算是使用左移来实现的。

⭐

∑ = XY0 + XY1 * 2

∑ += XY2 * 4

∑ += XY3 * 8

∑ += XY4 * 16

电路图如图2.10所示:

图2.10 乘法流水线电路图

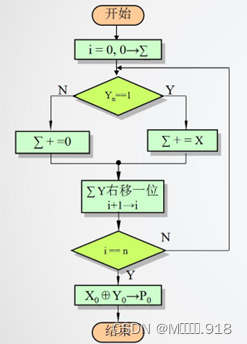

第9关:原码一位乘法器设计

原码一位乘法流程如图2.11所示:

图2.11 原码一位乘法流程图

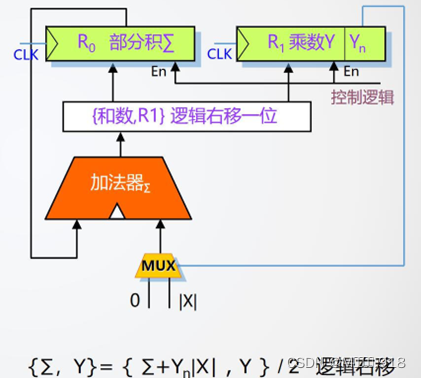

原码一位乘法的硬件逻辑如图2.12所示:

图2.12硬件逻辑图

所以设计思路如下:

- 由原码一位乘法可知,乘数依次从最低位乘以被乘数,然后和部分积进行累加。

- 因为乘数每次用完最低位后就不用了,所以我们可以右移一位,将最低位丢掉。

- 在进行累加时,因为每次做完乘法都是高一位的,所以我们把部分积右移一位,这样就可以实现对齐。另外,丢掉的那一位可以存在乘数寄存器的最高位,这样每次右移丢掉的一位都在最前列。在运行8次后,第一次丢掉的刚好到达最低位。

- 乘法部分如果Yi = 0,则结果为0,如果Yi = 1,则结果为X。可知乘法可以用数据选择器实现。对运算次数进行控制,在第0次运算时,把Y载入乘数寄存器中。在第8次运算后停止运算。因为是无符号数运算,所以不需要考虑符号位。

由以上的思路我们可以得到电路图如图2.13所示:

图2.13 无符号一位乘法器电路图

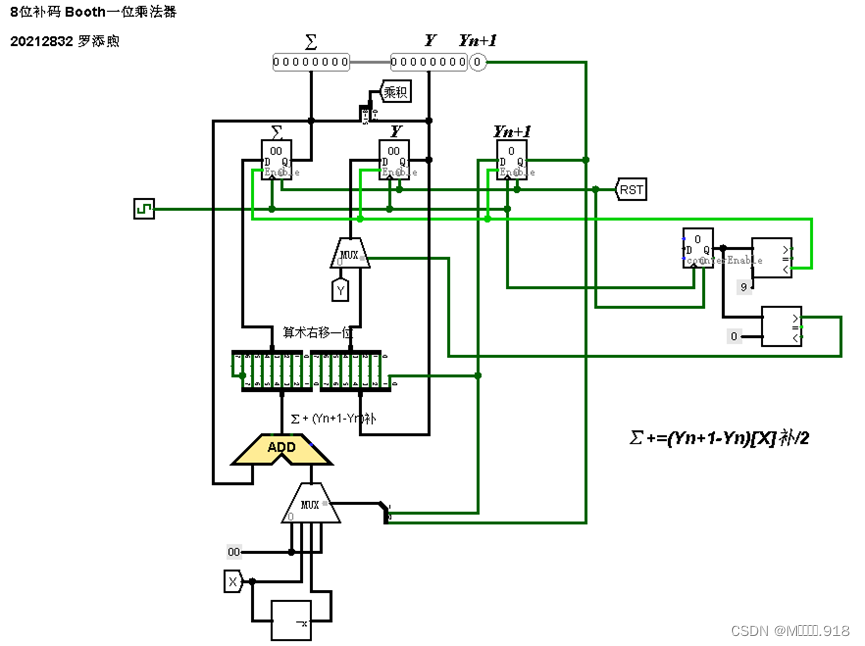

第10关:补码一位乘法器设计

补码一位乘法器流程图如图2.14所示:

图2.14 补码一位乘法器流程图

补码一位乘法器硬件逻辑如图2.15所示:

图2.15 补码一位乘法器硬件逻辑图

设计思路:

- 如果yn=yntl,局部积[zi〕加0,再右移一位:

- 如果ynt1=01,局部积加[x ]补,再右移一位:

- 如果yn ynt1=10,局部积加[-×]补,再右移一位:这样重复进展退1 步,但最后一步不移位。包括一位符号位,所得乘积为 2n+1 位,其中口为尾数位数,设计一个二输入三选一选择器对可能的三种情况进展选择。中选择器中输入为 YiYi+1为00 或者11时,由一存放器一端接 GND,另一端对其进展零输入中选择器中输入为 Yi Yit1 为01时,对其进展[x]补输入:中选择器中输入为 YiYit1为10时,对(X补输入端加一非门和一加法器对其进展取反加1输入。输出结果与一个一端接GND 初始署零的存放器相连接于一个加法器,实现局部积加法运算:计算结果存放于两个一样的移位存放器中,当局部积相加之后,由两个移位存放器同时对局部积的和进展移位操作。最后由两个移位存放器的输出端连接至选择器重新选择进展循环操作,直到局部积移位完。

用上述思路设计出来的电路图如图2.16所示:

图2.16 补码一位乘法器

第11关:MIPS运算器设计

设计思路:

先构造出每一种功能的输出,再根据OP的值来选择输出:

0~2:分别用一个移位器实现,设置对应的属性;

3~4:分别用自带的乘法器、除法器实现;

5:加法,用封装好的32位加法器,OF判断最高位进位和符号位进位是否一致,UOF判断是否有进位(需一个异或门),C0取0;

6:减法,用封装好的32位加法器,Y取反用一个非门实现,无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断,C0取1;

7~10:分别用与门、非门、异或门、或非门实现;

11:比较器用补码型,结果0拓展;

12:比较器用无符号型,结果0拓展,还需要一个equal信号;

都构造好之后,根据OP的值输出resualt。

具体电路图如图2.17所示:

图2.17 MIPS运算器电路图

cric文件的下载地址如下:有需要的自行下载噢!🌹🌹🌹🌹

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)