74138,74139,7447,74147,74151,74153

工作原理:选通端S1,S2',S3'为100时可将地址端A0,A1,A2的二进制编码在Y0'~Y6'对应的输出端以低电平输出。工作原理:1S',2S'为选通端,低电平有效。A0,A1为译码地址输入端,Y0'~Y3'为低电平输出端。

注:

74HCxxx是74LSxxx同序号的翻版,型号最后几位数字相同,表示电路的逻辑功能、管脚排列完全兼容。

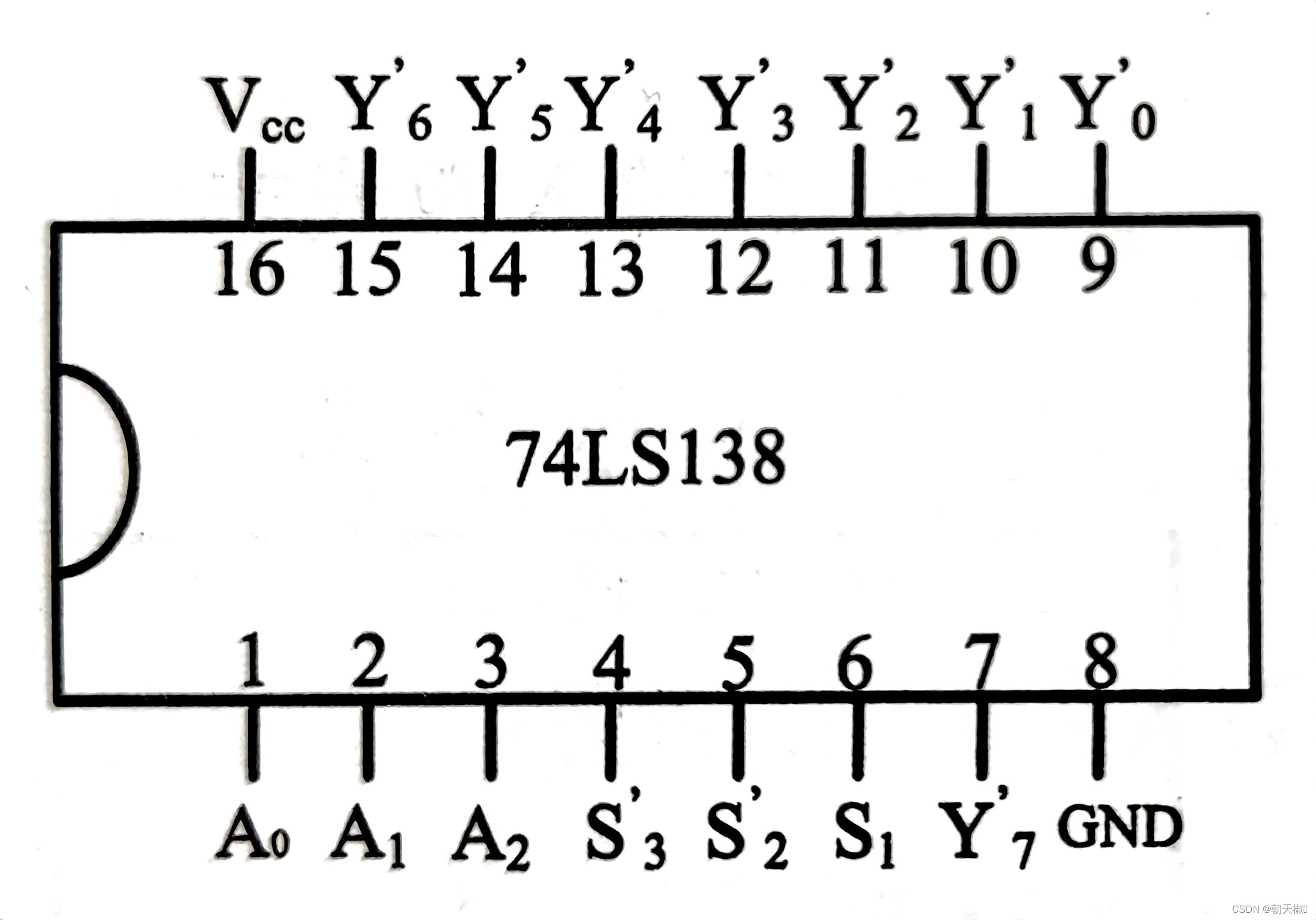

一、74LS138(3-8译码器)

1、引脚图

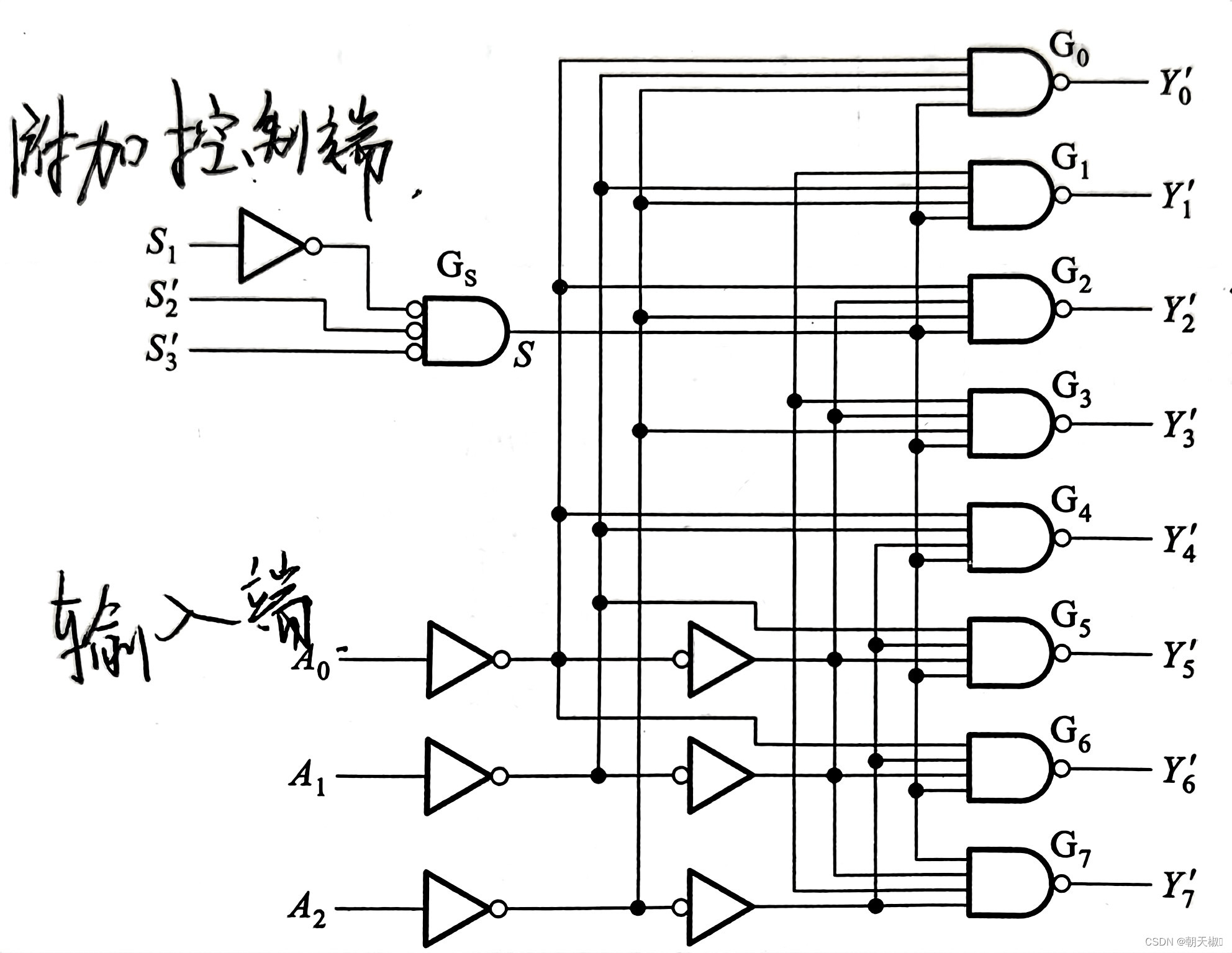

2、内部逻辑图

3、工作原理

附加控制端(又称“片选”输入端)S1、S2'、S3'为100时,Gs输出为高电平(S=1),译码器处于工作状态,可将地址端A2,A1,A0的二进制编码在Y0'~Y7'对应的输出端以低电平输出。否则,译码器被禁止,所有的输出端被封锁在高电平。

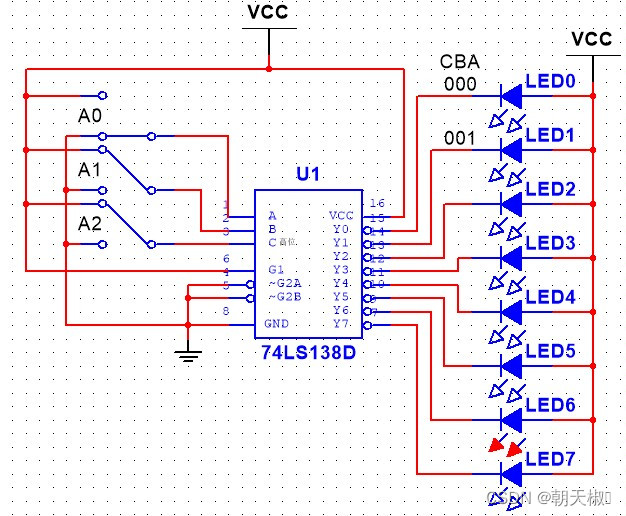

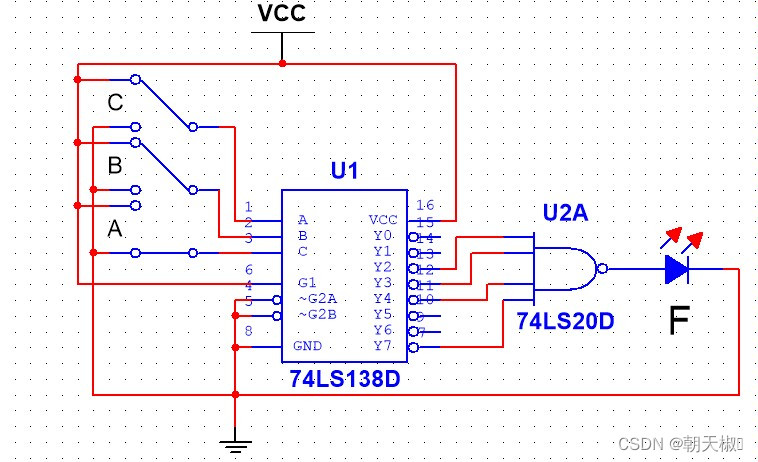

例:A2A1A0为110时,Y6'为低电平,共阳极LED6被点亮,仿真如下:

4、数据分配器

若将S1作为“数据”输入端(同时S2'=S3'=0),而将A2A1A0作为“地址”输入端,那么从S1输入的数据只能通过由A2A1A0所指定的一根输出线送出去。

例如:A2A1A0=101时,门G5的输入端除了接至Gs输出端的一个以外全是高电平,因此S1的数据以反码的形式从Y5'输出,而不会送到其他输出端。

5、例题

用3-8译码器实现函数F=A'B+BC+AB'C'

F=A'BC+A'BC'+ABC+AB'C'

=m3+m2+m7+m4

=(m3'·m2'·m7'·m4')'

仿真如下:

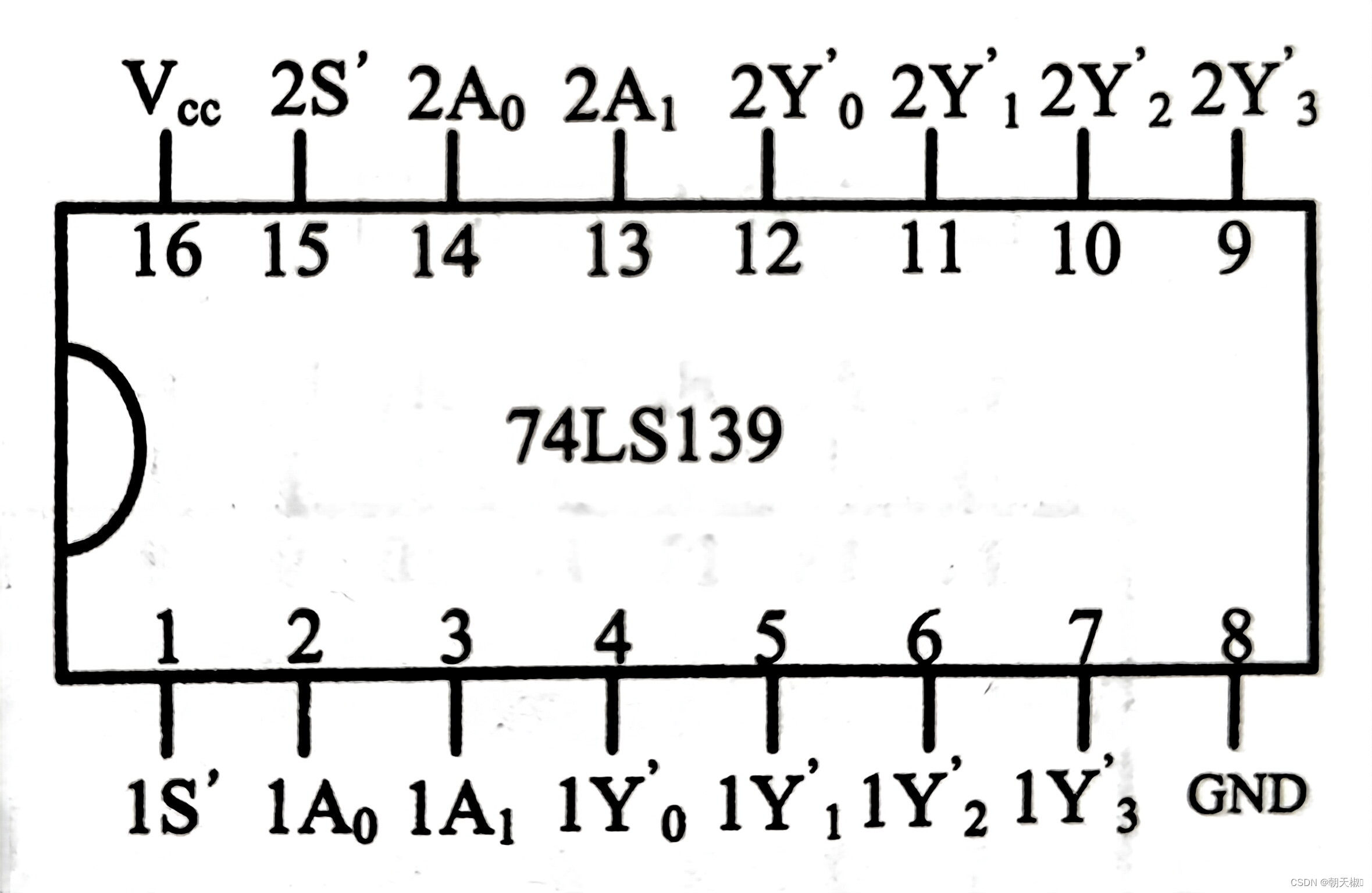

二、74LS139(2-4译码器)

1、引脚图

2、真值表

3、工作原理

1S',2S'为选通端,低电平有效。A0,A1为译码地址输入端,Y0'~Y3'为低电平输出端。

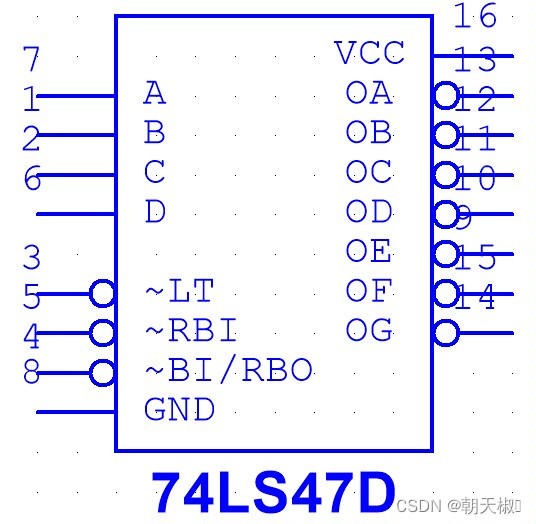

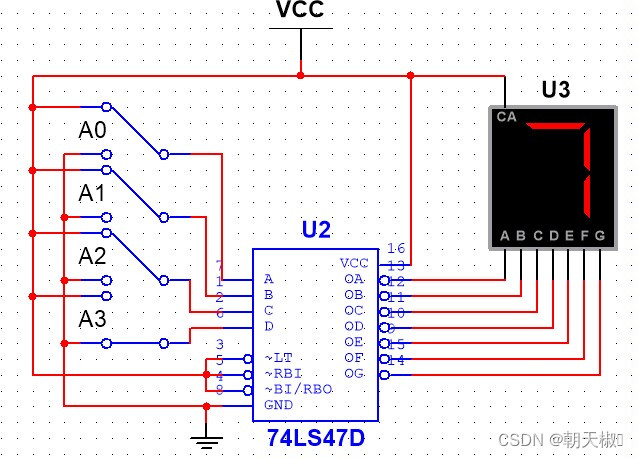

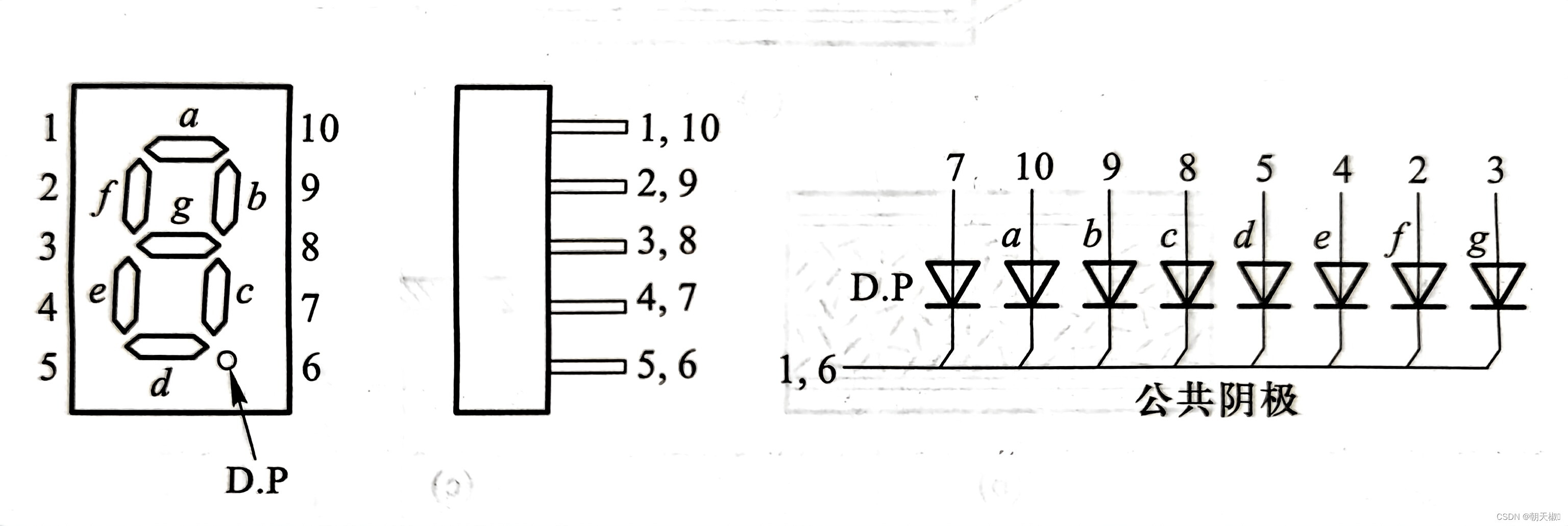

三、74LS47译码器驱动7段共阳极数码管

1、引脚图

2、真值表

3、工作原理

将输入端A,B,C,D的二进制编码转换成十进制在数码管输出。例A3,A2,A1,A0为0111,数码管显示7。

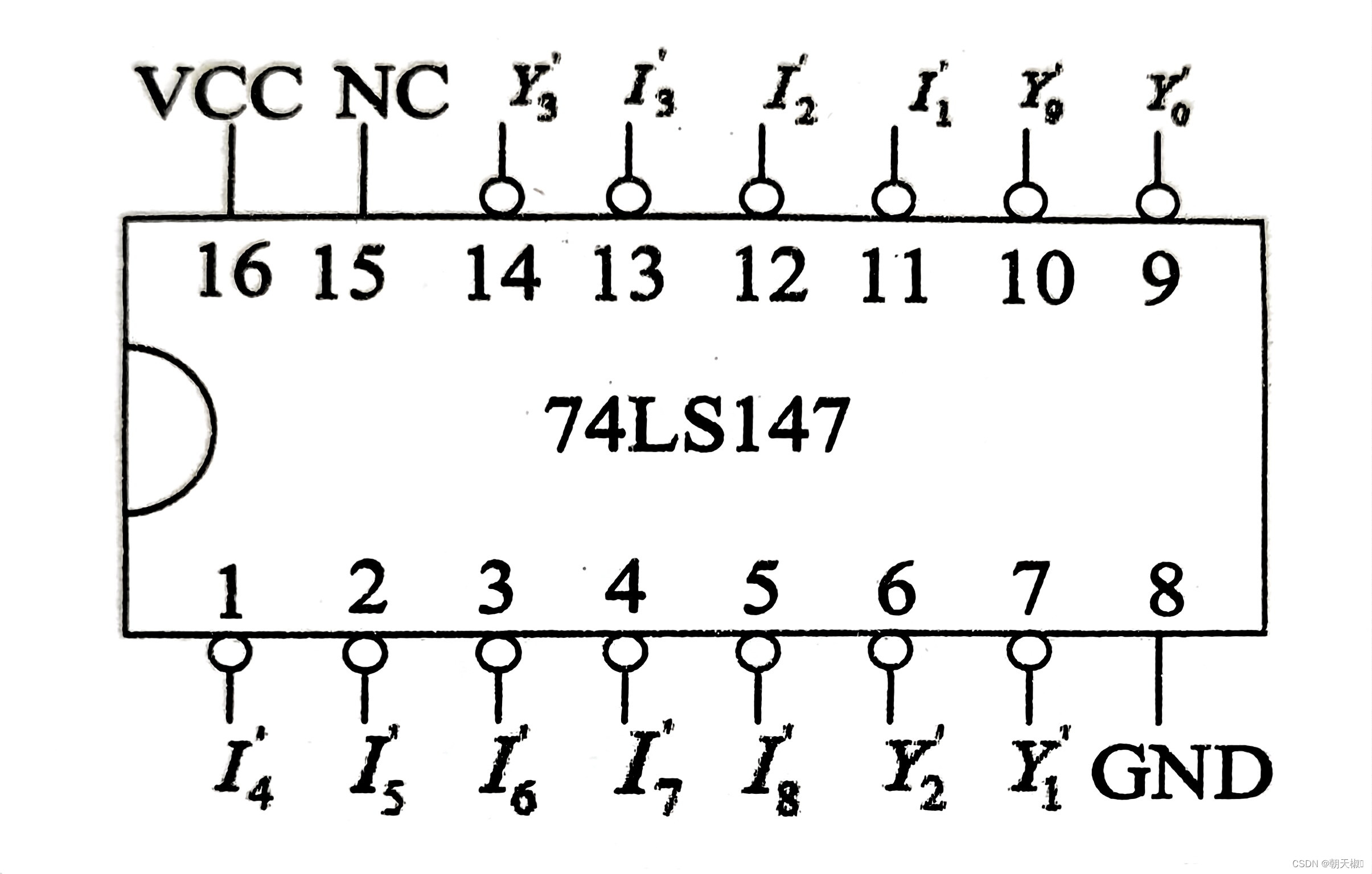

四、74LS147(二——十进制优先编码器)

1、引脚图

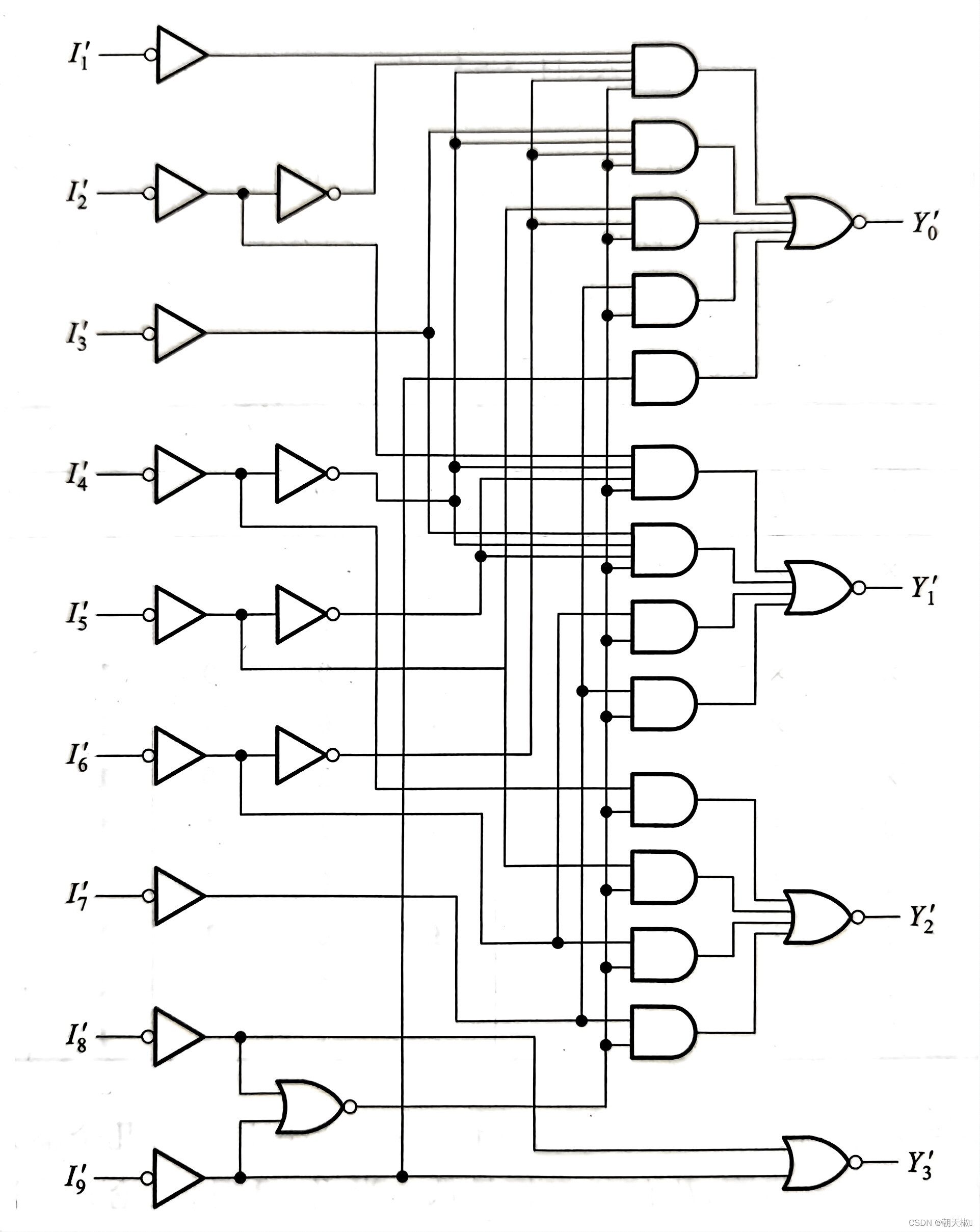

2、内部逻辑图

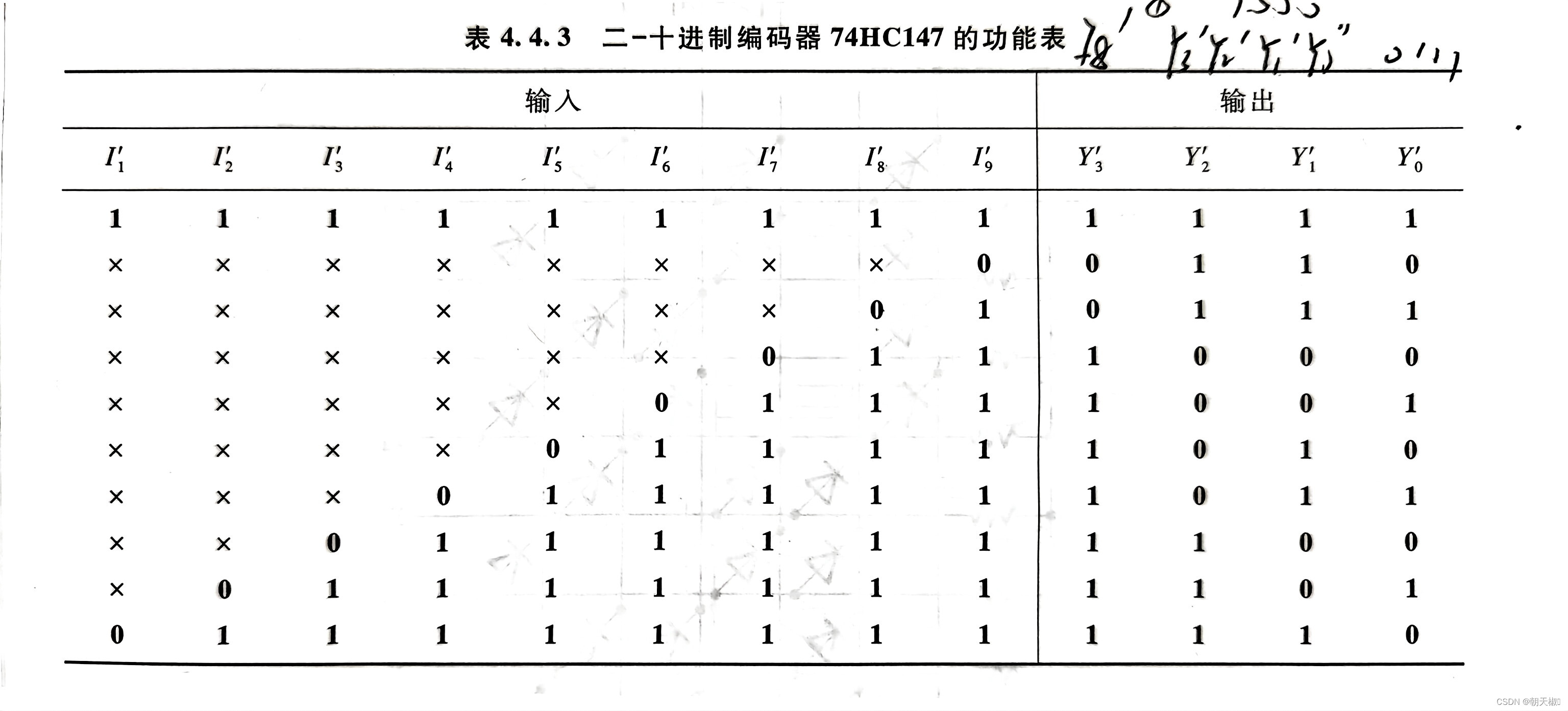

3、真值表

由表可知,编码器的输出是反码形式的BCD码。优先权I9'最高,I1'最低。当I1'~I9'均为无效输入(均为1)时,隐含表示了I0'为有效输入,编码输出Y3'Y2'Y1'Y0'=1111。

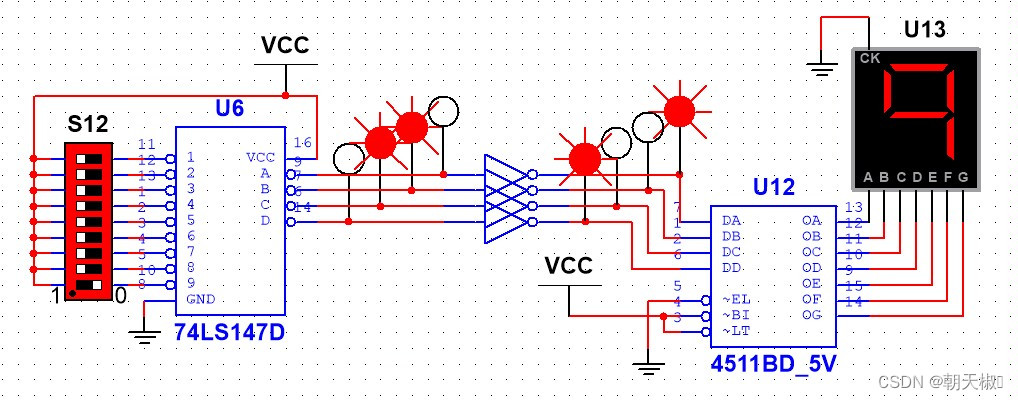

4、4511BD译码,点亮共阴极数码管

ls147输出端ABCD依次对应下图A0'A1'A2'A3'

上面仿真图74LS147输入I9'为0,其余引脚为任意电平(此处置1)时输出为0110,经非门转为1001,又经4511BD输出至数码管显示9(8+0+0+1)。

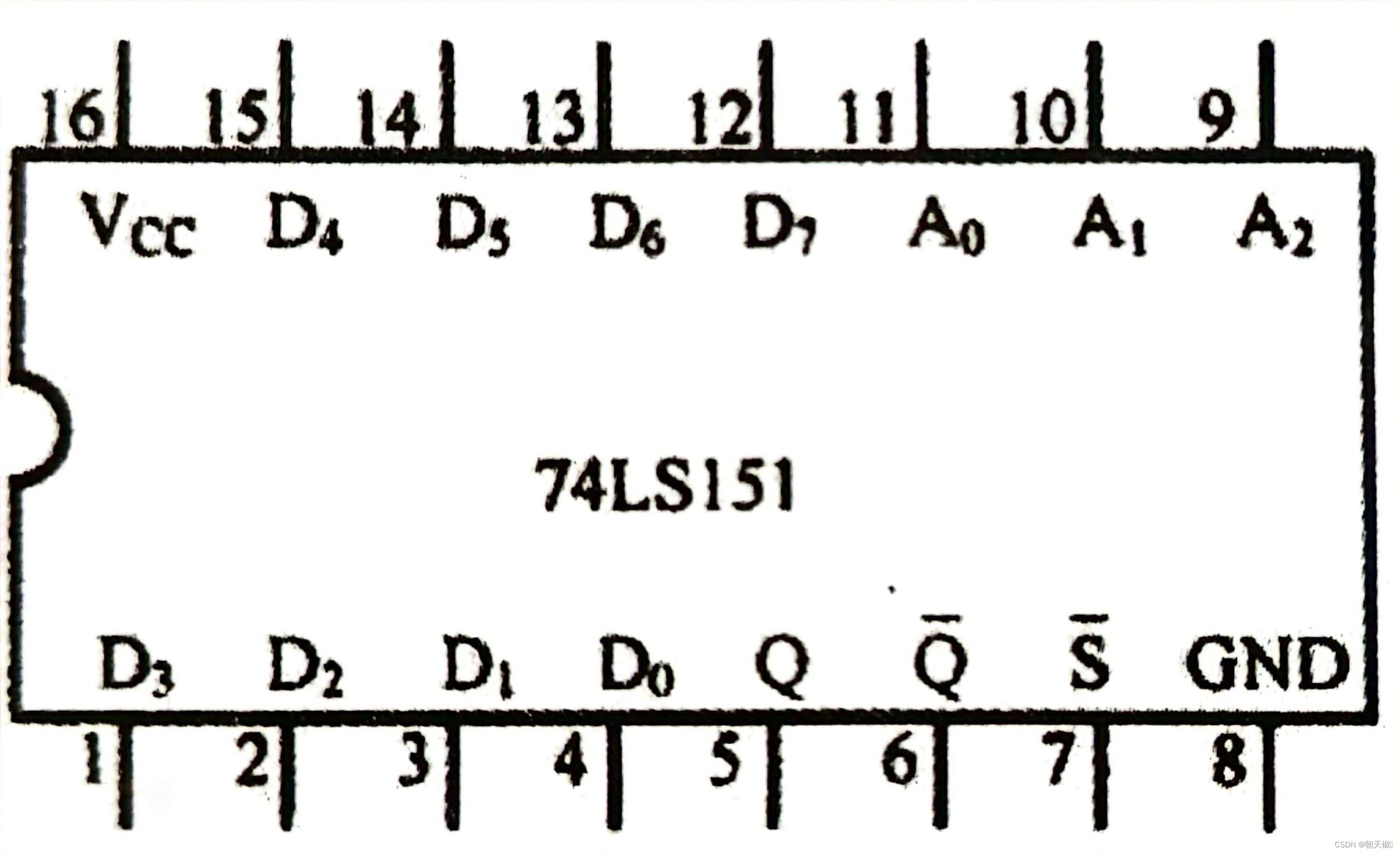

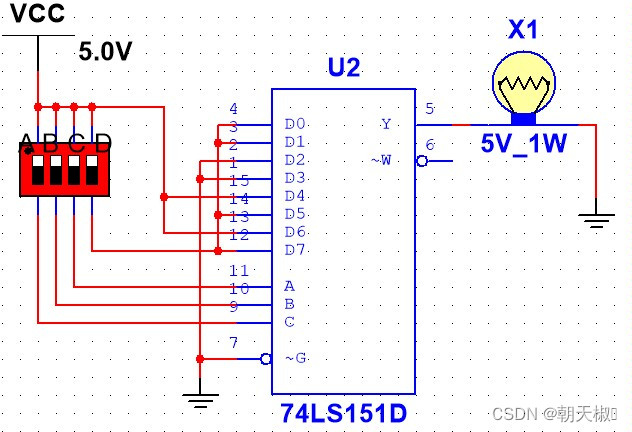

五、74LS151(8选1数据选择器)

1、引脚图

2、引脚功能

S为使能端(低电平有效);A2A1A0为地址输入端;D0~D7为8选1数据选择器的数据输入端;Q为数据输出端,Q'为反码数据输出端。

3、输出逻辑式

Y=S'[(A2'A1'A0')D0+(A2'A1'A0)D1+(A2'A1A0')D2+(A2'A1A0)D3+(A2A1'A0')D4+(A2A1'A0)D5+(A2A1A0')D6+(A2A1A0)D7]

4、例题

用74151实现函数F=ACD+B'D+AC'

化为最小项F=ABCD+AB'CD+A'B'CD+A'B'C'D+AB'C'+ABC'对比输出逻辑式,

ABCD对应(A2A1A0)D7,D7=D;AB'CD对应(A2A1'A0)D5,D5=D;A'B'C'D对应(A2'A1'A0')D0,D0=D;其余同理。

最后得出D0=D1=D5=D7=D,D4=D6=1,D2=D3=0。

仿真如下:

注意:ABCD中A为最高位,应该接芯片最高位C脚,其余同理。

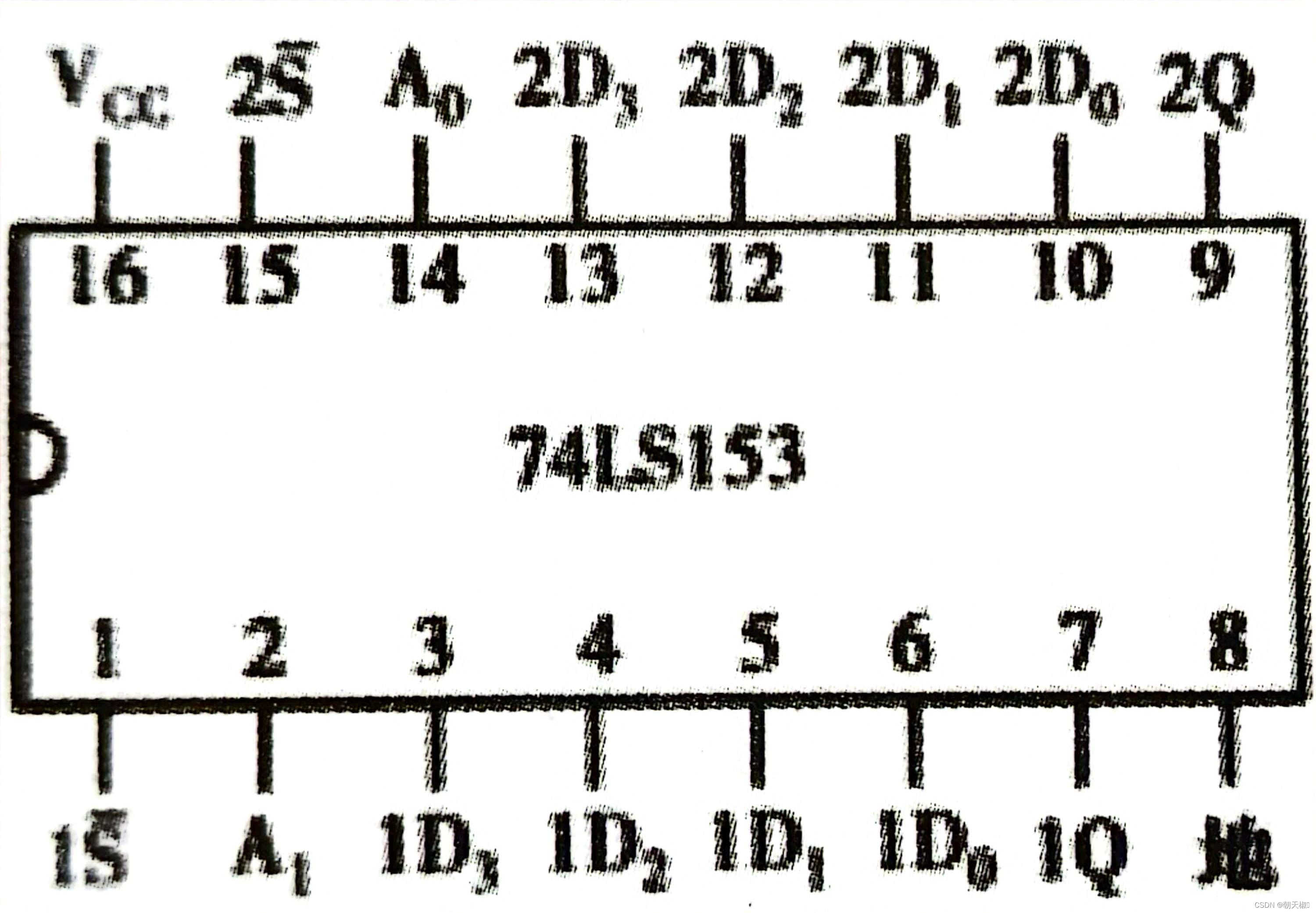

六、74153

1、引脚图

2、引脚功能

1S、2S为两个独立的始能端(低电平有效);A0、A1为公用地址端;1D0~1D3和2D0~2D3分别为两个4选1数据选择器的数据输入端;1Q、2Q为两个输出端。

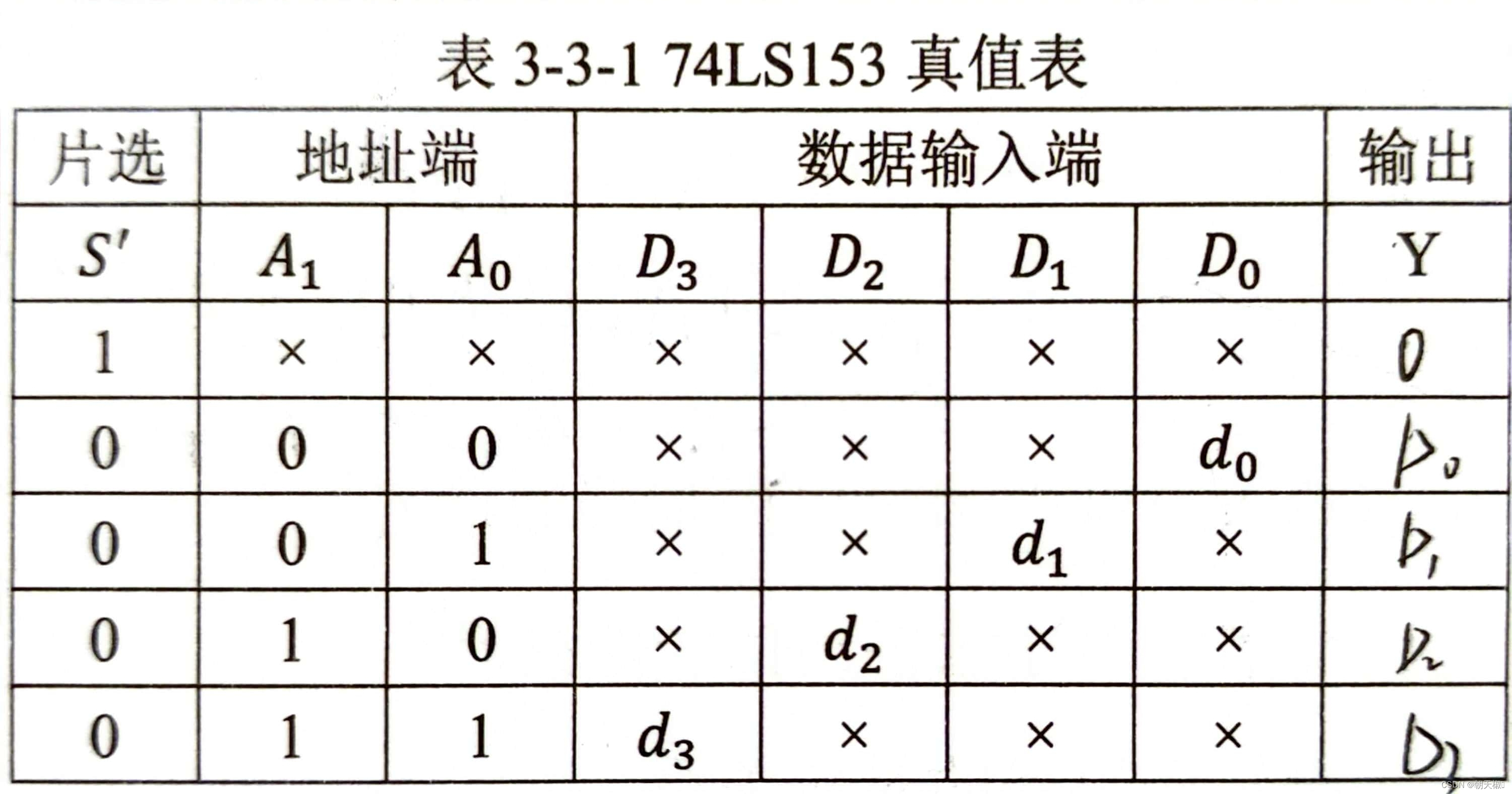

当使能端1S和2S=1时,多路开关被禁止,输出Q=0。当使能端1S或2S=0时,1D0~1D3或2D0~2D3输入有效(1S=2S=0,则均有效),根据地址码A1、A0(注意顺序,高位在前)的状态,将相应的数据D0~D3送到输出端Q。A1A0=00则选择DO数据到输出端,即Q=D0;A1A0=01则选择D1数据到输出端,即Q=D1,其余类推。

3、真值表

4、输出逻辑式

Y=S'[D0(A1'A0')+D1(A1'A0)+D2(A1A0')+D3(A1A0)]

5、例

1G=2G=0,数据输入端均有效,BA=00则选择C0到输出端,即1Y=1C0=1,2Y=2C0=1,两个LED均被点亮。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)