VSCODE-Verilog开发插件/(代码格式化+Verilog文件树显示+一键例化+UCF转XDC+代码错误检查+语法高亮)

实现verilog代码格式化功能,一件例化功能,例化的代码自动复制到剪切板,ucf转xdc文件:语法高功能:ucf语法高亮,xdc语法高亮,verilog语法高亮,高云.cst语法高亮。,verilog代码常用片段。verilog代码定义变量悬停显示。代码错误检查.

VSCODE插件 verilog-hdl-farmat /FPGA开发插件/Verilog开发插件/Verilog文件树

VSCODE插件,可实现功能:

功能总结

Verilog 代码格式化

- 变量对齐

- 逗号对齐

- 括号对齐

- 快捷键:CTRL + L

一键例化功能

- 例化的代码自动复制到剪切板

- 快捷键:ctrl+shift+p :输入 Convert_instance

UCF 转 XDC 文件

- 正常顺序转换

- 可实现序号的从小到大的排列

- 快捷键:ctrl+shift+p :输入 Convert UCF to XDC NORMAL ORDER 或 Convert UCF to XDC SORT ORDER

语法高亮

- ucf, xdc, do, tcl 语法高亮

- Verilog 语法高亮

- 高云 .cst 语法高亮

Verilog 代码常用片段

Verilog 代码定义变量悬停显示

代码错误检查

- 加入 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 的 linter(Verilog 语法检测)功能

Vivado 仿真文件的快速转换功能

- 进入 Vivado 工程下的 sim_1\\behav\\questa(或者 modelsim)里面运行命令 Convert Modelsim do 则会把 xxx_compile.do, xxx_elaborate.do, xxx_simulate.do 和加入用户自定义配置文件生成一键运行的 tb.do 文件

incrementSelection 的功能

- 使用多个游标进行递增、递减或反向选择

加入了 Verilog 文件树显示功能

- 需要命令 Find Verilog Modules 触发和刷新

前言

- 注意🔴:高亮代码的时候需要切换颜色主题为:深色+

- 如果出现报错,可您呢个是因为你的VSCODE版本低了,请更新最新版本,本插件除了代码检查需要使用外部环境外,其他不需要额外的配置.代码检查请参考Verilog-HDL/SystemVerilog/Bluespec SystemVerilog的详细配置.

- 提升🟢:整个插件是为了方便FPGA开发写的插件功能,其中部分功能是参考了插件市场的,部分是自己觉得需要写的功能.如果大家有好的修改意见或者使用问题,请给我留言. 🐧QQ:1391074994 🐧QQ裙: 819816965

- 如果好用,请记得给个好评😘😘😘.

功能

- 实现verilog代码格式化功能(变量对齐,逗号对齐,括号对齐),加入位宽配置功能。功能触发:按下 ctrl+shift+p :输入 verilog。 快捷键 CTRL + L;

- 一件例化功能,例化的代码自动复制到剪切板。功能触发:按下 ctrl+shift+p :输入 Convert_instance。

- ucf转xdc文件:

- 正常顺序转换。 功能触发:按下 ctrl+shift+p :输入 Convert UCF to XDC NORMAL ORDER。

- 可实现序号的从小到大的排列。 功能触发:按下 ctrl+shift+p :输入 Convert UCF to XDC SORT ORDER。

- 语法高功能:ucf,xdc,do,tcl语法高亮,verilog语法高亮,高云.cst语法高亮。

- verilog代码常用片段。

- verilog代码定义变量悬停显示。

- 代码错误检查:加入Verilog-HDL/SystemVerilog/Bluespec SystemVerilog的linter(verilog语法检测)功能

- vivado仿真文件的快速转换功能 :进入vivado 工程下的sim_1\behav\questa(或者modelsim)里面运行命令Conver Modelsim do 则会把 xxx_compile.do,xxx_elaborate.do,xxx_simulate.do和加入用户自定义配置文件生成一键运行的tb.do 文件.

- 操作范例:bilibi 示范链接

- 演示文档链接:CSDN演示文档链接

功能详细介绍

-

verilog代码格式化: 按下 ctrl+shift+p :输入 verilog 或者 快捷键 CTRL + L;

gif:

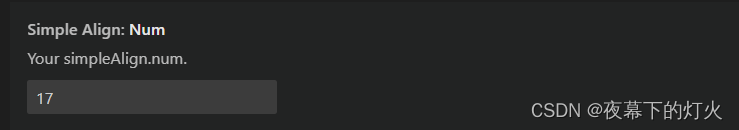

加入位宽配置功能:

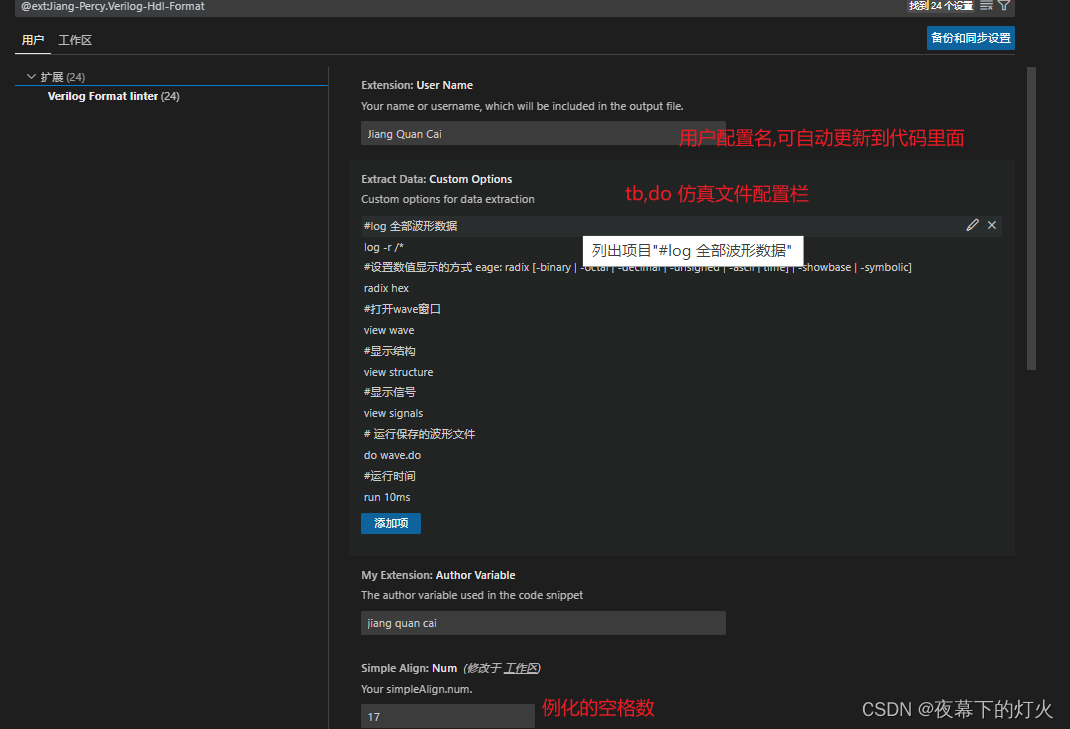

默认是17 当前面的变量名很长的时候,会出现后面对不齐的情况,可以适当加大整个数值,使之对齐. -

例化功能:

可以一键实现当前打开的Verilog文件例化功能,并且复制到剪切板里面,可以之家粘贴.

gif:

-

ucf转xdc文件:

-

正常顺序转换 :gif:

-

序号的从小到大的排列转换:gif:gif

-

-

语法高功能:ucf语法高亮,xdc语法高亮,verilog语法高亮,高云.cst语法高亮:

gif:高亮gif -

代码片段:支持输入的代码片段: | module | geli | jishuqi | shangshenyan | tb | zhuangtaiji | always | dapai | assign | alwaysposclk | alwaysnegclk | begin | end | initial | case | reg | regarray | regmemory | wire | wirearray | array | parameter | localparam | integer | signed | include | def | ifdef | ifndef | elsif | endif | undef | ts | default_nettype | ternary | if | ifelse | for | while | forever | function | generate |genvar

其中 比较常用的部分:module/geli/jishuqi/shangshenyan/tb/zhuangtaiji/always/dapai

gif:

-

verilog代码定义变量悬停显示:

gif:

-

代码错误检查:

gif:

-

tb.do 配置

VIVADO 联合仿真进去modelsim后 进入仿真文件夹 配置合并生成一键仿真文件.

VIVADO -modelism 仿真生成一键 tb.do

-

Setting配置项:

*

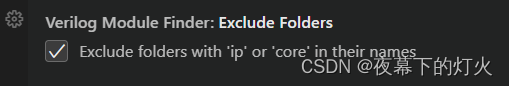

- 文件树显示

可以显示verilog的层次结构文件树功能,如果打开的文件夹里面有IP文件的话,在setting里面做了屏蔽操作

默认是勾选,则不会识别名称为"ip"或者"core"下面的verilog代码,避免显示许多的顶层文件.

Thanks

ENGLISH

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)