DDR中的Training?

最近不是在看启动吗?里面总是有个DDR Training,就很纳闷这是个啥。但是一百度实在是没找到。不小心今天找到了一篇前辈的文章,这我不得马上去整来学习一下。有人说BIOS程序就是按照硬件手册和根据用户选择填寄存器,几张表就能解决的事为什么要这许多程序呢?虽然数千个选择形成的组合爆炸让穷举表成为不可能,但它也道出了BIOS大部分程序的实质:填写寄存器。有一个声音发出了不同意见,在BIOS程序里面

https://zhuanlan.zhihu.com/p/107898009

前言

最近不是在看启动吗?里面总是有个DDR Training,就很纳闷这是个啥。但是一百度实在是没找到。不小心今天找到了一篇前辈的文章,这我不得马上去整来学习一下。链接在最开始,感谢大佬的优秀文章。

有人说BIOS程序就是按照硬件手册和根据用户选择填寄存器,几张表就能解决的事为什么要这许多程序呢?

虽然数千个选择形成的组合爆炸让穷举表成为不可能,但它也道出了BIOS大部分程序的实质:填写寄存器。

有一个声音发出了不同意见,在BIOS程序里面,长期居住了一个另类,他的名字叫做MRC:内存参考代码。他的任务就是初始化内存,而他却管自己叫做Memory Training代码,主打的是调整时序和提高信号完整性。好高级的名字:Training,训练,似乎和人工智能有关?

当然不是,但和AI 模型的training之所以取名如此一样,都是为了通过实验来寻找可以解决问题的方案。Deep Learning的Training得到神经网络的权重矩阵;

而Memory Training得到一组对齐、补偿和参考电压参数,来平衡和对冲线路的差异和信号的噪声。

如果我们查看Intel的BIOS的代码,会发现MRC代码量很大。而它所以另类因为它是唯一与模拟信号和信号完整性打交道的地方,大量的采样、眼图代码让它与众不同。ARM和AMD则没有如此大量的Memory Training代码,这是为什么呢?内存不Training行不行?

内存为什么要Training?

内存I/O部分频率越来越高,如此高的频率让小小的一点误差都会被放大。熟悉主板布线的同学应该知道高速信号布线的时钟约束十分严苛,一组高速信号在主板上拐个弯,内圈和外圈的走线长度会产生差距,尽管很小,低速信号没关系,但高速信号时钟约束就达不到,必须在相反的方向拐回来补偿一下。

内存I/O频率上G的频率,让任何细小的误差都必须得到补偿,所以要在整个数据链路进行对齐和补偿。

一个比较完整的内存访问链路包括了很多部分:

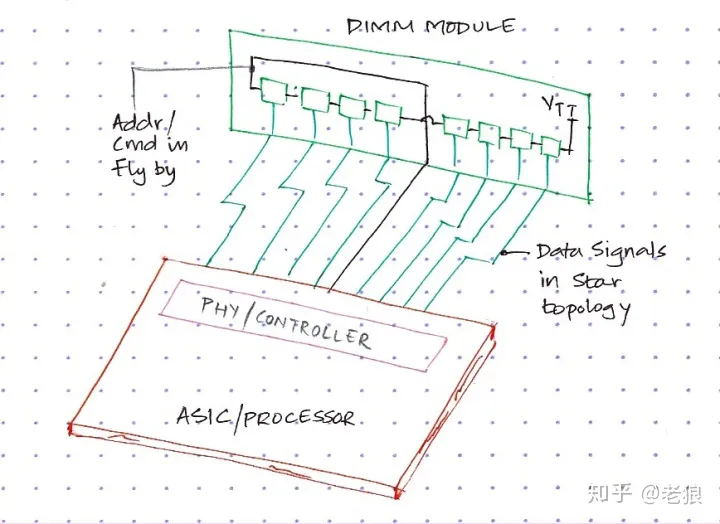

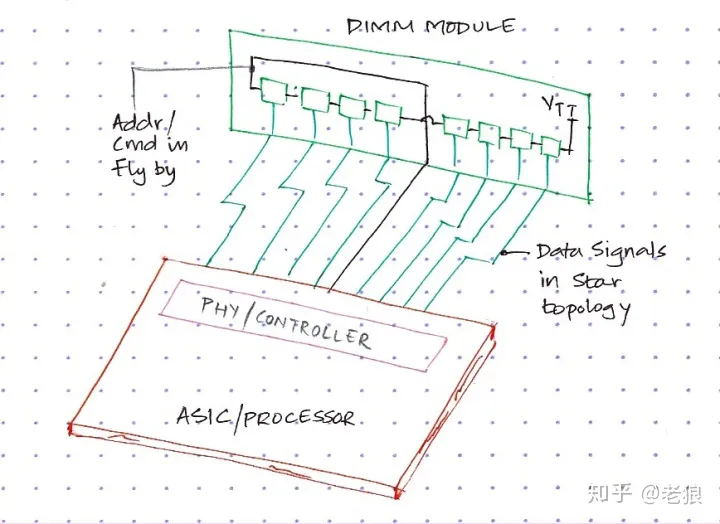

从源头开始包括MC (内存控制器,memory Controller)、PHY(MC和PHY有些在一起,很多是分离设计来增加灵活性);从Pitch到pin,再从pin穿过主板到达slot的布线;slot过金手指通过fly-by或者直连到内存颗粒;内存颗粒中到内存Cell。

这么长的链条每个点都有可能引入时钟不同步和采样延迟的问题,所以要在各个部分分别对齐,让内存DIMM的上百条连线整齐划一。(DIMM是内存插槽的类型。 DIMM全称Dual-Inline-Memory-Modules,中文名叫双列直插式存储模块)

这其实是内存初始化对齐大步骤共十几个的末尾部分。

- 对齐和补偿要从芯片内部开始,当芯片出口好了,

- 再对齐DCA、DCS(因为下面的步骤需要下command);

- 再是jedec spec里面的Read Leveling,read DQS/DQ;

- 再下来才是Write Leveling,和write DQS/DQ。

- 为了信号好,还要匹配RON和ODT电阻,

- 以及通过调整vRef来让眼图眼睛张开,并寻找安全和合适的采样点。

- DDR5因为速度太高,还要加入DFE等均衡器来提高信号完整性:

这些步骤还不包括RDIMM要求的backside training和LRDIMM的 DB到颗粒的额外Training步骤,所以服务器内存初始化更加繁杂的多。

谁来进行Training?

这些步骤大部分是所有内存方案都要做的,包括焊在板子上的Solder Down方案和不同的内存控制器。关键是谁来执行这些步骤,谁来Training整个命令和数据链条。

有两种方案:In Band和OOB(Out Of Band)。大家经常在通信领域听到band概念,这里没有通信调制,还提band是怎么个意思呢?其实这种说法在silicon技术文档里面经常提到,这个所谓的band,是指CPU的计算资源,即CPU的Compute Bandwidth。

- In Band,就是CPU自己亲历亲为,自己完成任务;

- OOB是说不占用CPU资源,让别家完成,比较典型的是由一个MCU完成,当然完成过程中和过后还需要和CPU通过mailbox等机制互相交互。

OOB training十分常见,比大家认为的常见更加常见。现在几乎所有高速通信线路都需要Training,包括但不限于PCIe、USB、SATA等等。而完成这个Training的并不是CPU,可以是MCU和DSP等。

结论

好了,我们回到原来的问题:为什么Intel的MRC代码量很大,而ARM和AMD则没有如此大量的Memory Training代码?

相信同学们都已经有了答案。是的,Intel采用In Band training,而ARM和AMD采用OOB Training。

最后给大家留个思考题:这两种方式各有什么优缺点,为什么Intel采用In Band,而ARM和AMD采用OOB?

精彩的评论:

OOB的training sequencer集成在PHY里面,访问DRAM更快,所以training速度也快。

但由于第三方vendor的封闭性,开放的FW接口有限,所以不够灵活,后期兼容性调整比较费力。

arm总比intel先进,intel搞cpu时还没有mcu,后来积重难返,为了复用和兼容只好一条道走到黑。MRC是一段程序,程序执行需要ram,它是初始化ram的,ram未初始化之前是不能用的,先有鸡还是先有蛋,这代码写起来一定很纠结。

oob用mcu,mcu自带不用trainning的低速ram。

oob也只是让另外的固件去做初始化。不存在修代码更方便的说法吧。无论bios去做还是其他的去做,最后都要通过更新固件来更新内存training过程。

我看未必是技术上的问题。估计Intel的MC和PHY都是自己做的,用处理器training顺理成章,他自己也不做小mcu内核,更不太可能专门为training集成个第三方的小mcu;ARM,AMD系统,更有可能会采购第三方的MC/PHY,由IP设计方集成的方案自然更可靠和高效。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)