555计时器原理

555计时器原理一. 元器件部件:1. SR锁存器2. 运算放大器(运放)3. 半导体三极管(三极管)4. 滤波电路二. 实现原理一. 元器件部件:常见的555计时器内部构造大致由SR锁存器运算放大器(运放)半导体三极管(三极管)上述三个部分构成在实际应用中不可避免的要添加去耦电容以避免噪声对触发信号和阈值信号的影响。1. SR锁存器2. 运算放大器(运放)3. 半导体三极管(三极管)4. 滤波电

一. 元器件部件:

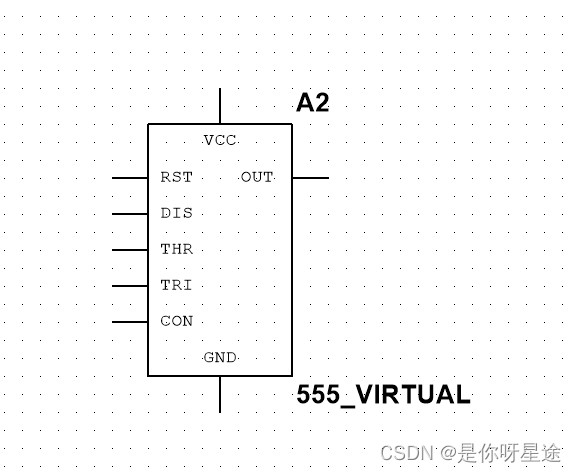

以Multisim上的555计时器为例:

555计时器包含八个引脚

分别为:

RST - Reset复位引脚(低电平有效)DIS - Discharge三极管集电极Collector输入引脚THR - Threshold上阈值电压引脚TRI - Trigger触发引脚CON - Control voltage1 电压控制引脚OUT - Output信号输出引脚VCCGND

555定时器内部功能图:

常见的555计时器内部构造大致由以下几个部分构成

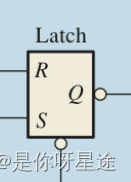

1. SR锁存器

- SR锁存器(

Latch)

锁存器逻辑符号:

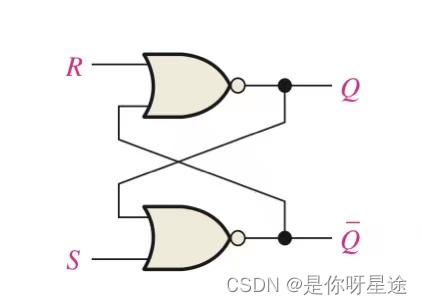

常见两种或非门

锁存器内部构造:

常见两种或非门

锁存器真值表:

| S输入 | R输入 | Q \mathsf{Q} Q输出 | Q ‾ \overline{\mathsf{Q}} Q输出 |

|---|---|---|---|

| 0 | 0 | NC | NC2 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Invalid | Invalid3 |

| S ‾ \overline{\mathsf{S}} S输入 | R ‾ \overline{\mathsf{R}} R输入 | Q \mathsf{Q} Q输出 | Q ‾ \overline{\mathsf{Q}} Q输出 |

|---|---|---|---|

| 1 | 1 | NC | NC2 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 0 | 0 | Invalid | Invalid3 |

原理:

向RS双端同时输入数据,初始状态有

Q

\mathsf{Q}

Q=0,

Q

‾

\overline{\mathsf{Q}}

Q=1。在该条件下沿着两个或门进行输入输出真值的判断。(注意:

Q

\mathsf{Q}

Q和

Q

‾

\overline{\mathsf{Q}}

Q真值关系一定相反),且注意此处不能存在S*R=1即S=R=1的情况,当出现此种情况时,对于:

(1)由状态S=R=0跳变到S=R=1的状态下,因为不存在S=R=1的独立状态需要判断是先达到S=0,R=1的状态还是先到达S=1,R=0的状态,对于这两种状态,无法判断是哪种,所以不能宏观确定SR锁存器的实际状态

(2)由状态S=R=1跳变到S=R=0的状态下,因为不存在S=R=1的独立状态需要判断是先达到S=0,R=1的状态还是先到达S=1,R=0的状态,对于这两种状态,仍无法判断是哪种,所以也不能宏观确定SR锁存器的实际状态

但对于这两种情况,其微观状态下还是唯一确定的,为了避免这种情况的发生,产生了SR锁存器的约束条件:

S*R=0

避免了无法由宏观唯一确定微观状态的情况

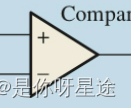

2. 比较器

- 比较器(Comparator)

比较器有两个输入端分别为正输入端和负输入端,分别记输入电压为Vin+和Vin-,比较两个输入端电压的大小

| 输入端电压关系 | 输出端Vout |

|---|---|

| Vin+>Vin- | 1 |

| Vin+<Vin- | 0 |

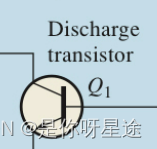

3. NPN型半导体三极管(三极管)

- NPN型半导体三极管(三极管)(NPN type triode)

三极管的内容其实还是比较多的,这里极其简单的介绍一下三极管的通断状态,以NPN型半导体三极管为例,三极管有三种工作状态。分别为:

截止状态:射极和集电极之间电流截断,没有电流流经

放大状态:通过集电极上的电流随着基极电流的增大而成倍增大(此时集电极和射极之间已处于导通状态)

饱和状态:通过集电极上电流达到饱和,集电极和射极之间呈现完全导通状态

如下图所示为NPN型半导体三级管

在555计时器中为

4. 滤波电路(*)

在实际应用中不可避免的要添加去耦电容以避免噪声对触发信号和阈值信号的影响。

二. 实现原理

555计时器的整体实现原理为反馈原理

通过三极管状态的不断翻转实现特定频率的输出

以其中一种接线方式为例

- 其中

RESET和Vcc引脚接入高电平使重置引脚失效 DIS - Discharge三极管集电极Collector输入引脚接入R1将R1上分压作为该引脚的输入值,根据该引脚的输入值不断切换三极管的通断状态THR - Threshold上阈值电压引脚同集电极引脚输入作用于比较器输出电平值到SR锁存器,同时接入电容作为充放电容器引起电压值改变TRI - Trigger触发引脚等待接入其他元器件,如果不接,则默认输入为高电平值作用于比较器输出到SR锁存器上CON - Control voltage电压控制引脚接去耦电容稳定电路GND接地

实现特定频率值的输出

原理如下:

- 初始状态:555计时器内部电阻上分压各为(1/3)Vcc,初始状态

Trigger触发引脚上输入为高电平(2)引脚高电平,(6)引脚低电平。在比较器作用下输出低电平,同时作用在SR锁存器上,输出为Q为低电平,再取非(可以看到输出处有取非符号-小圆圈)。一端将高电平输出到三极管上,使三极管处于导通状态,Vcc通过R1流经三极管接地;另一端取非输出低电平 - 向

Trigger触发引脚上输入低电平,同1. 理,在比较器和锁存器作用下节点处输出为低电平,分两端输出,一端使三极管处于截断状态,三极管集电极和射极之间没有电流流过,Vcc从R1作用在电容器上极板上,随着极板充电,在(6)引脚处电位逐渐升高,当该点电位大于(2/3)Vcc时,致使比较器输出高电平,此时(2)引脚回到低电平,SR锁存器输出高电平作用使三极管处于导通状态 - 电容器在(2.) 过程中充电,在三极管达到

导通状态后沿着如图所示路径逐渐放电,当放电完毕后回到(1. )状态并循环。每经历一个循环,输出一个完整波形(在达到(3. )状态时,和(1. )状态是同时进行的,且都不改变输出电平值)

注意到,这种接线方式下的555计时器仍然需要一个变化的输入值接入触发引脚才能实现固定频率的输出,而要实现555计时器“自给自足”,需要从555计时器中的电平变量中将输出作为Trigger触发引脚的输入值

如下图实现了555计时器的“自给自足”:

接入R2实现分压

将电容器上极板电位作为Trigger触发引脚输入电位,由只外接R1的555计时器工作过程,得知电容器极板上的电位会发生周期性变化,而这个周期受电容器的电容大小和两个电阻器R1和R2的阻值大小的影响,电容器上极板电位的周期变化作为输入等效于高低电平的周期变换过程,实现了555计时器输出固定频率的方波信号

对于输出的频率,遵循以下公式:

三. 图例引用

图0.1——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P421 FIGURE 7-52

图1.0——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P389 FIGURE 7-1

图1.1——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P389 FIGURE 7-2

图2.0——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P421 FIGURE 7-52

图3.0——模拟电路-P112 Figure 2.1 The npn BJT

图3.1——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P421 FIGURE 7-52

图4.0——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P421 FIGURE 7-53

图4.1——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P422 FIGURE 7-54

图4.2——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P425 FIGURE 7-56

图4.3——Thomas L. Floyd-Digital Fundamentals-Prentice Hall (2014)-P425 FIGURE 7-57

希望能够帮到迷途之中的你,知识有限,如有学术错误请及时指正,感谢大家的阅读

(^^)/▽ ▽\(^^)

更多推荐

已为社区贡献9条内容

已为社区贡献9条内容

所有评论(0)