vivado 第一个sdk工程

vivado 第一个sdk工程

·

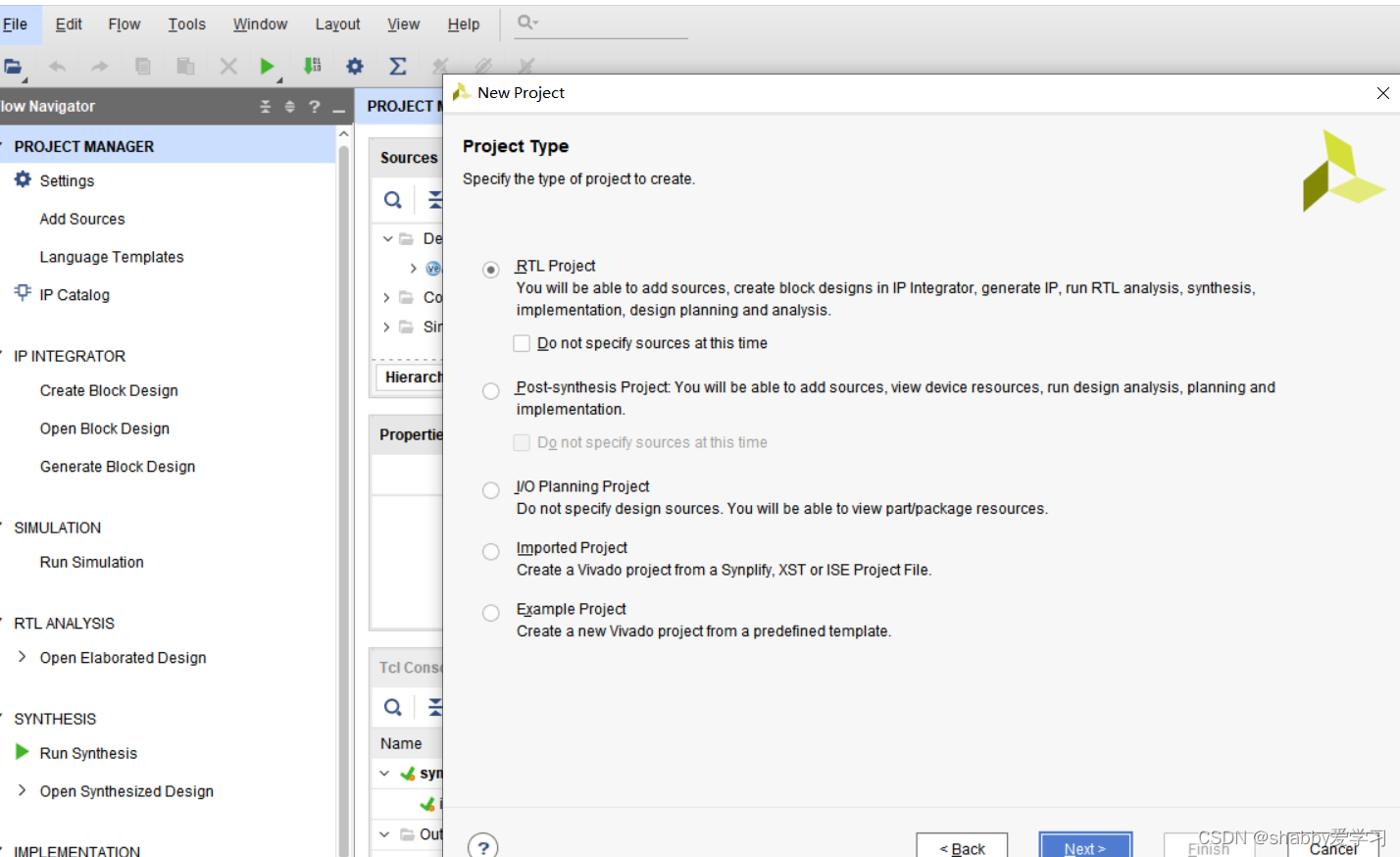

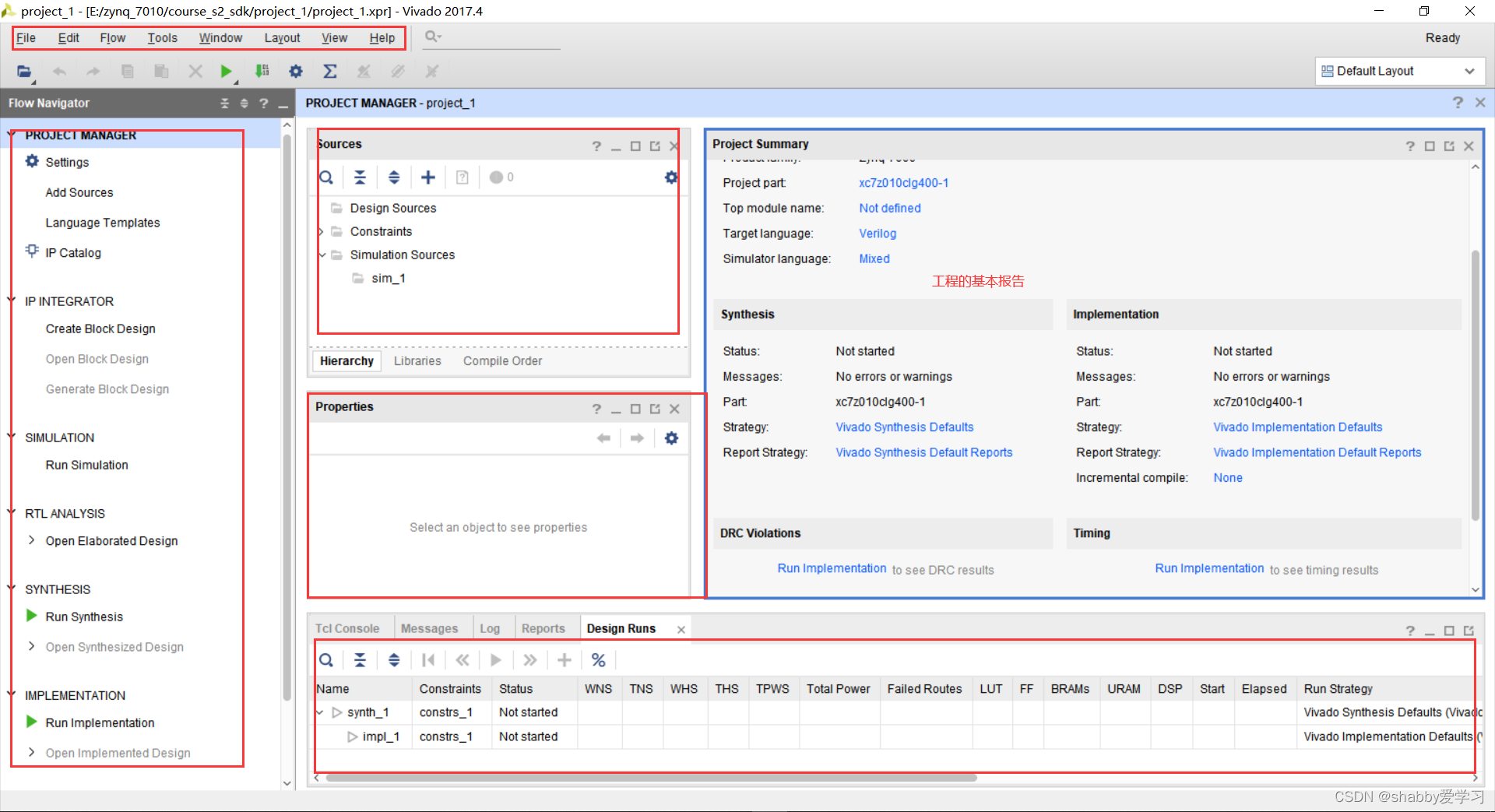

1.新建工程

- 第一个工程

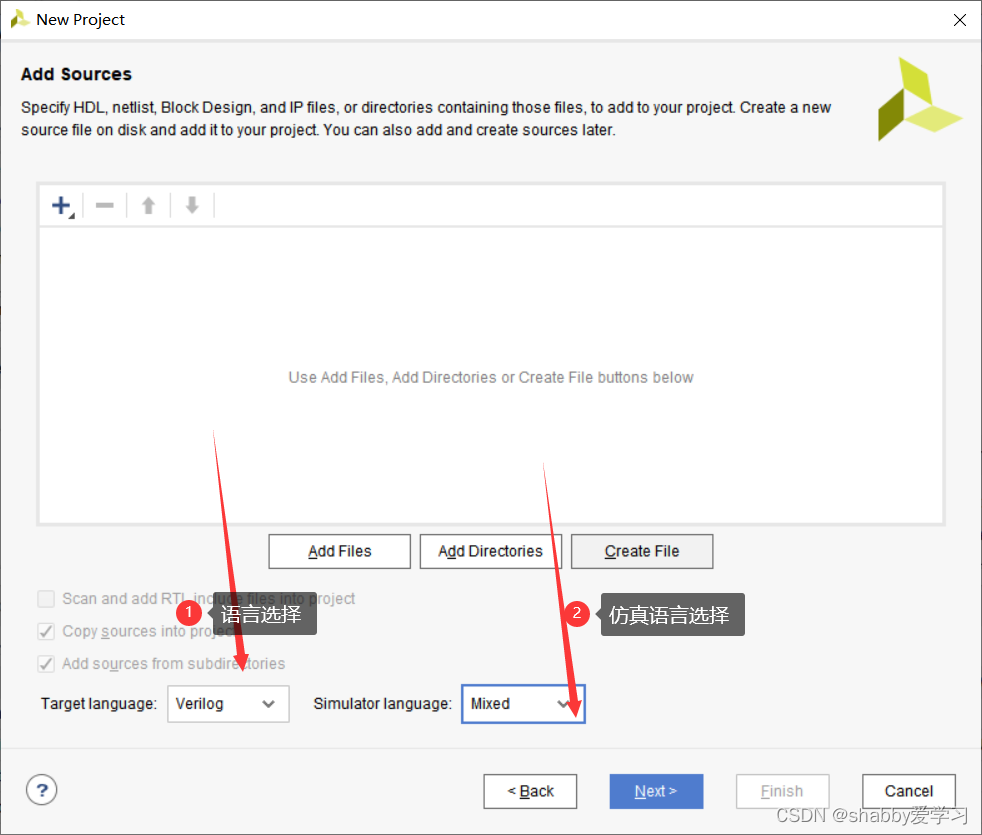

- 是否添加文件,如果有就添加,没有就next

- 约束文件,引脚约束,也可以图形化配置引脚模式

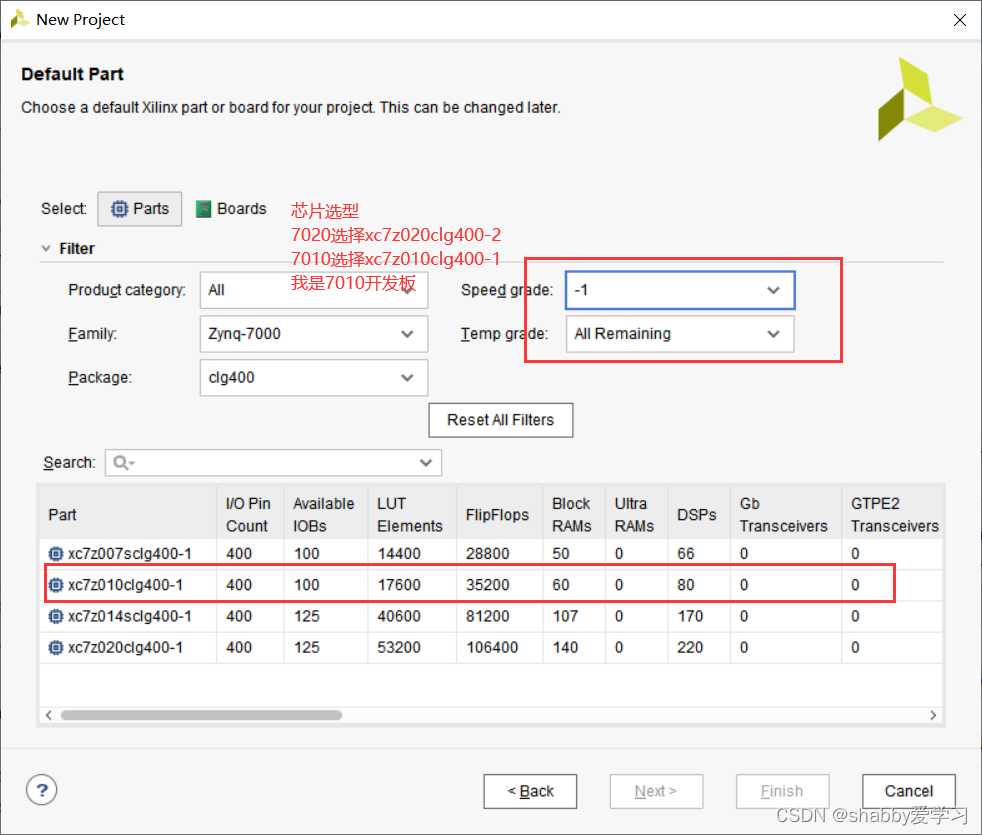

- 芯片选型

- 空工程报告和界面

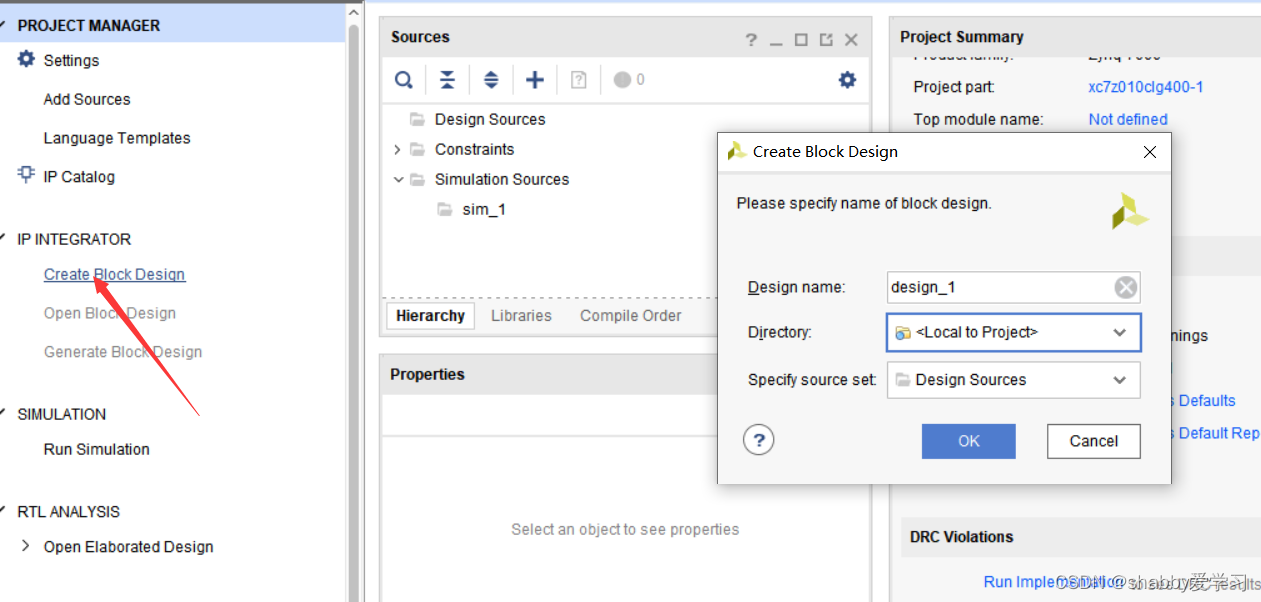

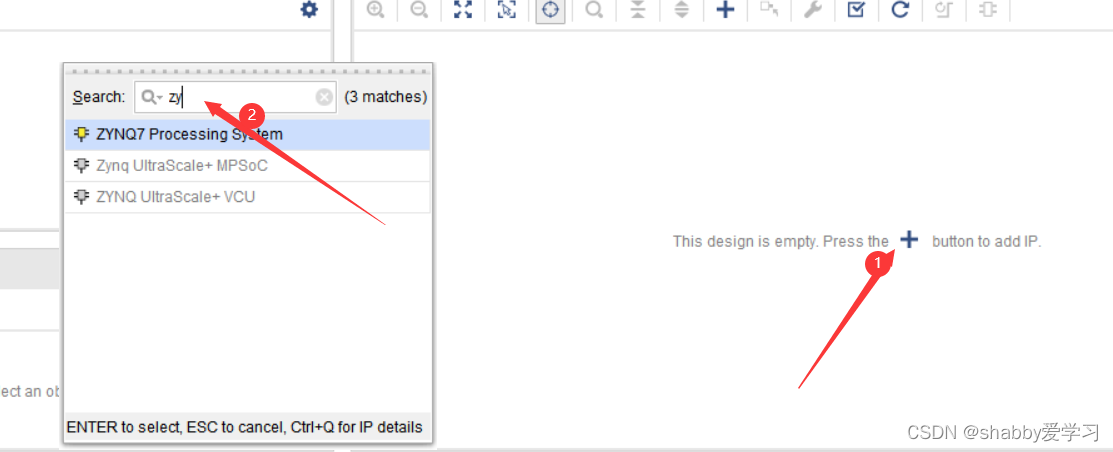

- 比起单纯的fpga开发,需要单独创建一个block designer。这是arm核,调用。为你创建ps部分,

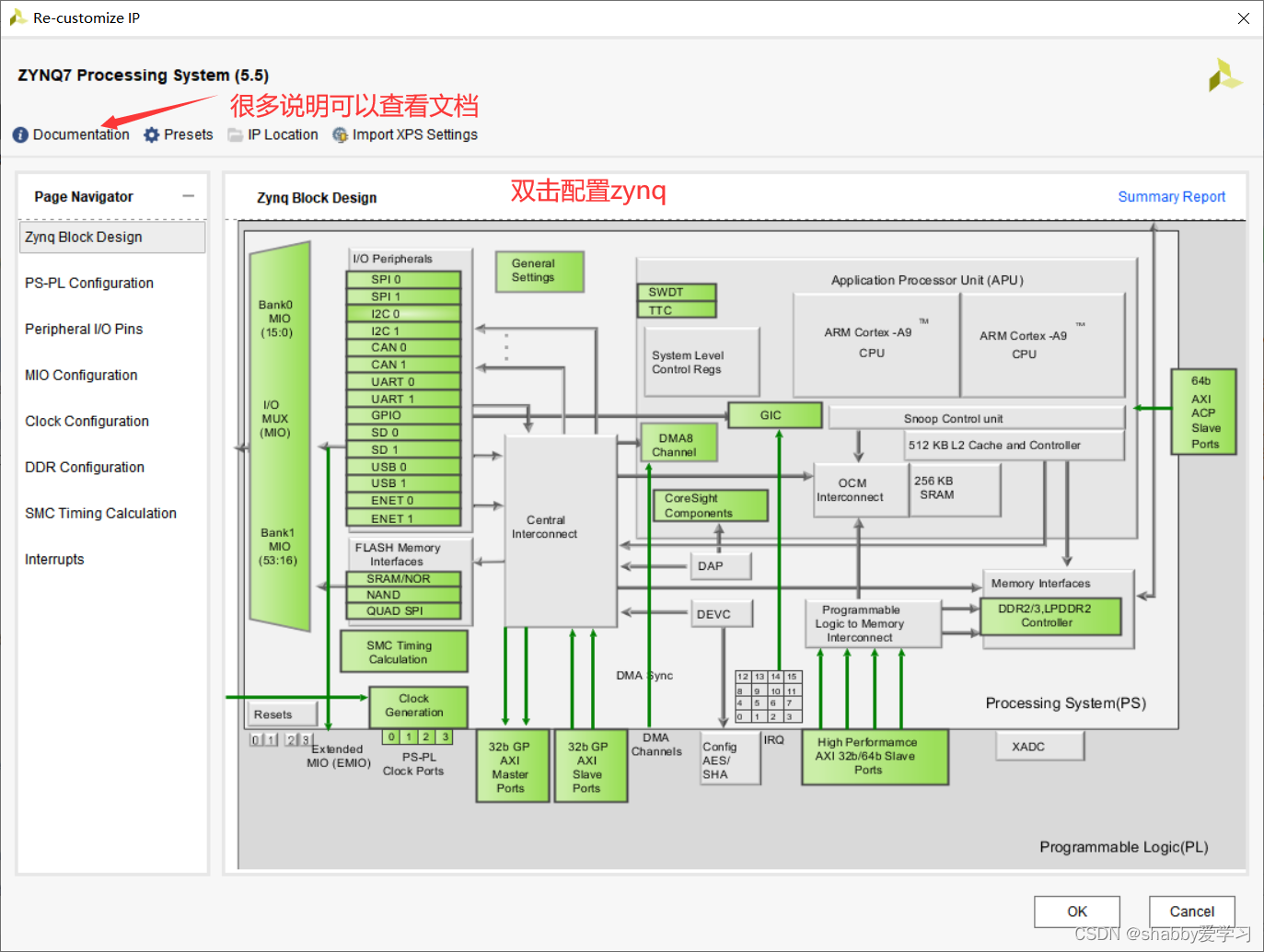

2.ZYNQ配置

- 界面说明 配置ps和pl的参数

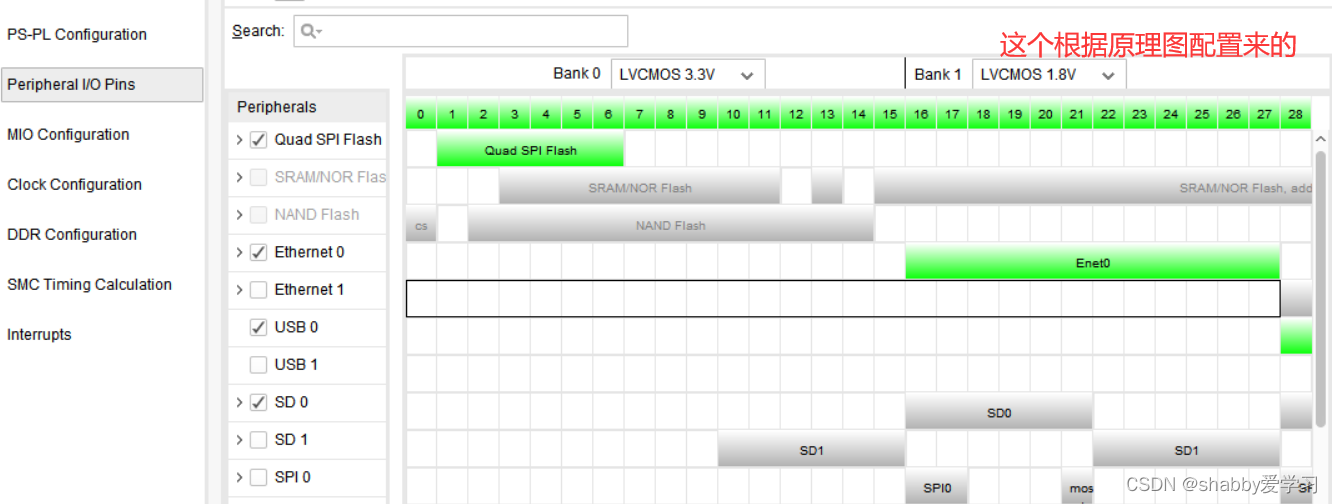

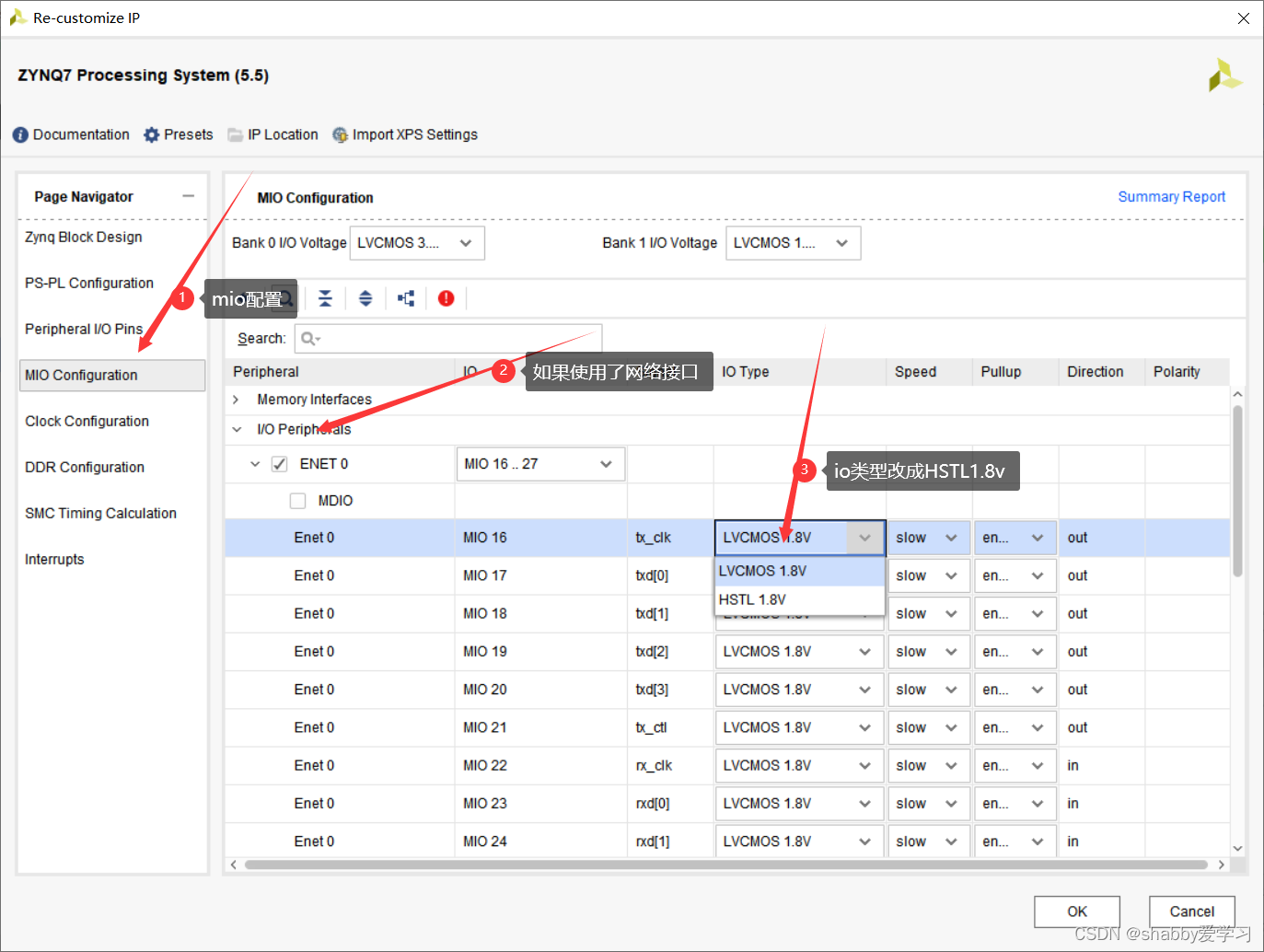

- 总线和外设接口配置

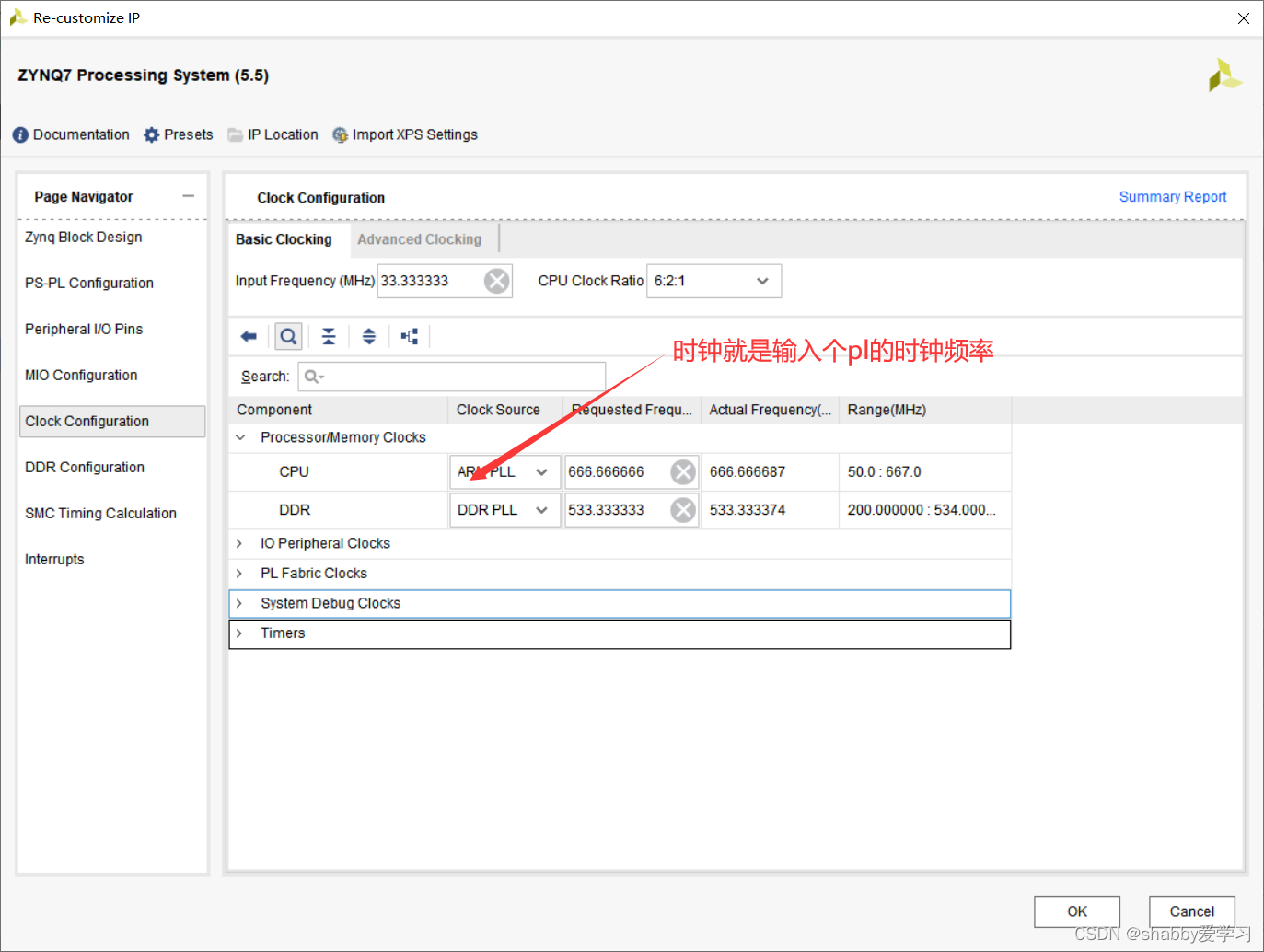

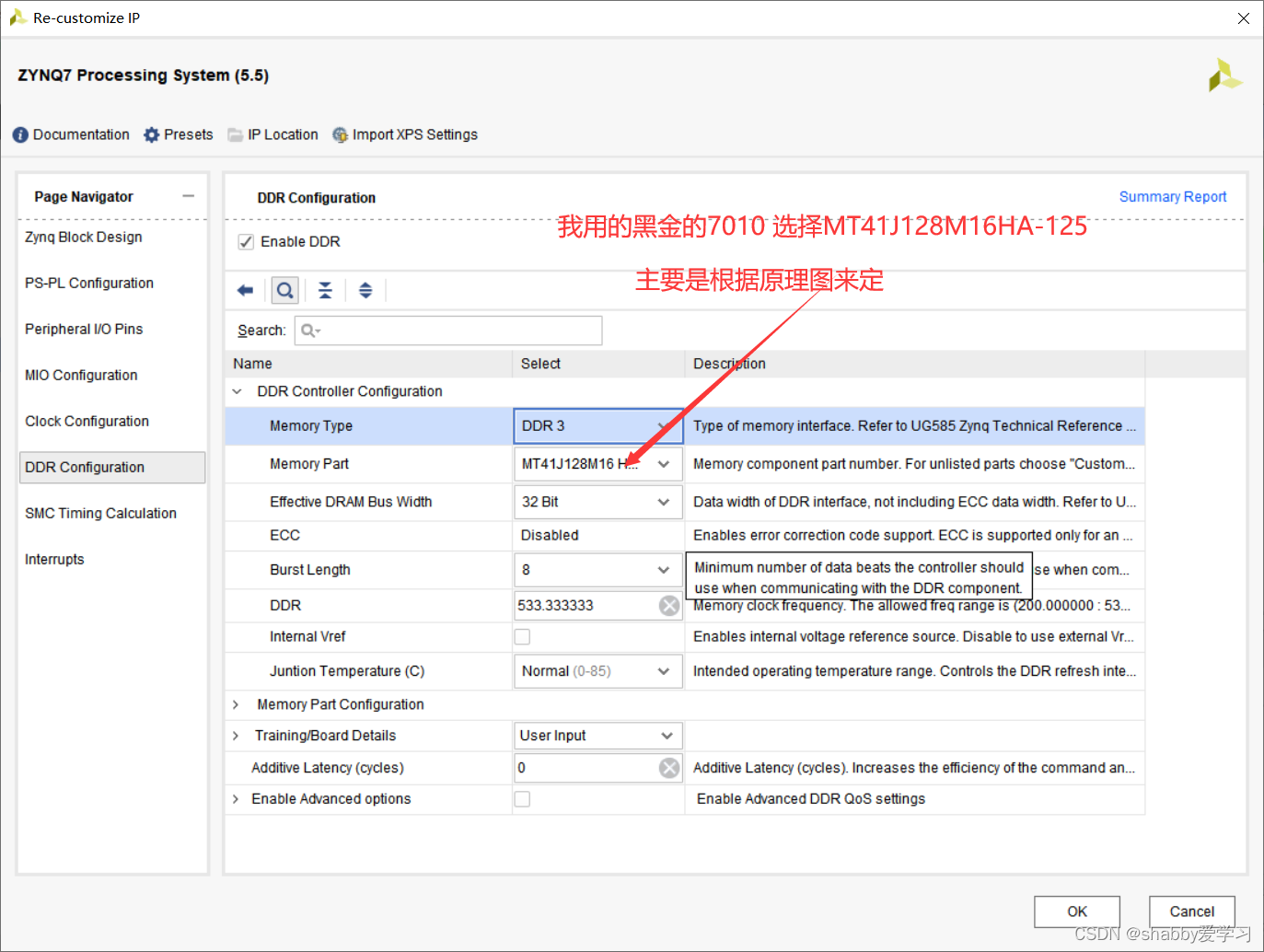

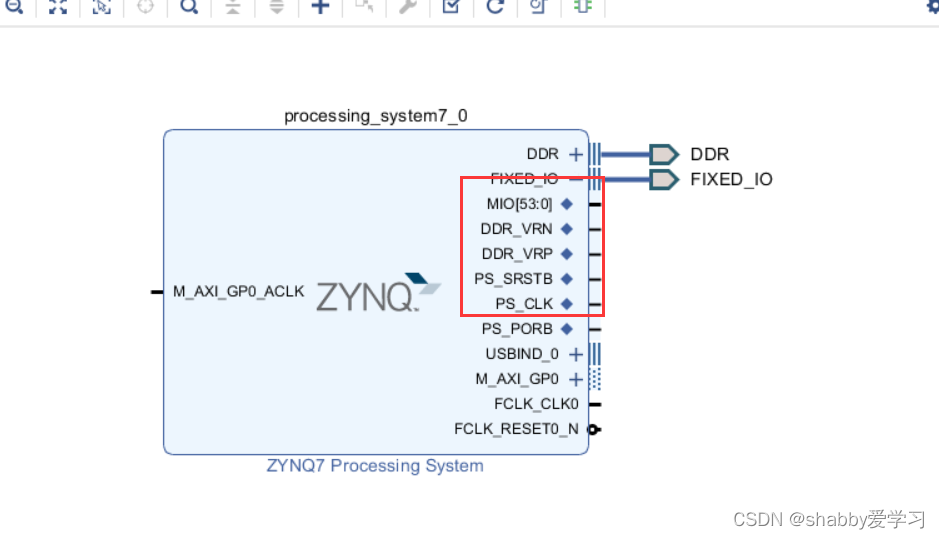

2. ps——clk都是固定的引脚,ps需要时钟驱动,其他都是io口。看原理图 ps_srstb这些引脚都是固定好的,不能外围配置。我们在使用过程中,增加外设就在核中添加,

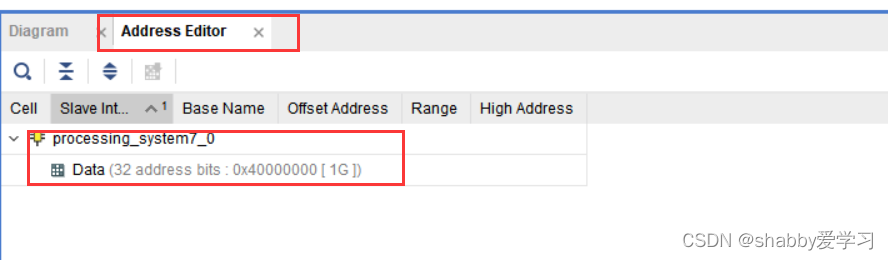

3. 当前没有使用外设,所以没有分配地址。

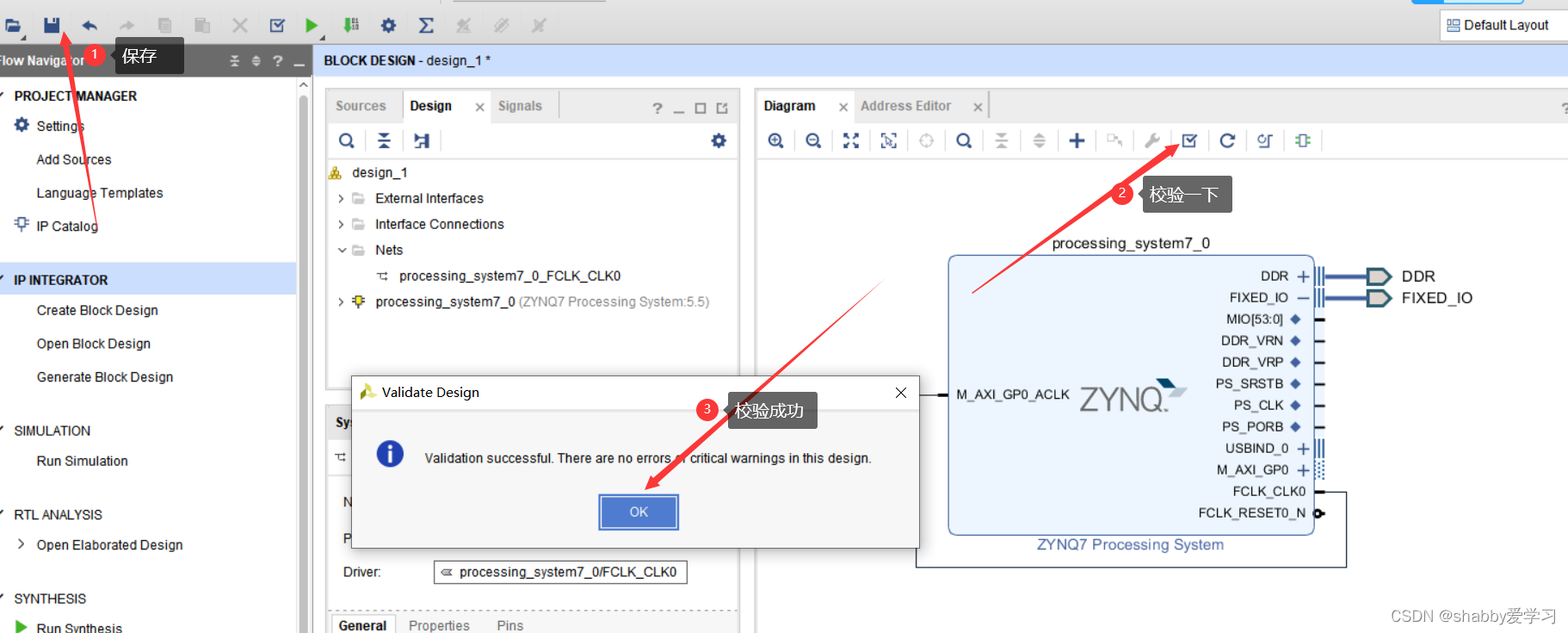

完成原理图设计后,然后再操作。

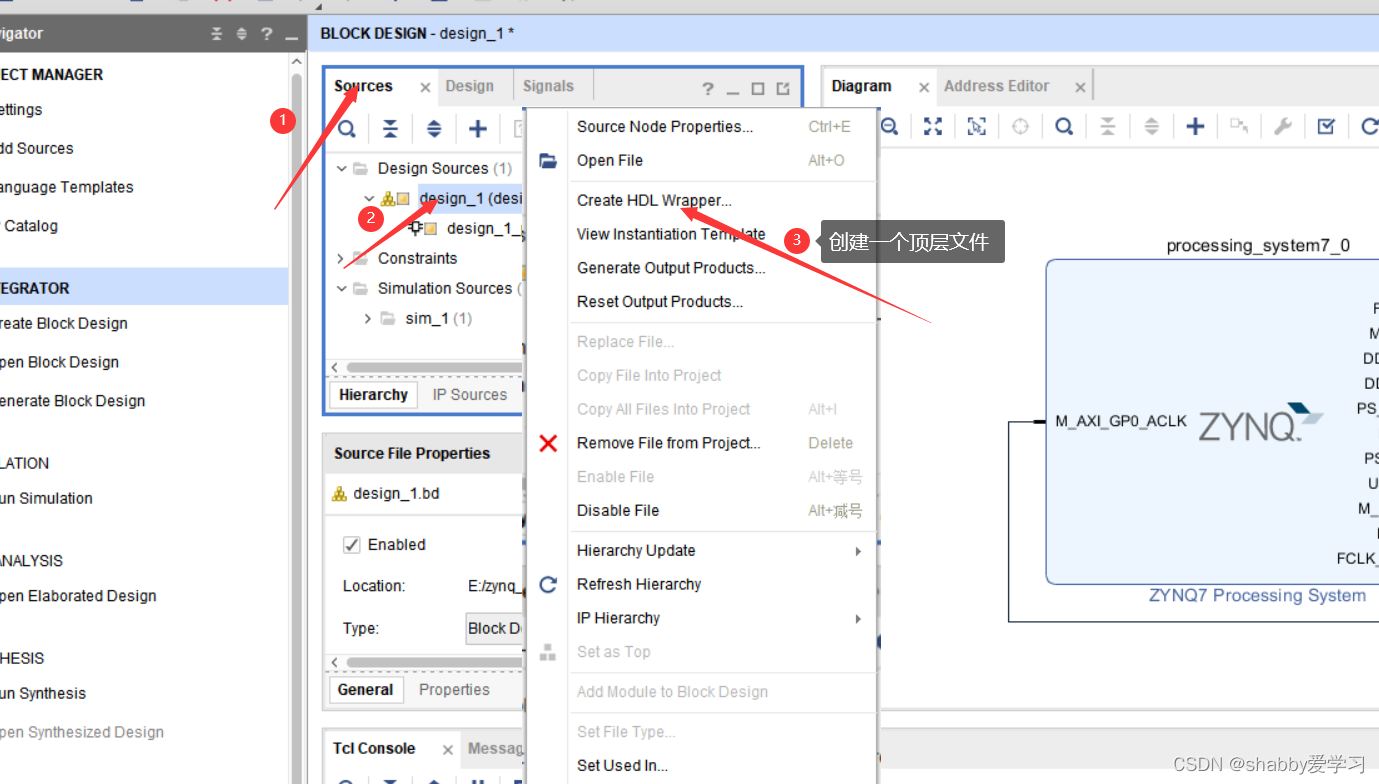

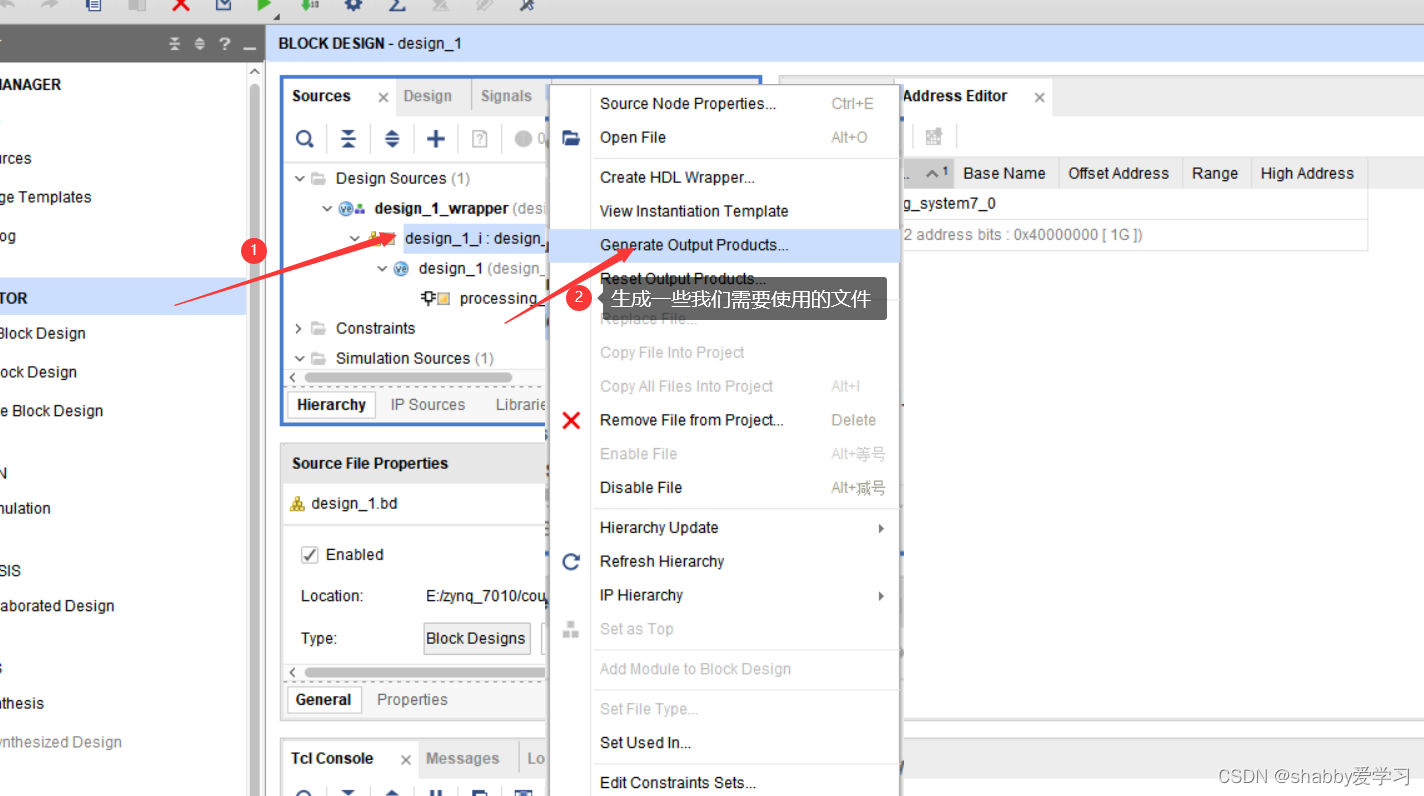

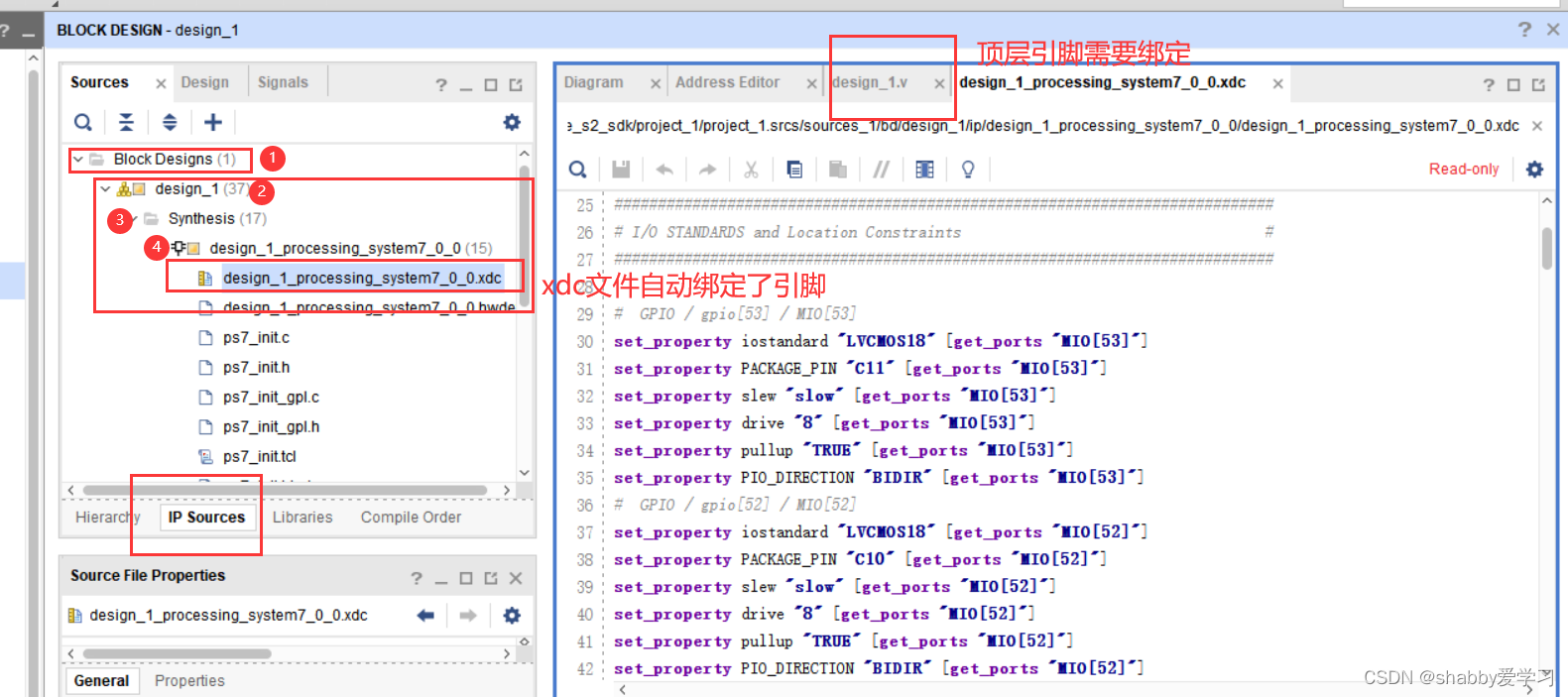

4. 生成顶层后,输出所需要的输出文件。需要花一段时间,完成后会自动更新。ps端全部配置完成后,包括外设,ip调用【可以自定义ip,使用了pl端的逻辑资源】创建

6. 引脚绑定就是在图像化界面配置过程中的位置。

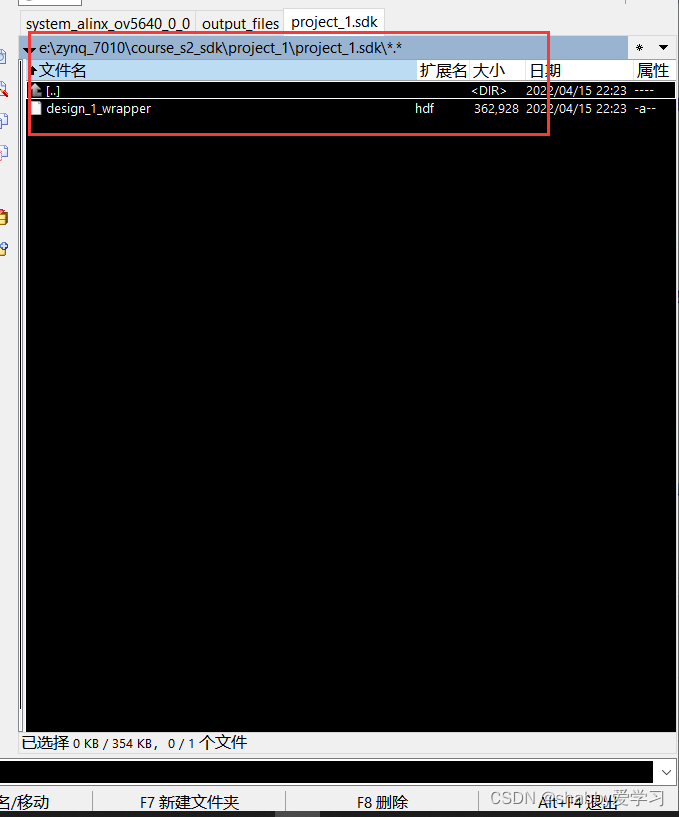

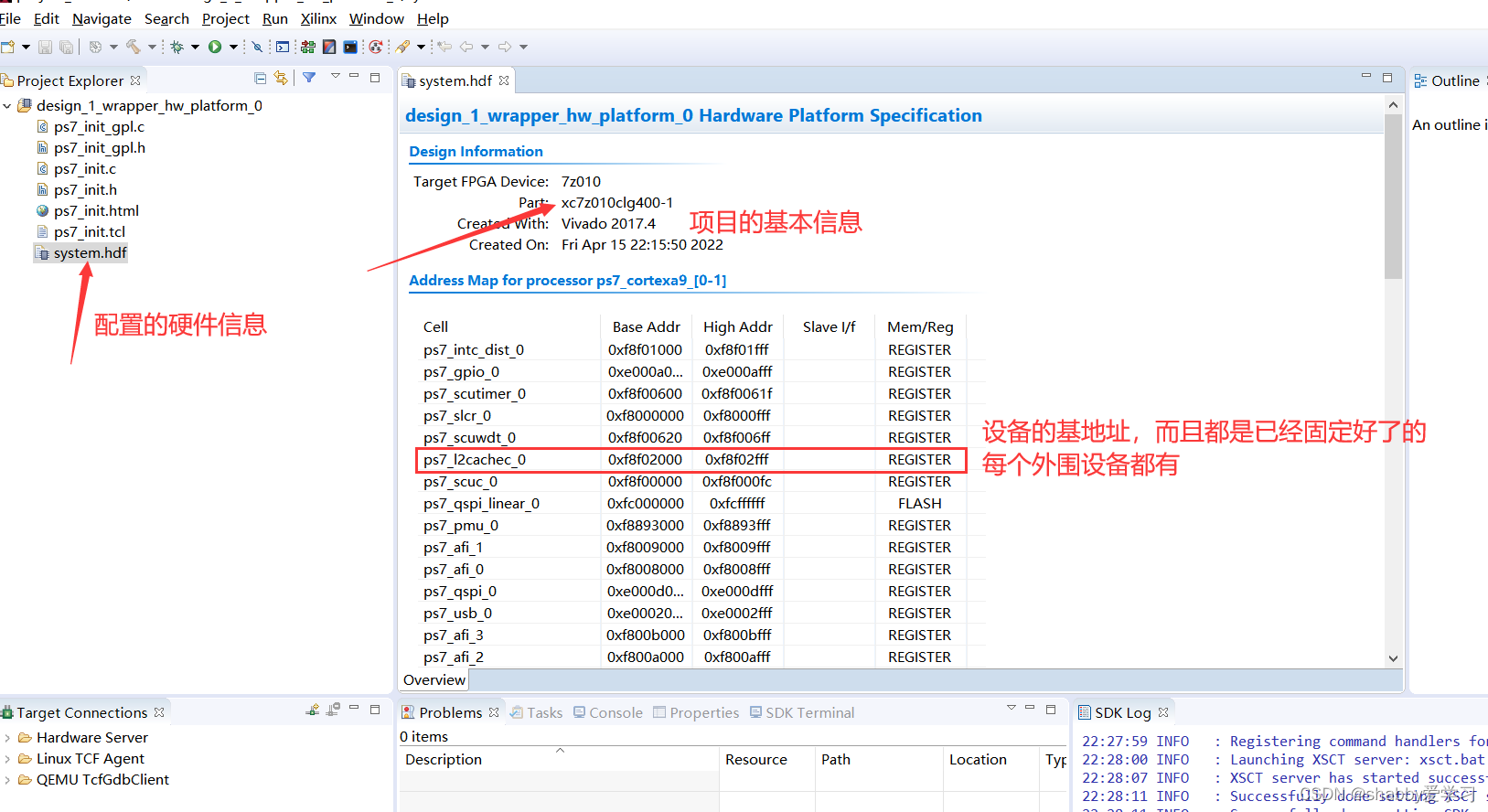

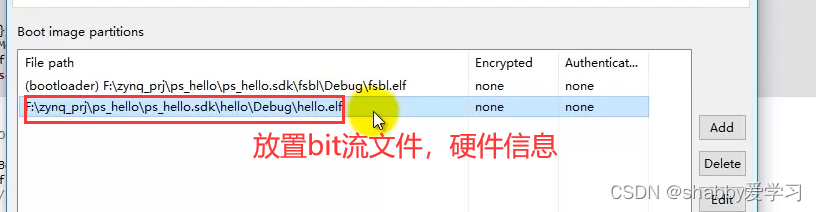

7. 导出配置信息,包括硬件信息,地址,外围设备的地址等,如果有pl逻辑资源就要包含比特流文件。

8. 导出的文件在当前目录下,文件格式.hdf。导出的硬件信息。

3.SDK编译和运行

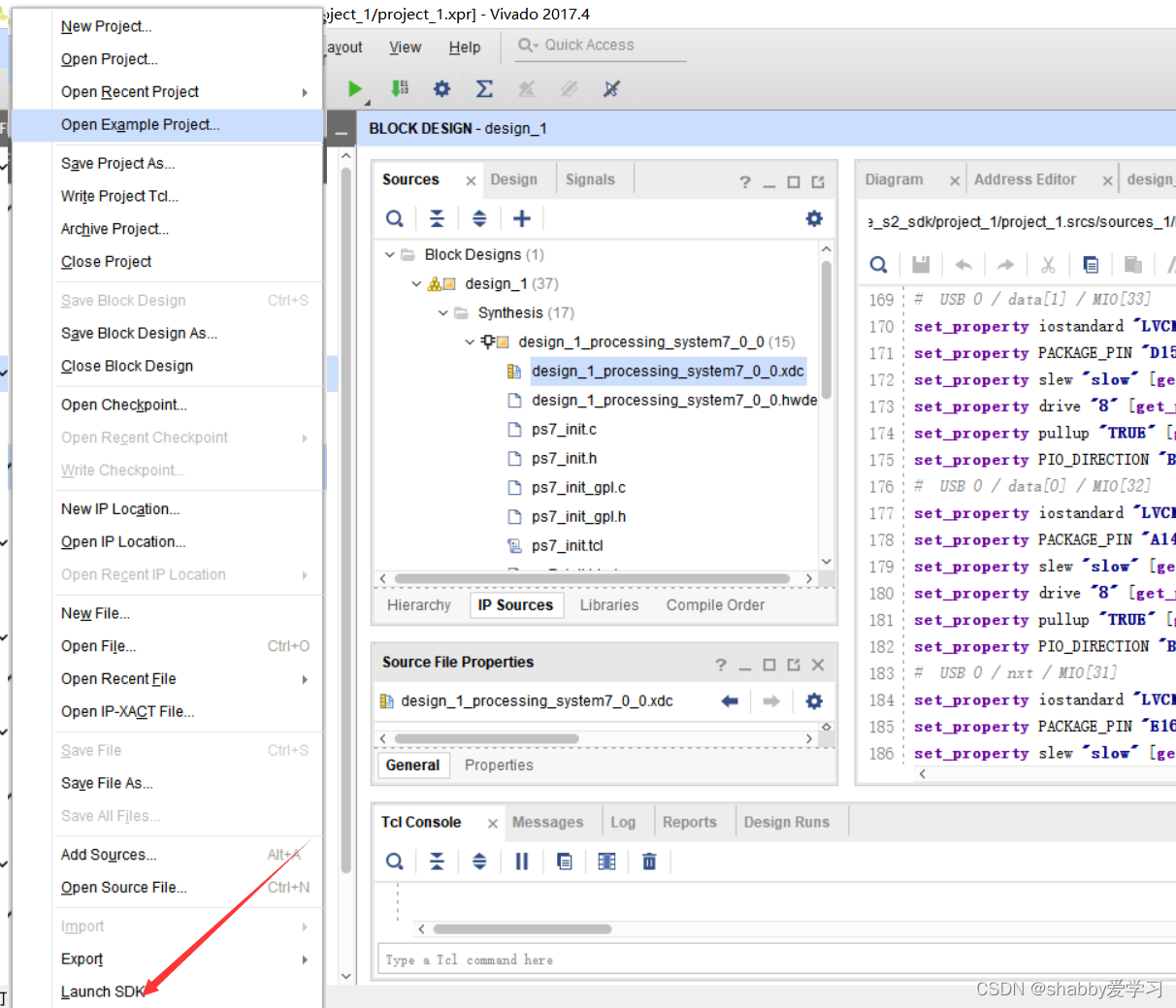

- 打开sdk软件

- 界面介绍

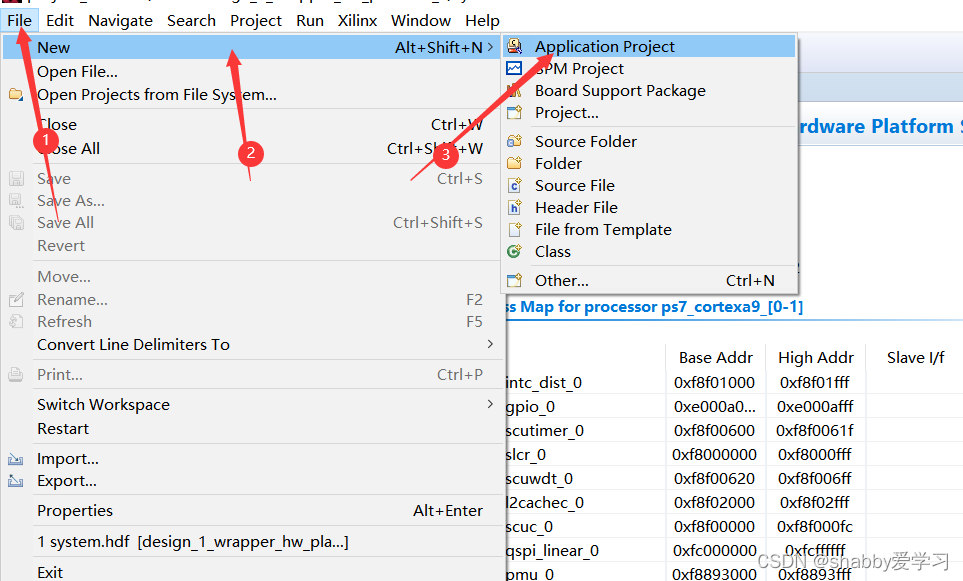

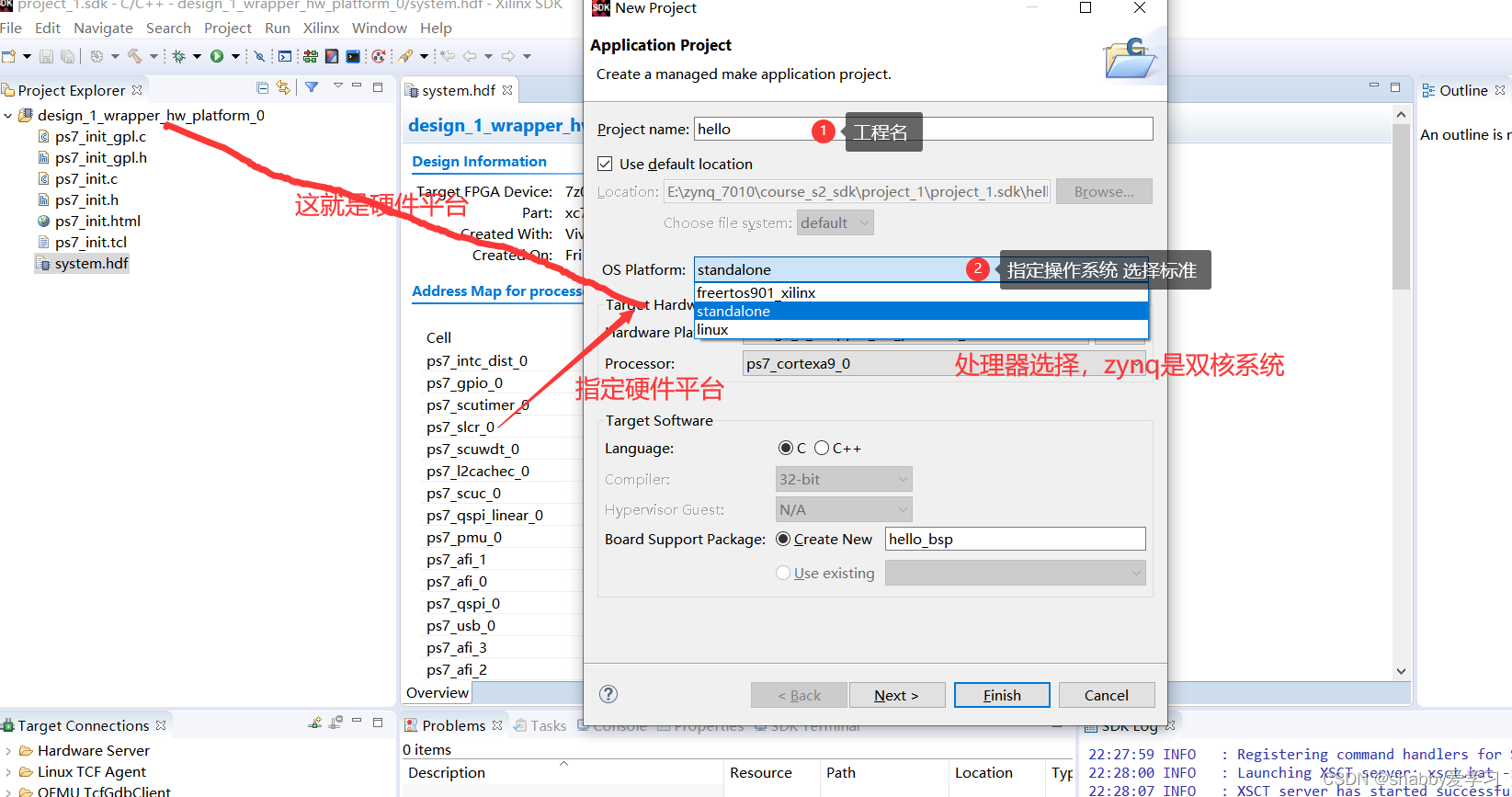

- 新建工程

硬件平台是从vivado中导出来的

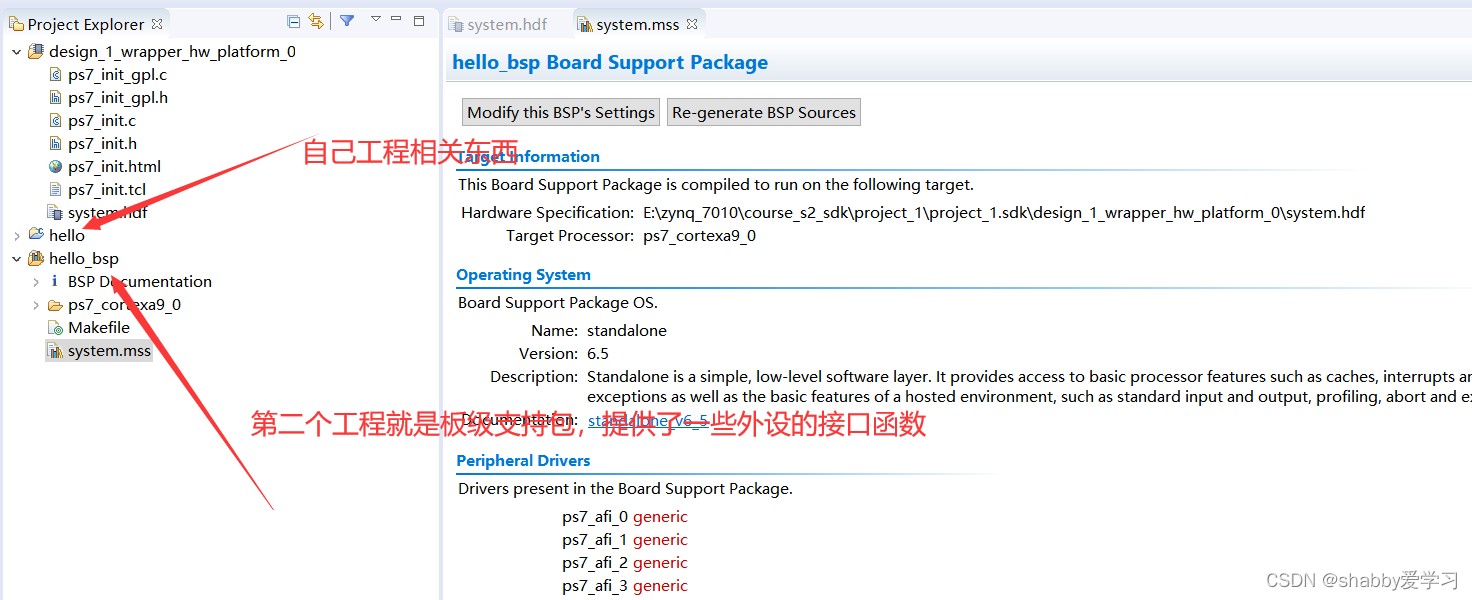

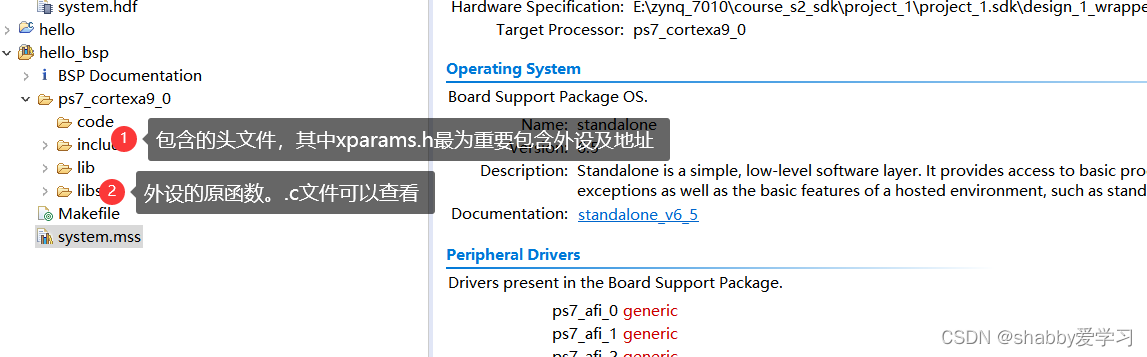

4. 工程二提供了一些头文件和板级支持包,以及外设的接口函数。其中头文件比较重要的是,sparameters.h提供了外设的基地址。

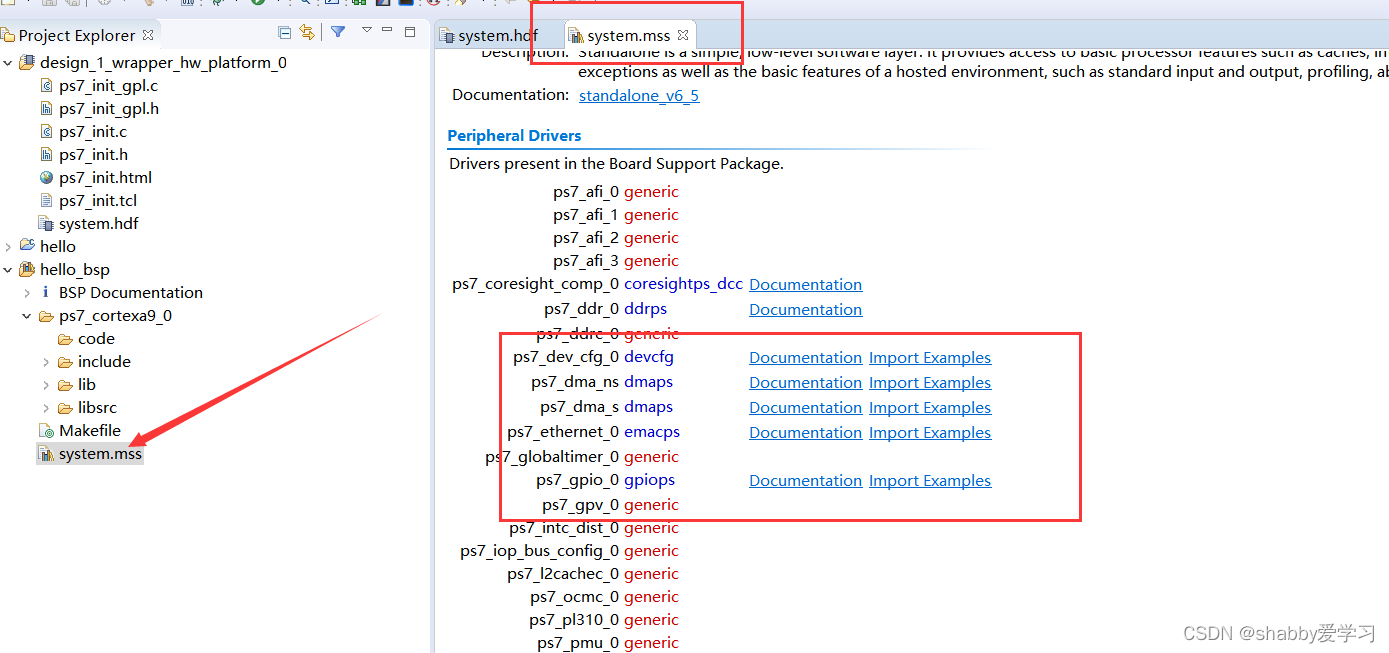

5. 外设的驱动,可供选择。驱动的说明可供查看,接口函数和说明,例子都有。里面也有例子。

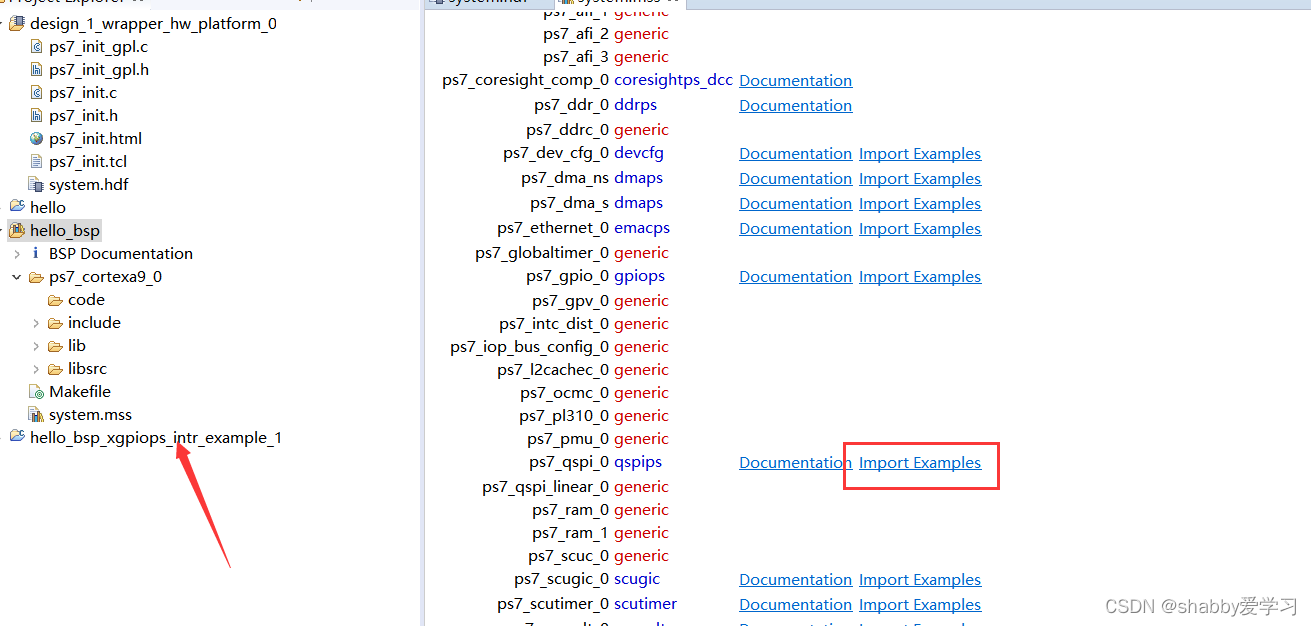

6. 里面有些模块的有些例子可以导入学习。

7. 还有外设选择配置

- 打开sdk软件

4.开发板连接

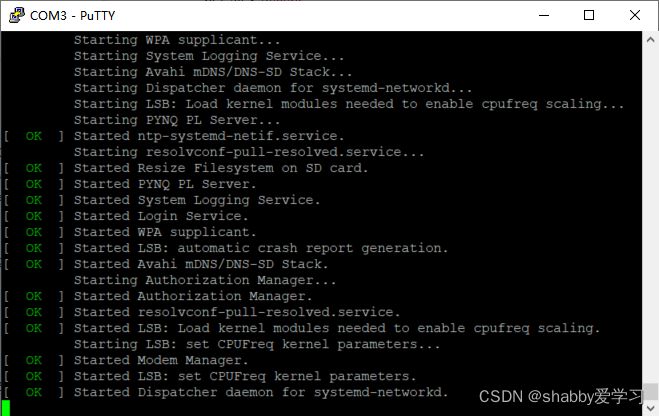

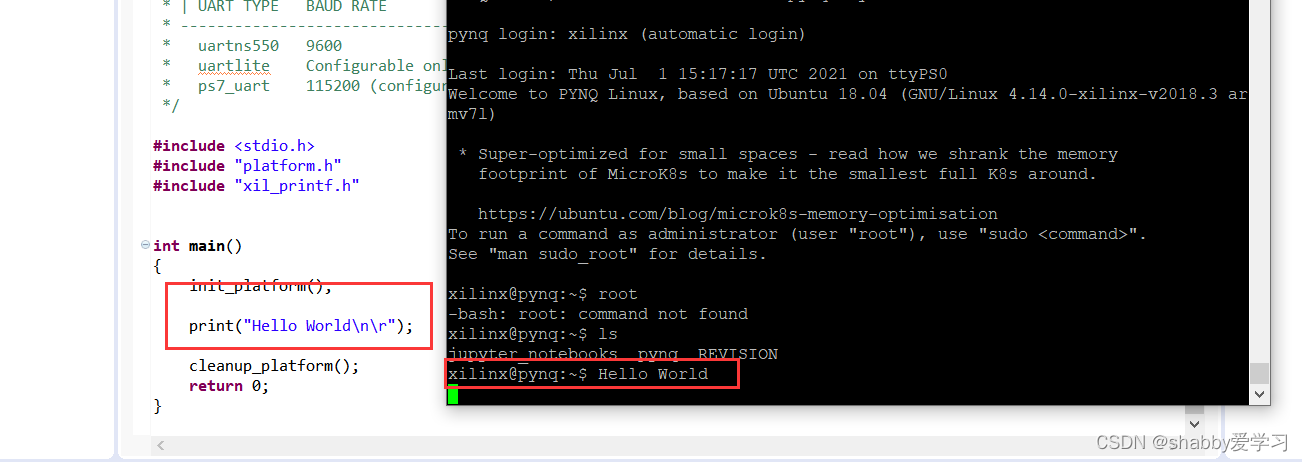

- 串口连接,用putty查看串口号。波特率115200.

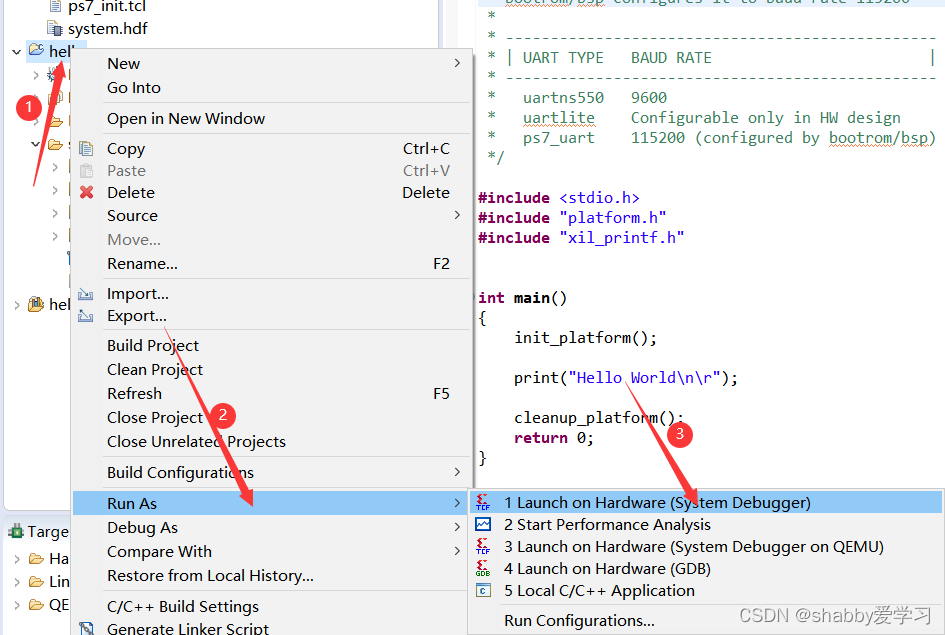

- 下载程序

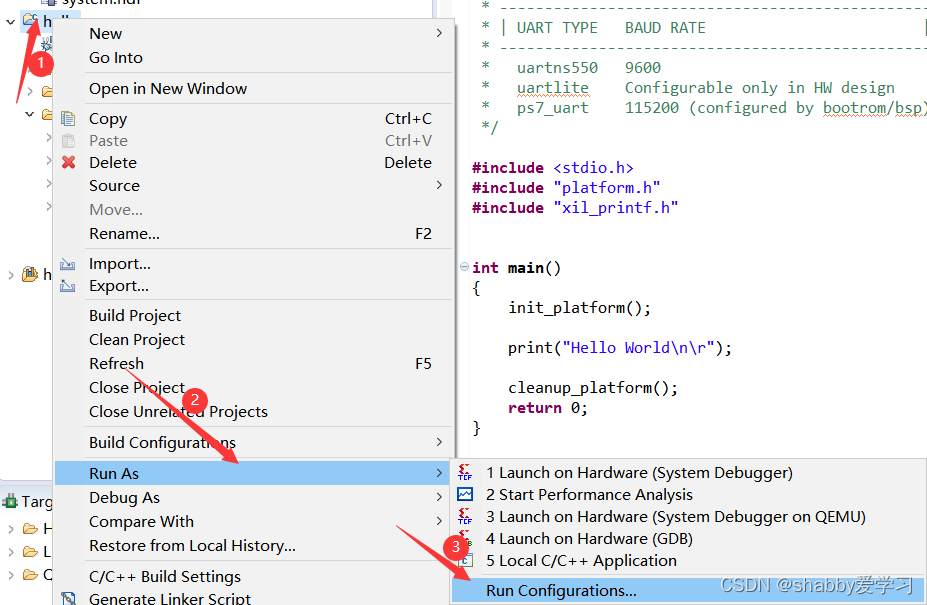

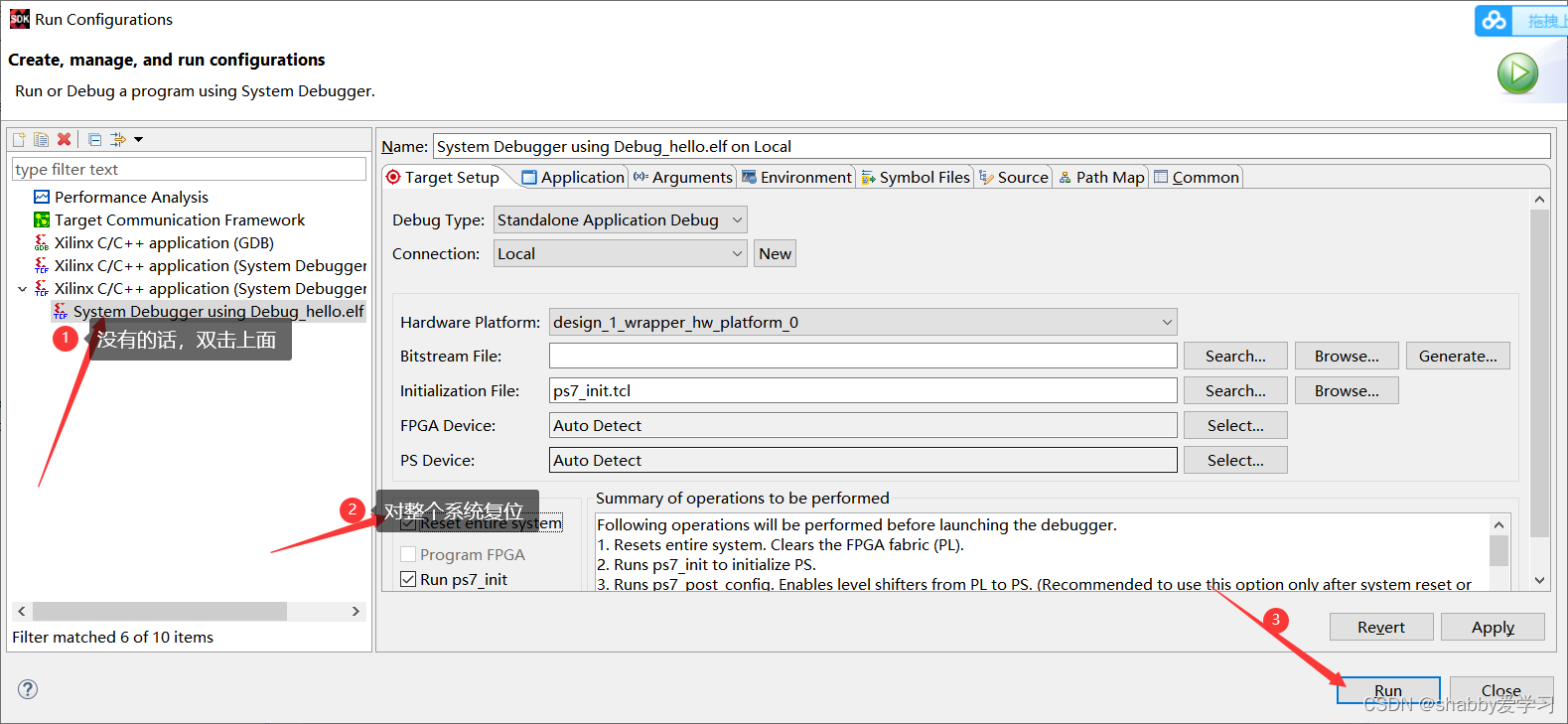

- 如果不行,需要简单配置一下

- 如果没有箭头指向文件,双击箭头上面那个就行。

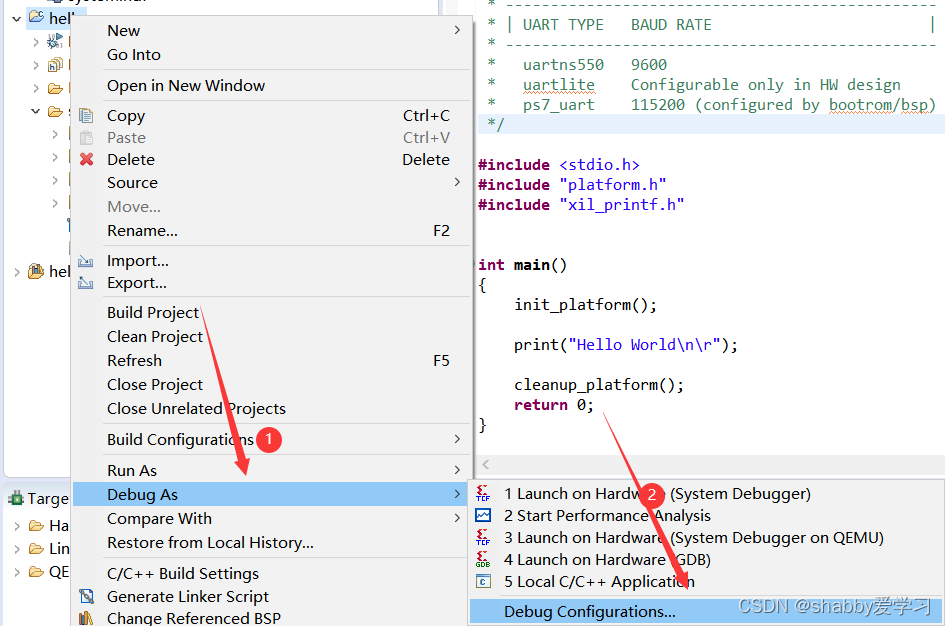

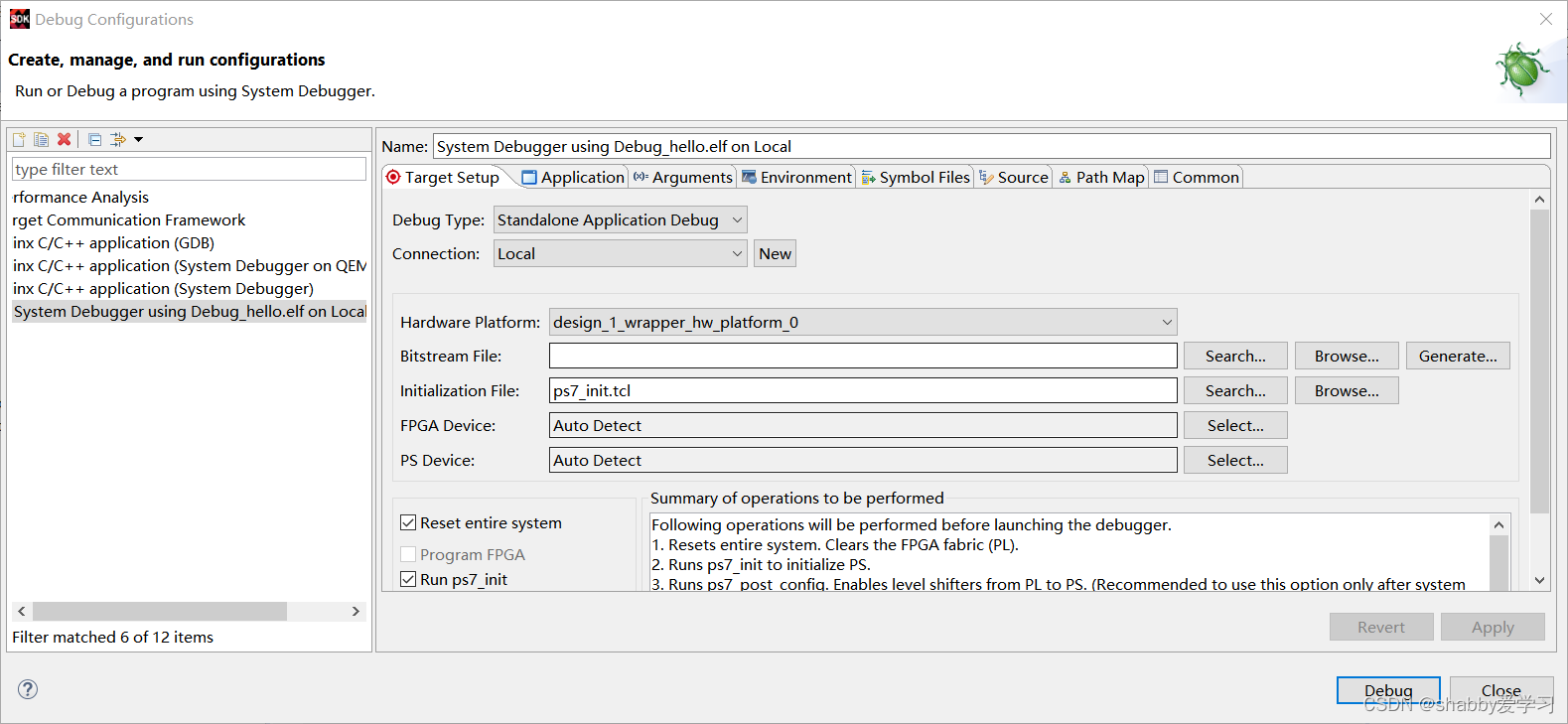

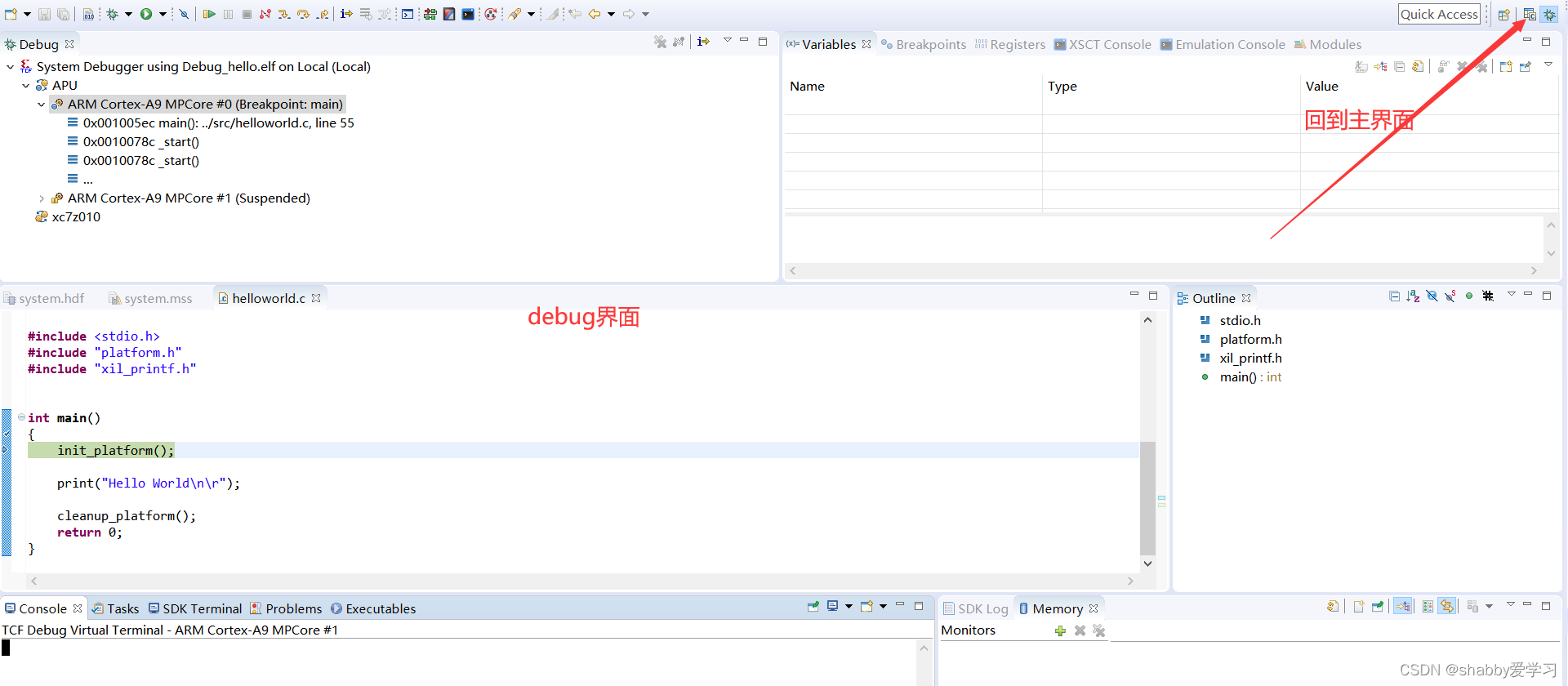

- 进入debug模式

5.程序固化

-

看ug821文档

-

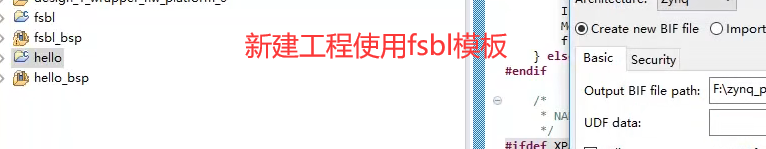

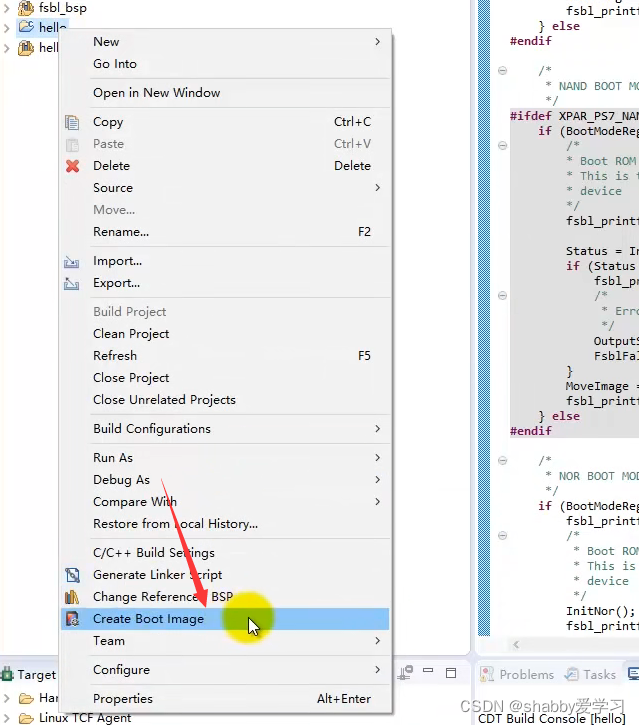

新建工程使用fsbl模板

-

创建文件

-

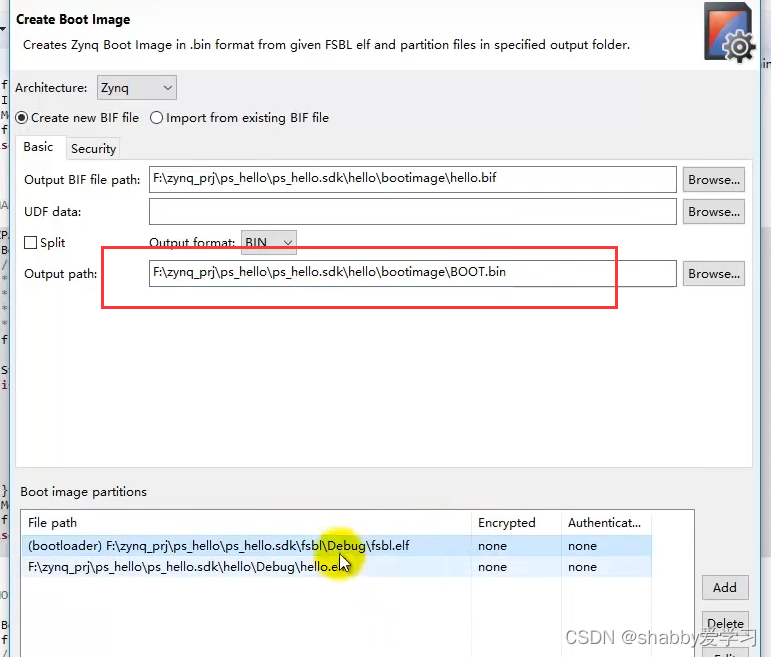

生成固化文件

hello这个过程中没有使用硬件资源

在文件夹下找到boot.bin文件。sd卡启动模式、

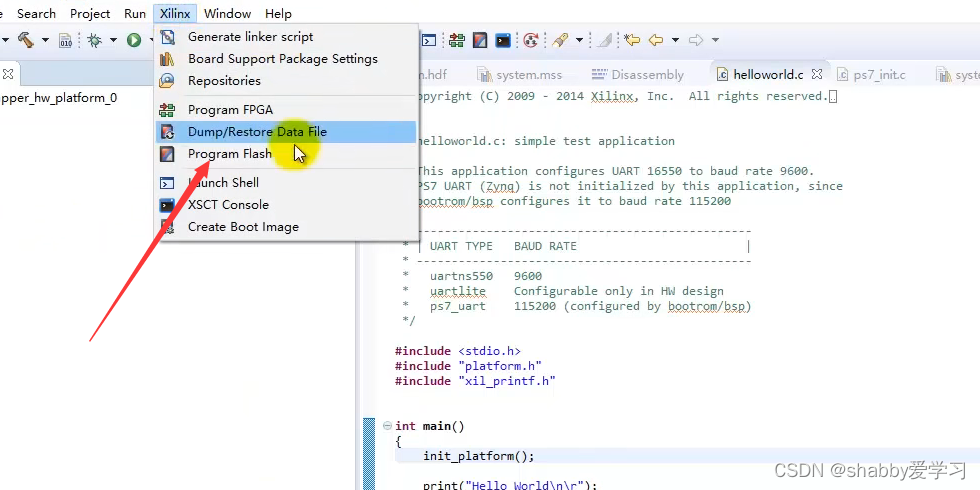

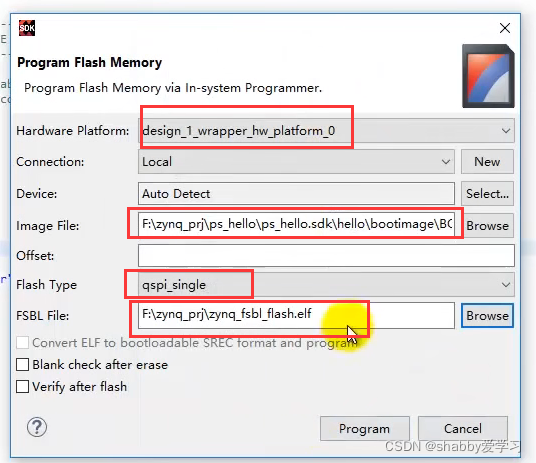

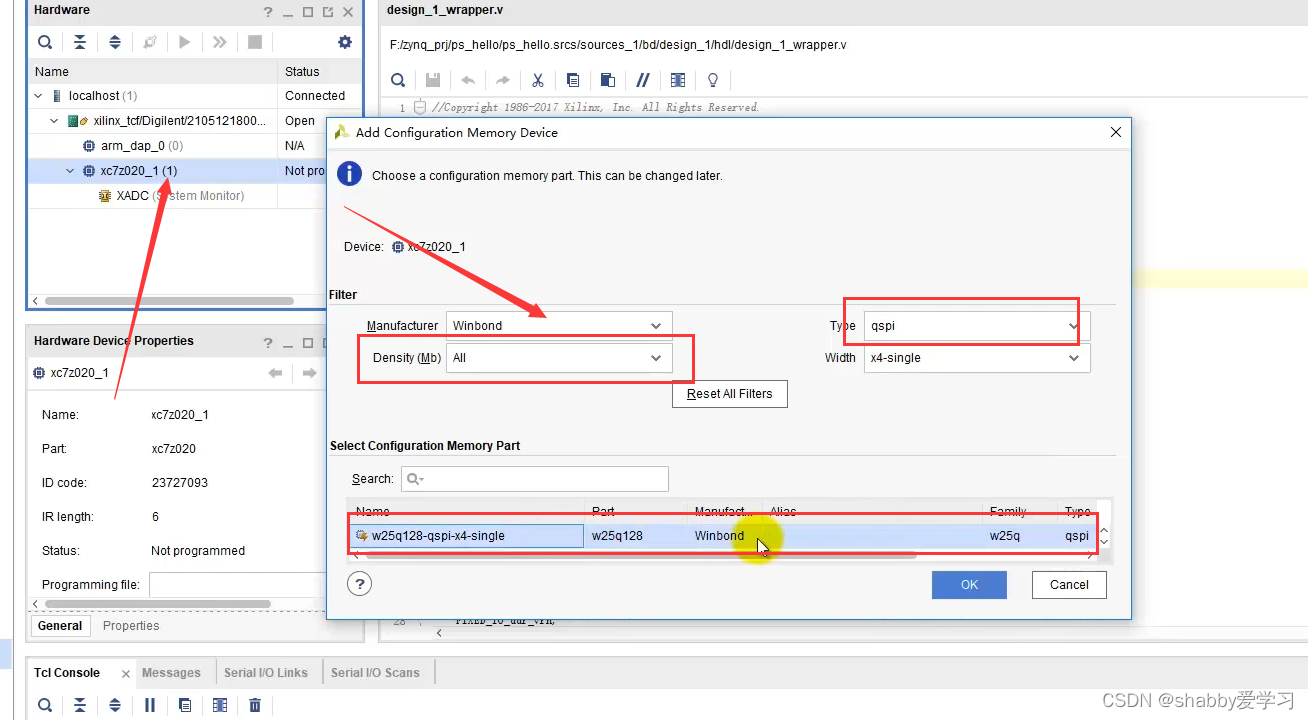

flash启动模式。sd卡模式和qSPI模式可以下载。

在vivado开发界面用qspi下载模式

里面有一个默认的elf文件找到地址即可。这是软件的bug

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)