TMS320F280049学习笔记5_Analog-to-Digital Converter (ADC)

翻译了280049参考手册ADC模块的常用内容。

目录

13.1简介

ADC模块是一个12位逐次逼近(SAR)风格的ADC。ADC由一个核心和一个封装器组成。其核心由模拟电路组成,包括通道选择MUX、采样保持(S/H)电路、逐次逼近电路、电压基准电路和其他模拟支持电路。封装器由配置和控制ADC的数字电路组成。这些电路包括可编程转换逻辑、结果寄存器、模拟电路接口、外设总线接口、后处理电路和其他片上模块接口。

每个ADC模块由一个采样保持(s/h)电路组成。ADC模块被设计为在同一芯片上被复制多次,允许同时采样或多个独立操作ADC。ADC包装器是基于转换开始(SOC)的(见章节13.3)。

13.1.1特性

每个ADC都有以下特性:

- 12位分辨率

- 由VREFHI和VREFLO引脚设置的比率外部参考

- 可选择内部参考2.5V或3.3V

- 单端信号转换

- 多达16路多路输入复用

- 16个可配置的SOC

- 16个单独寻址的结果寄存器

- 多个触发源

- —S/W—软件立即启动

- —所有ePWMs—ADCSOC A或B

- —GPIO XINT2

- —CPU定时器0/1/2

- —ADCINT1/2

- 四个灵活的PIE中断

- 可配置的中断放置

- 突发模态

- 四个后处理块,每个都有:

- —饱和偏置校准

- —设定点计算错误

- —高、低和过零比较,具有中断和ePWM跳闸能力

- —触发-采样延迟捕获

13.1.2ADC框图

13.2ADC可配置性

一些ADC配置由SOC单独控制,而另一些则由每个ADC模块全局控制。表13-1总结了基本的ADC选项和它们的可配置级别。后面的章节将讨论这些配置。

13.2.1时钟配置

基本ADC时钟由系统时钟(SYSCLK)直接提供。这个时钟用来生成ADC采样窗口。寄存器ADCCTL2有一个确定ADCCLK的PRESCALE字段。ADCCLK用于给ADC提供时钟。

**内核大约需要10.5个ADCCLK周期来将一个电压转换成一个转换结果。**用户有必要确定所需的采样窗口持续时间,见章节13.13.2。

13.2.2分辨率

ADC的分辨率决定了模拟范围量化为数字值的精细程度。这个ADC支持12位的分辨率。

13.2.3电压参考

13.2.3.1外部参考模式

每个ADC都有一个VREFHI输入和一个VREFLO输入。在外部参考模式下,这些引脚被用作比率参考,以确定ADC转换输入范围。

有关如何提供参考电压的信息,请参见13.13.6节。

注意:

- 在没有外部VREFLO信号的设备上,VREFLO内部默认连接到设备模拟地VSSA

- 请参阅您的设备特定的数据表,以确定VREFHI和VREFLO的允许电压范围

- 外部参考模式需要VREFHI引脚上的外部电容。有关所需的特定值,请参阅您的设备特定数据表

280049CLanch的板子VREFHI和VREFLO原理图如下:

13.2.3.2内部参考模式

在内部参考模式下,设备驱动VREFHI引脚输出电压。VREFHI和VREFLO引脚然后设置ADC转换范围。

内部参考电压可配置为2.5V或1.65V。当选择1.65V的内部参考电压时,有效ADC转换输入范围为VREFLO到3.3V。

13.2.3.3联合参考

某些封装上,多个ADC的电压基准引脚可以组合使用。在这种情况下,当选择外部参考模式和内部参考模式,以及选择3.3V或2.5V的内部参考电压范围时,需要将组参考配置相同。

例如,如果ADC B和ADC C参考引脚组合,所需的参考模式为2.5V内部参考模式,则应运行以下参考配置代码:

//ADCB VREFHI and ADCC VREFHI share a pin

//ADCB VREFLO and ADCC VREFLO share a pin

//Both references must be explicitly configured

//Both references must be configured identically

SetVREF(ADC_ADCB, ADC_INTERNAL, ADC_VREF2P5);

SetVREF(ADC_ADCC, ADC_INTERNAL, ADC_VREF2P5);

内部设备硬件将确保多个引用不会在同一引脚上驱动冲突的电压。

因此,参考可以按照任意顺序或任意时间进行配置。

13.2.3.4选择参考模式

电压参考模式应该使用C2000Ware提供的SetVREF或ADC_setVREF功能来配置。使用这些函数中的任何一个都可以确保正确的调整被加载到ADC调整寄存器中。该函数必须在设备复位后至少调用一次。不要直接写入ANAREFCTL寄存器来配置电压参考模式。

13.2.4信号模式

ADC支持单端信令。

在单端模式下,参考VREFLO通过单引脚(ADCINx)对变换器的输入电压进行采样。

13.2.5期望转换结果

基于给定的模拟输入电压,理想的期望数字转换如表13-2所示。超出范围的数值被截断。

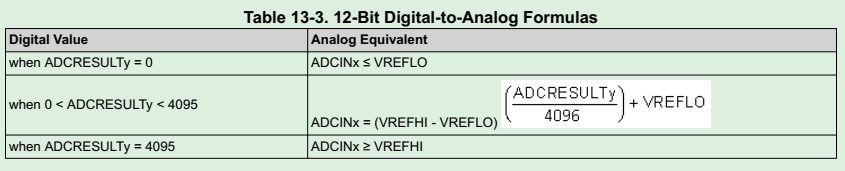

13.2.6转换结果解释

根据给定的ADC转换结果,理想的对应模拟量输入如表13-3所示。这对应于可能产生这种转换结果的模拟电压的可能范围。

13.3SOC工作原理

ADC触发和转换排序是通过可配置的转换起始(SOC)来完成的。每个SOC是一个配置集,定义单个通道的单个转换。在该集合中有三种配置:启动转换的触发源、要转换的通道和采集(样本)窗口持续时间。在接收到为SOC配置的触发器时,封装器将确保指定的通道 使用指定的采样窗口持续时间。

多个SOC可以根据需要配置为相同的触发器、通道和/或采样窗口。

将多个SOC配置为使用同一个触发器将允许触发器生成一系列转换。

将多个SOC配置为使用相同的触发器和通道将允许进行过采样。

13.3.1 SOC配置

每个SOC都有自己的配置寄存器ADCSOCxCTL。在这个寄存器中,SOCx可以配置为触发源、转换通道和采样窗口持续时间。

13.3.2 触发操作

每个SOC可以配置为在多个输入触发器中的一个上启动。SOCx的主要触发器选择在ADCSOCxCTL。TRIGSEL寄存器,可以选择:

- Disabled (software only)

- CPU Timers 0/1/2

- GPIO: Input X-Bar INPUT5

- ADCSOCA or ADCSOCB from each ePWM module

此外,每个SOC也可以在设置ADCINT1或ADCINT2标志时触发。这是通过配置ADCINTSOCSEL1寄存器(用于SOC0到SOC7)或ADCINTSOCSEL2寄存器(用于SOC8到SOC15)。这对于创建持续的转换非常有用。

13.3.3 ADC采集(采样和保持)窗口

外部信号源在快速有效地驱动模拟信号的能力方面各不相同。为了达到额定分辨率,信号源需要将ADC核心中的采样电容充电到信号电压0.5 lsb以内。**采样窗口是采样电容被允许充电的时间量,**并由ADCSOCxCTL.ACQPS寄存器为SOCx进行配置。

ACQPS是一个9位寄存器,可以设置为0到511之间的值,所以采集窗口持续时间为:

Acquisition window = (ACQPS + 1)∙(System Clock (SYSCLK) cycle time)

- 采样窗口持续时间基于系统时钟(SYSCLK),而不是ADC时钟(ADCCLK)。

- 选定的采样窗口持续时间必须至少与一个ADCCLK周期一样长。

- 数据表将指定最小采集窗口持续时间(以纳秒为单位)。用户负责选择符合这一要求的获取窗口持续时间。

13.3.4 ADC输入模型

对于单端操作,ADC输入特性值在单端输入模型中(见图

13-3)可以在设备特定的数据表中找到。

这些输入模型应与实际信号源阻抗一起使用,以确定采集窗口的持续时间。更多信息请参见13.13.2节。

13.3.5通道选择

每个SOC可以被配置为转换任何ADC通道。通过ADCSOCxCTL。CHSEL寄存器为SOCx选择此行为

表13-4总结了这一点。

13.4SOC配置举例

13.4.1 ePWM触发器单次转换

要将ADCA配置为在ePWM计时器达到其周期匹配时在通道ADCIN1上执行单个转换,需要做一些事情。首先,必须配置ePWM3来生成一个SOCA或SOCB信号(在这条语句中,SOC指的是ePWM模块中的一个信号)。请参阅增强型脉宽调制器模块(ePWM)章节介绍如何做到这一点。假设选择了SOCB。

SOC5是任意选择的。这16个SOC都可以使用。

假设在SYSCLK频率为100 MHz的情况下需要100 ns的采样窗口,那么采集窗口持续时间应为100 ns/10 ns = 10个周期。因此,ACQPS字段应该设置为10 - 1 = 9。代码如下:

AdcaRegs.ADCSOC5CTL.bit.CHSEL = 1; //SOC5 will convert ADCINA1

AdcaRegs.ADCSOC5CTL.bit.ACQPS = 9; //SOC5 will use sample duration of 10 SYSCLK cycles

AdcaRegs.ADCSOC5CTL.bit.TRIGSEL = 10; //SOC5 will begin conversion on ePWM3 SOCB

按照配置,当ePWM3匹配其周期并产生SOCB信号时,如果ADC空闲,ADC将立即开始采样通道ADCINA1 (SOC5)。如果ADC忙,ADCINA1将在SOC5获得优先级(见章节13.5)时开始采样。ADC控制逻辑将以指定的100 ns的采样窗宽对ADCINA1进行采样。采样完成后,ADC立即开始将采样电压转换为数字值。当ADC转换完成后,结果将可在ADCRESULT5寄存器中得到。(具体样本见章节13.12)

13.4.2 ePWM触发器的过采样转换

为了将ADC配置为ADCINA1采样4次,我们使用与前面示例相同的配置,但将它们应用到SOC5、SOC6、SOC7和SOC8。

AdcaRegs.ADCSOC5CTL.bit.CHSEL = 1; //SOC5 will convert ADCINA1

AdcaRegs.ADCSOC5CTL.bit.ACQPS = 9; //SOC5 will use sample duration of 10 SYSCLK cycles

AdcaRegs.ADCSOC5CTL.bit.TRIGSEL = 10; //SOC5 will begin conversion on ePWM3 SOCB

AdcaRegs.ADCSOC6CTL.bit.CHSEL = 1; //SOC6 will convert ADCINA1

AdcaRegs.ADCSOC6CTL.bit.ACQPS = 9; //SOC6 will use sample duration of 10 SYSCLK cycles

AdcaRegs.ADCSOC6CTL.bit.TRIGSEL = 10; //SOC6 will begin conversion on ePWM3 SOCB

AdcaRegs.ADCSOC7CTL.bit.CHSEL = 1; //SOC7 will convert ADCINA1

AdcaRegs.ADCSOC7CTL.bit.ACQPS = 9; //SOC7 will use sample duration of 10 SYSCLK cycles

AdcaRegs.ADCSOC7CTL.bit.TRIGSEL = 10; //SOC7 will begin conversion on ePWM3 SOCB

AdcaRegs.ADCSOC8CTL.bit.CHSEL = 1; //SOC8 will convert ADCINA1

AdcaRegs.ADCSOC8CTL.bit.ACQPS = 9; //SOC8 will use sample duration of 10 SYSCLK cycles

AdcaRegs.ADCSOC8CTL.bit.TRIGSEL = 10; //SOC8 will begin conversion on ePWM3 SOCB

按照配置,当ePWM3匹配其周期并产生SOCB信号时,如果ADC空闲,ADC将立即开始采样通道ADCINA1 (SOC5)。如果ADC繁忙,ADCINA1将在SOC5获得优先级时开始采样(见章节13.5)。一旦SOC5的转换完成,SOC6将开始转换ADCINA1,并且SOC5的结果将被放置在ADCRESULT5寄存器中。这四种转换最终将依次完成,结果分别为对应SOC5、SOC6、SOC7、SOC8的ADCRESULT5、ADCRESULT6、ADCRESULT7、ADCRESULT8

13.4.3 CPU定时器触发器的多次转换

这个例子将展示如何用不同的采集窗要求对多个信号进行采样。CPU1计时器2将用于生成触发器。要了解如何配置CPU定时器,请参阅系统控制和中断章节。

在设计多信号采样方案时,一个很好的第一步是列出信号及其所需的采样窗口。由此计算每个信号所需的SYSCLK周期数,然后进行ACQPS寄存器设置。这如表13-5所示,其中SYCLK假设为100 MHz (10 ns周期时间)。

接下来决定哪个ADC引脚连接到每个信号。这将高度依赖于应用程序板布局。一旦选择了引脚,确定CHSEL的值就很简单了(见表13-6)。

利用信息表格,很容易生成SOC配置:

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 5; //SOC0 will convert ADCINA5

AdcaRegs.ADCSOC0CTL.bit.ACQPS = 23; //SOC0 will use sample duration of 24 SYSCLK cycles

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 3; //SOC0 will begin conversion on CPU1 Timer 2

AdcaRegs.ADCSOC1CTL.bit.CHSEL = 0; //SOC1 will convert ADCINA0

AdcaRegs.ADCSOC1CTL.bit.ACQPS = 88; //SOC1 will use sample duration of 89 SYSCLK cycles

AdcaRegs.ADCSOC1CTL.bit.TRIGSEL = 3; //SOC1 will begin conversion on CPU1 Timer 2

AdcaRegs.ADCSOC2CTL.bit.CHSEL = 3; //SOC2 will convert ADCINA3

AdcaRegs.ADCSOC2CTL.bit.ACQPS = 21; //SOC2 will use sample duration of 22 SYSCLK cycles

AdcaRegs.ADCSOC2CTL.bit.TRIGSEL = 3; //SOC2 will begin conversion on CPU1 Timer 2

AdcaRegs.ADCSOC3CTL.bit.CHSEL = 2; //SOC3 will convert ADCINA2

AdcaRegs.ADCSOC3CTL.bit.ACQPS = 58; //SOC3 will use sample duration of 59 SYSCLK cycles

AdcaRegs.ADCSOC3CTL.bit.TRIGSEL = 3; //SOC3 will begin conversion on CPU1 Timer 2

按照配置,当CPU1 Timer 2生成一个事件时,最终将按此顺序对SOC0、SOC1、SOC2和SOC3进行采样和转换。ACINA5(信号1)的转换结果将在ADCRESULT0中。类似地,ADCINA0(信号2)、ADCINA3(信号3)和ADCINA2(信号4)的结果将在分别为ADCRESULT1、ADCRESULT2、ADCRESULT3。

13.4.4 SOC的软件触发

在任何时候,无论SOC是否配置为接受特定的触发器,软件触发器都可以设置要转换的SOC。这是通过在ADCSOCFRC1寄存器中写入位来实现的。

在不等待CPU1 Timer 2生成触发器的情况下,前面例子中的软件触发可以通过下面的语句来完成:

AdcaRegs.ADCSOCFRC1.all = 0x000F; //set SOC flags for SOC0 to SOC3

13.5ADC转换优先级

当多个SOC标志被同时设置时,两种形式的优先级中的一种决定了它们转换的顺序。默认的优先级方法是轮询。在这个方案中,没有SOC具有比其他SOC更高的固有优先级。优先级由RRPOINTER(轮询指针)决定。反映在ADCSOCPRIORITYCTL寄存器中的RRPOINTER指向最后转换的SOC。优先级最高的SOC被分配给下一个大于RRPOINTER值的值,在SOC15之后绕回SOC0。在重置时,该值为16,因为0表示已经发生了转换。当RRPOINTER = 16时,SOC0优先级最高。当ADCCTL1复位时,RRPOINTER被设备复位。RESET位被设置,或当

写入SOCPRICTL寄存器。

循环优先级方法的示例如图13-4所示。

ADCSOCPRIORITYCTL寄存器中的SOCPRIORITY字段可以用来为所有的SOC分配高优先级。当配置为高优先级时,SOC将在当前转换完成后中断轮询,并在下一次转换时插入自己。转换完成后,轮询轮将在中断的地方继续运行。如果同时触发两个高优先级SOC,则较低值的SOC优先。

首先将高优先级模式分配给SOC0,然后按数字顺序递增。写入SOCPRIORITY字段的值定义了第一个非高优先级SOC。换句话说,如果把4写成SOCPRIORITY, SOC0、SOC1、SOC2、SOC3被定义为高优先级,其中SOC0优先级最高。

图13-5给出了一个使用高优先级SOC的例子。

13.6Burst模式

13.7EOC和中断操作

每个SOC都有一个相应的转换结束(EOC)信号。这个EOC信号可以用来触发ADC中断。**ADC可以配置为在采样窗口的末端或在电压转换的末端产生EOC脉冲。**这是使用ADCCTL1寄存器中的位INTPULSEPOS配置的。

请参阅13.12节了解准确的EOC脉冲位置。

每个ADC模块有4个可配置ADC中断。这些中断可以由16个EOC信号中的任何一个触发。可以直接读取每个ADCINT的标志位,以确定相关的SOC是否完成,或者可以将中断传递给PIE。

13.7.1 基于ADC-EOC中断的多速率控制器高级触发技术

在本节中,c28335_pmsmfoc_adcinterrupt 模型用于使用配置为 c28335_pmsmfoc 的模型块来调用控制器模型。 在 Controller_And_Peripherals 子系统中,ePWM1 模块配置为触发 ADC 转换,以便在 PWM 边沿转换期间不会发生采样(从而最大限度地减少采样信号上的噪声)。 使用 ADC 转换结束中断来调度控制器。 这在 ADC 转换和 PWM 占空比的新值之间提供了最短且最具确定性的延迟。

默认情况下,TI F28335 等处理器的模型集将使用硬件定时器来调度模型中存在的所有同步速率。 如果我们保留此默认行为,控制器算法将不会与 ADC 同步,这可能会在控制器算法和 ADC 转换之间引入延迟或漂移。

在 c28335_pmsmfoc_adcinterrupt 模型配置参数中,在硬件实现 > 调度程序选项下,选择 ADCINT1 作为调度程序中断源。 此选项用来自 ADC 模块 1 (ADCINT1) 的 ADC 中断替换设置为 CPU 定时器 0 中断的默认调度程序中断源。 在 ADC 模块上,为 ADC 模块 1 启用了转换结束中断。由于 ADC 转换是从以 25kHz 运行的 PWM 模块启动的,并且模型的基本速率(基本采样时间)设置为 40us ,可以安全地将调度程序中断源替换为 40us 周期性触发的 ADC 中断。 当使用默认的 CPU 定时器 0 作为调度程序中断源时,该工具将自动设置 CPU 定时器 0 以遵循模型的基本速率。 当使用 ADCINT1 替换调度程序中断源时(如本例所示),用户有责任确保 ADCINT1 以模型中使用的基本速率定期触发。 该模型展示了一种使用 ADC 转换结束中断来调度多速率控制器算法的先进技术。 该技术对于本示例是有效的,因为我们已将模型配置为以与控制器算法中指定的采样时间相同的周期速率生成 ADC 转换结束中断。 如果不确保这种采样一致性,生成的代码的行为将与模拟的行为不同。

(Embedded Coder® Support Package for Texas Instruments™ C2000™ Processors:4-28)

13.8后处理模块

13.9开路/短路检测电路

13.10上电顺序

13.11ADC校准

13.12ADC时序

将模拟电压转换为数字电压的过程分为S+H阶段和转换阶段。ADC采样和保持电路(S+H)的时钟由SYSCLK提供,而ADC转换过程的时钟由ADCCLK提供。ADCCLK是根据ADCCTL2寄存器中的PRECALE字段对SYSCLK进行划分而生成的。

S+H持续时间为被转换SOC的ACQPS字段值加1乘以SYSCLK周期。用户必须确保此持续时间超过1个ADCCLK周期和数据表中指定的最小S+H持续时间。转换时间大约是10.5个ADCCLK周期。准确的转换时间总是SYSCLK循环数的整数。具体计时请参见13.12.1节中的计时图表和表格。

13.12.1 ADC时序图

- 以下图表显示了两个SOC在下列假设下的ADC转换时间:

- 将SOC0和SOC1配置为使用同一个触发器。

- 当触发器发生时,没有其他SOC在转换或挂起。

- 轮询指针处于SOC0先转换的状态。

- ADCINTSEL被配置为在SOC0转换结束时设置一个ADCINT标志(这个标志是否传播到CPU导致中断由PIE模块中的配置决定)

- 相关参数说明如表13-8所示。ADC时序如表13-9所示。

13.13其他信息

参考文献

1: TMS320F28004x Microcontrollers Technical Reference Manual (Rev. D).

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)