实战篇---Nios ii 基本操作

目录硬件搭建步骤1. 用自带的qsys工具产生嵌入式CPU软核1)配置nios ii的主时钟2)添加nios ii软核3)添加其他的IP核4)连线5)配置nios ii复位和异常地址。6)基地址分配7)终端号分配8)生成QSYS系统2. 用原理图将产生的嵌入式内核和FPGA其他程序PIN相连1)新建.bdf原理图文件...

目录

2. 用原理图将产生的嵌入式内核和FPGA其他程序PIN相连

工具:quartus 13.1(自带Qsys,eclipse)

quartus自带工具,包含QSYS以及ECLIPSE。因为生成一个SOPC(片上可编程系统,在quartus中也叫NIOS嵌入式软核,在新版本的quartus中也称为platform designer),包含硬件电路和软件程序两部分。 硬件部分通过QSYS搭建一个硬件系统(一个系统包含CPU、时钟、存储器、外设以及系统ID号),通过相关的现成IP核搭建,相当于可编程在FPGA上实现。软件部分通过quartus自带的eclipse编辑器生成用于CPU处理器工作的code。生成的处理器不是只有NIOS II一种,还有其他的CPU,只要满足FPGA内部的设计即可。

通过内部已经集成的IP核,可以快速构建SOPC。SOPC之间的部件连接叫内部互联总线,遵循的avalon协议,例如avalon-MM(又分master 和slave端),avalon-ST等。如下:

硬件搭建步骤

1. 用自带的qsys工具产生嵌入式CPU软核

1)配置nios ii的主时钟

不同的FPGA IC所支持的nios ii 最大时钟频率不同,需查看手册。

如上图,library为qsys封好的IP核,可直接调用。先点击view打开时钟窗口,配置时钟的名称和频率。配置后,system contents里面的时钟会变为已修改的名称。system contents里面为配置的软核cpu的基本组成结构。

如上图,library为qsys封好的IP核,可直接调用。先点击view打开时钟窗口,配置时钟的名称和频率。配置后,system contents里面的时钟会变为已修改的名称。system contents里面为配置的软核cpu的基本组成结构。

2)添加nios ii软核

如下图,点击embedded processors--> nios processors,再点击add。

Nios II/e 占用资源最少 ,功能也最简单,速度最慢。Nios II/s 占资源比前者多一些,功能也多了,速度也快一些。 Nios II/f 占资源最多,功能也最多,速度就快。选择时候要根据你的需求和芯片资源来决定。

选择指令 cache 和数据 cache 的大小;

其余均可选择默认做简单的配置。

3)添加其他的IP核

例如RAM,System ID Peripheral 核,JTAG UART 核。

在library上方的搜寻窗口里搜On-ChipMemory(RAM or ROM),再ADD添加。在Total memory size"窗口中输入 40960(即片上内存的大小设置为 40KB),其余选项保持默认。

这里有一个连线的规则:如果是存储器这类的 IP 核,需要将其 Slave 端口同 Nios II 的 data_master 和instruction_master 相连;而其它非存储器 IP 核则只需要连接到 Nios II 的data_master 即可。

System ID 是一种标示符,起校验的作用,以防止 Quartus 和 Nios 程序版本不一致的错误发生。

JTAG UART 对 Nios II 的软件调试非常方便,可以实时的打印和输出调试信息。

4)连线

点击下图中圆点,浅灰色线变成黑色,表示连接成功。将各个模块的clk和data线分别连接,并连接复位信号线。点击主界面菜单栏中的"System"下的"Create Global Reset Network",会自动将各个模块的复位信号相连。

5)配置nios ii复位和异常地址。

在Nios II Processor 的配置界面,配置 Reset Venctor 和 Exception Venctor 为"onchip_ram.s1" 。Reset Vector 是复位后启动时的 Memory 类型和偏移量,就像STM32中,系统上电后先去读取flash的首地址一样。 Exception Vector 是异常情况时的 Memory 类型和偏移量。需要 SDRAM 和 FLASH设置好以后才能配置,这个很重要。

6)基地址分配

点击主界面菜单栏中的"System"下的"Assign Base Address。"Base"栏将自动分配基地址,模块之间不会出现重复的地址。

7)中断号分配

在"IRQ"标签栏下点击"Avalon_jtag_salve"和 IRQ 的连接点就会为"jtag_uart"核添加一个值为 0 的中断号。如下图所示:

8)生成QSYS系统

点击"Generation"标签栏中 Generate 按钮生成 Qsys 系统。

2. 用原理图将产生的嵌入式内核和FPGA其他程序PIN相连

1)新建.bdf原理图文件

2)添加 Qsys 组件到项目顶层文件

在 top_level.bdf 原理图的空白处双击,将已经生成的Project 目录下的 kernel 加入到原理图中来。

3)加入 Quartus II IP File 文件

为了以后的编译成功,将对应的 Quartus II IP File(.qip)加入到项目中。如下图所示:

4)添加PLL

在 top_level.bdf 的空白处双击,弹出 Symbol 对话框中点击 MegaWizard Plug-In Manager。如下图:配置速度等级为8,与IC相对应。配置时钟50M,与外部晶振一致。最后选择pll_inst.v生成IP核,其余可默认。

然后添加PLL到原理图上。

5)进行逻辑连接和生成管脚

用工具栏中的 Diagonal Node Tool 将 PLL 模块的 c0 与 kernel 模块的 clk_clk 相连接;

在 PLL 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚;

在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚。

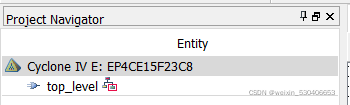

6)芯片配置和引脚配置

如下,右键选择device-->device and pin options-->修改 Dual-Purpose Pins 为 Use as regular I/O,设置 Voltage 里的 I/O 电压为 3.3-V LVTTL(与外部电路供电一致)。

7)编译 Start Compilation

8)Pin planner配置

配置IC引脚,时钟和复位。

软件配置

1. Eclipse项目创建

1)选择菜单 Tool->Nios II Software Build Tools for Eclipse 打开 Nios II SBT forEclipse 软件开发环境。

2)Workspace 选择当前的项目的 software 目录下,点击 OK。

3)建立新的软件应用,选择菜单 File->New->Nios II Application and BSP fromTemplate。使用工程模板来建立应用程序和 BSP 库。BSP库是用于让程序在硬件上运行的板级支持包。

4)在 SOPC Informaction File name 栏中点击浏览按钮选择 kernel.sopcinfo 文件后打开。

5)在 Project name 处输入项目名称,点击finish结束。

6)完成后返回 Eclipse 主界面,在 Project Explorer 界面里会出现项目工程和 BSP 的库文件。

2. 编写代码并编译

1).c文件编写code后,先编译一下工程,右键选择 项目,选择 Build Project。

2)编译成功后在 Console 窗口显示 Build Finished 的信息。

调试

1. 先下载 FPGA 的硬件配置文件到开发板

1 )连接 JTAG 下载器到开发板,确定 A.JTAG 下载器的驱动安装成功。B.计算机的防火墙不会影响到 JTAG 的正常工作。最后开发板上电。

2)选择菜单 NiosII->Quartus II Programmer;

3)在 Programmer 界面里点击 Add File..按钮来添加 FPGA 配置文件;

4)选择.sof文件,下载到开发板上;

2. 下载.elf文件

1)下载完成后返回 Eclipse 主界面,右键选择 项目,再选择 Run As->3Nios II Hardware

2)转到"Target Connection"标签栏。

3)点击右边的 Refrensh Connections 按钮(需要把窗口拉大一些才能显示这个按 钮),界面中会出现 USB-Blaster。

4)点击 Apply 后,点击 Run。完成后会出现一个 Nios II Console 窗口。当您在以下的窗口看到红色框内的文字,恭喜您基于 Qsys 系统的 Nios II 程序已经运行成功。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)