使用Verdi或DVE分析波形的一些小技巧

本文记录使用Verdi或DVE查看Delta Cycle的方法和分享一些分析波形的小技巧。

本文记录使用Verdi或DVE查看delta cycle的方法和分享一些分析波形的小技巧。

文章目录

查看Delta Cycle的方法

Verilog和SV的仿真调度机制

在仿真时可能会遇到一些设计和验证平台之间竞争冒险的问题。Verilog有一套仿真调度机制,一个时间片(time-slot)被分为Active, Inactive, NBA 区域,可以理解为分别主要用于阻塞赋值、零延时操作和更新非阻塞赋值。SystemVerilog又在这一基础上将设计和验证平台的事件分开调度,在同一时间片之后引入了Observed, Reactive, Postpone 区域,分别执行断言、验证平台和输入采样。SV-2017的IEEE标准中展示了完整的time slot region划分,如下图所示。

一个时间片可分为无限小的delta cycle,其时间精度比最小单位 fs 还小,在使用Verdi或DVE仿真时,可以通过查看delta cycle来分析硬件仿真和验证平台间的准确时序前后关系。

使用Verdi查看Delta Cycle的方法

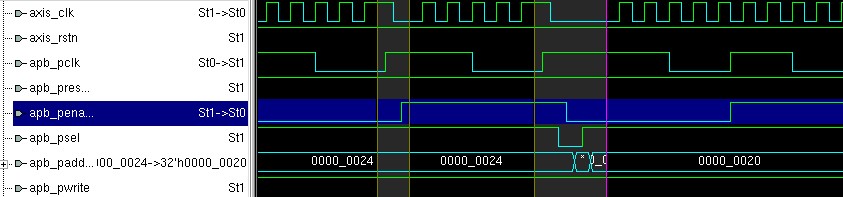

一个非常简单的例子如下,APB总线是在每周期第二个pclk采到penable的高电平,而非在第一个pclk,那么怎么通过波形上确认呢?在使用VCS仿真时,可以在仿真simv命令后添加选项 +fsdb+region。

用Verdi打开fsdb波形后,打开波形窗口 View 选项下的"Region mode",然后点击 Expand/Collapse Time at Cursor,或直接选中波形按w键。

然后就可以看到仿真时刻的delta cycle,并且选中还可以看到当前时刻所在的region。这里绿色区域为Active Region,红色区域为NBA Region。借助event region可以很好理解为何是在第二个pclk采到penable高电平。

另外,也通过选择 Tools -> Event Sequence 来显示图形化的事件序列,效果如图所示。

使用DVE查看Delta Cycle的方法

在VCS仿真命令中添加 -gui 参数即可调用DVE仿真。DVE也可以在仿真进行时观察波形,这里如果没有事先存储波形文件的话,需要在 run 命令前执行"dump -add /*“命令,对全部或指定层次的波形采样。这里给出同样一个APB总线的例子。

在波形窗口打开 Simulator 选项下的 Capture Delta Cycle Values。

然后在波形对应时间点,右键选择"Expand Time”,即可看到展开了的delta cycle。

Verdi的一些其他小技巧

总线拆分

选中信号右键 -> Bus Operation -> Expand ad Sub-bus,可以将多比特bus选取特定位宽拆分成sub-bus,或者直接在弹出对话框的 Every 项内输入n值,按每n个bits拆分。

事件统计

选中信号并截选时间段 -> 点击菜单选项 View -> Signal Event Report,可以看到在特定时间段内信号的上升、下降沿次数、频率、占空比等信息,方便统计。

逻辑运算

选中信号右键 -> Logical Operation,可以产生一个新的信号,对选中信号做一些逻辑运算。如可以判断一个地址何时低12位为0。

修改参数显示进制

Verdi顶层 Tools 选项 -> Preferences -> Source Code -> View Options -> Parameter Value Radix,可以把parameter从默认二进制显示替换成如16进制,方便查看。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)