开源EDA工具 OpenLANE 使用报告

OpenLANEOpenLANE简介OpenLANE(https://github.com/The-OpenROAD-Project/OpenLane) 是一个完成自动将RTL转换成GDSII 文件的流处理的开源项目,它包含了几个重要的开源组件包括OpenROAD,Yosys,Magic,Netgen等负责流程中的各个部分,注意这里的OpenROAD和开源EDA工具链OpenROAD项目(http

目录

OpenLANE

OpenLANE简介

OpenLANE(https://github.com/The-OpenROAD-Project/OpenLane) 是一个完成自动将RTL转换成GDSII 文件的流处理的开源项目,它包含了几个重要的开源组件包括OpenROAD,Yosys,Magic,Netgen等负责流程中的各个部分,注意这里的OpenROAD和开源EDA工具链OpenROAD项目(https://github.com/The-OpenROAD-Project/OpenROAD)是不同的,这里的OpenROAD是后者OpenROAD项目中的一个组件,即OpenROAD App,负责一部分后端开发。

RTL => GDSII流程中所需要的各个组件以及各种库组成了PDK,即Process Design Kit 工艺设计包,它是将RTL转换成物理芯片的关键,要想制造芯片,必须使用PDK。谷歌公司和工艺代工厂SkyWater于2020年共同宣布推出了以后者的PDK为主要部分的开源开发套件,开发者在一定的规则下可以免费使用,还利用这套PDK来开发芯片,甚至有机会获得免费流片的机会,这套PDK工艺虽然不是特别先进(180/130 nm),但是对于研究机构和个人来说有着重要的意义,因为使用付费PDK的价格是非常高昂的。

OpenLANE 是由谷歌赞助的Efabless 公司负责维护的一个开源项目,包含了上面所介绍的Skywater-PDK以及一些其它开源PDK组件。可以完成RTL到GDSII 的全流程,比我们第二部分将要介绍的 OpenROAD 项目出现的时间还要新一些,这一部分实验正是基于 OpenLANE 完成芯片的全流程实验,最终得到我们需要的GDS。

实验过程

环境准备

实验需要在Linux环境下开展,可以本地使用虚拟机软件,操作系统是Ubuntu 20.04.2 LTS,注意有条件的话,最好分配不低于20GB的硬盘和不小于4GB的内存,处理器也多多益善,原因后面会介绍到。

需要说明的是,实验一开始我使用的是Ubuntu 14.04.6 LTS 版本,实际证明是错误的选择。系统配置完毕以及安装必要的软件后,安装 docker ,安装完毕运行下面的命令验证 docker 的有效性:

安装OpenLANE

首先分别执行下面的命令:

git clone https://github.com/efabless/openlane.git

cd openlane/

sudo make openlane

sudo make pdk

sudo make test这个过程中遇到的最大问题就是 git clone 的速度太慢,而要clone的文件量是庞大的,因为要将Skywater-PDK,一些库和 open_pdks 以及docker 容器下载到本地,,在执行 sudo make pdk 的过程中,由于要clone 一些子模块,速度问题变得更加的严重:

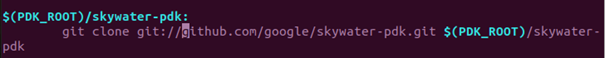

解决办法就是将makefile文件中的类似 https://github.com/ 中的https通通替换为git,这样就可以提升下载速度:

当然还有修改后执行 sudo make pdk还有可能发生clone错误,此时可以到新生成的 pdks/skywater-pdk/.git/config 文件中继续替换操作:

下载安装过程时间很长,可能发生内存溢出的错误:

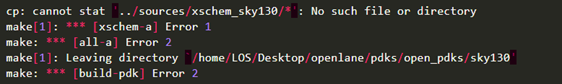

此时重新执行sudo make pdk 命令即可。还有可能出现下面的错误:

解决这个问题时发现github 上该项目的issues 中有人也遇到了这个问题: openlane-issue:297 ,没有很好的解决方法,大概是一种系统BUG,因为开始时使用的是 Ubuntu 14.04.6 LTS 版本,所以只能重新安装 Ubuntu 20.04 LTS,重新执行上面的步骤,由打印信息可知,完成skywater-pdk的安装后开始 open_pdks的下载:

如果还发生 clone 问题,可以对 open_pdks/sky130下的Makefile 文件进行 https 到 git的替换操作:

注意下面生成magic database 的过程很长,会停顿在这里,但是实际上还是在执行的:

最后安装成功后执行的是测试命令,测试环境是否安装成功:

如果配置成功的话,可以发现./designs/spm/runs/openlane_test/results/magic/spm.gds 以及同名的png照片文件生成。因为 OpenLANE 同时使用 Magic 和 Klayout 两种生成gds 文件的方式,Klayout作为备用方式,最后还会对两者输出的结果进行对比,所以在results/klayout文件夹下也可以看到新生成的gds文件:

证明安装成功。

make test 报错的解决过程

由于 OpenLANE 还是一个比较新的项目,bug 也比较多,所以经常出现一些低级的错误,如果 make test 可以顺利执行,就可以跳过下面的这一小节了,而且这个问题在记录时已经得到了解决。

中间遇到的一个问题就是虽然正常生成了GDS文件,但是在做检查流程时出错,输出信息为:

在完成GDSII 生成后进行了四步检查:

由输出信息可知,在进行CVC检查时出错,缺少了一个变量,变量名为:

::env(STD_CELL_LIBRARY_CDL)

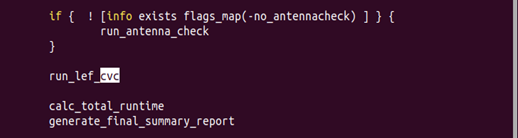

根据打印信息我们知道,根调用者为 根目录下的flow.tcl文件,它负责指挥整个运行过程,文件中与CVC检查有关的部分是下图光标处:

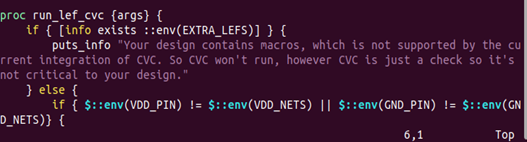

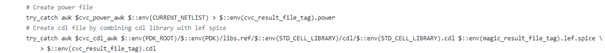

对应的函数在./scripts/tcl_commands/cvc.tcl文件中定义:

CVC主要做电路有效性检查,与缺少的变量有关的语句是该文件中的这一部分,代码的意思是当执行try 后面的语句出错时就会抛出错误:

这时发现了github上该项目有一个相关的还没有解决的同样问题的 issue:openlane-issue:362,被标记为 bug:

![]()

因为我使用的是最新版本v0.16版的OpenLANE,所以我考虑能否从之前版本的该文件中检查一下该变量的用法,发现v0.15中并没有该变量:

v0.16版本中引入了该变量,为了理解tcl文件中代码的意思,可以学习一下tcl文件的语法,实际上这段代码只是做了用这个新定义的变量替换了一长串变量字符而已,开发者的意图应该是让这个变量可以由使用者在使用时自己赋值,所以有set_if_unset 设置默认值:

但是我在运行时发生错误,说明这个默认值并没有起到默认值的作用,所以try 后面的语句没有执行成功,抛出了错误。

所以想到了最简单的方法就是用v0.15中的写法替换掉当前版本的写法,结果执行成功:

我也参与到了这个 issue 的讨论过程,比较幸运的是发现这个问题的第二天,引入这个bug的开发者@ahmednofal也注意到了这个问题,修正了这个错误并pull request到该项目,他将没有起到作用的set_if_unset 替换成了下面的表达方法,改成下面的写法后可以执行测试并起到了可由使用者自己定义的功能:

我在issue上review并支持了他的fix,拥有项目管理权限的Efabless公司的开发者赞同了我的review,并merge了该request,该issue openlane-issue:362 目前已经成为已解决closed的状态,截止目前版本更新为v0.17。

通过这个过程可以看到,在使用开源工具时,积极利用issue等板块进行讨论,可以帮助实现问题的解决,及时修补bug,这也是开源软件的重要意义之一。

测试 OpenLANE 提供的其它design

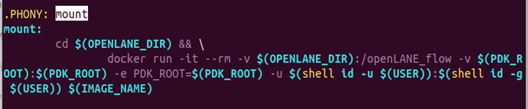

使用make test时默认测试的设计是spm,现在我们对OpenLANE的designs目录下提供的其它设计进行测试,首先我们可以看看make test 做了哪些工作,查看项目根目录下的Makefile文件:

可以看到利用docker镜像和OpenLANE执行了相应的设计流程。

官方提供的执行指定设计的命令如下,design_name就是designs文件夹下的各个设计对应文件夹的名称:

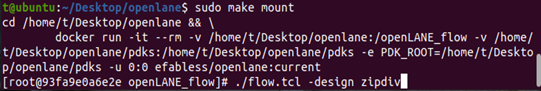

sudo make mount

./flow -design <design_name>可以看到Makefile文件中对mount的定义,启动了docker容器:

我们以zipdiv为例进行测试:

运行结果如下:

可以看到成功执行,我们可以在/designs/<design_name>/runs/xxx/results/klayout或magic下找到对应design生成的gds文件:

除此之外还测试了xtea等设计,但是当我们对picorv32a进行测试时出现了错误:

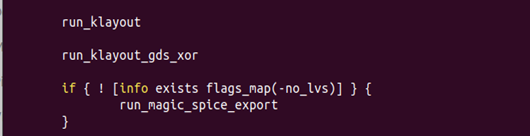

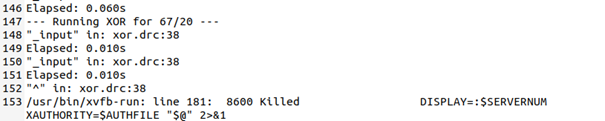

由报错信息可知是在使用klayout进行xor操作进行比较时产生错误,此时实际上已经生成了gds文件。

./flow.tcl中有下面xor函数调用:

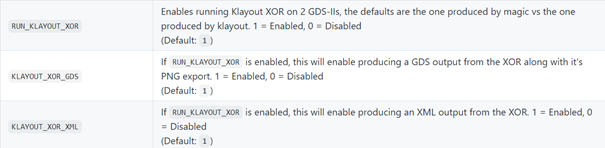

由官方文档可知,xor操作对magic和klayout生成的gds文件进行了相应操作,并生成了一个新的gds文件输出:

通过错误提示的相应输出日志/designs/picorv32a/runs/22-05_01-13/logs/klayout/34-klayout.xor.log

而正常的其它设计的该日志应该是:

可以看出可能是Xvfb出现问题,Xvfb是一个类似于提供虚拟桌面的软件,尝试了重新安装等方法,都没有实现,可以判断不是Xvfb出现问题,尝试重新执行,在执行的过程中通过监视系统,发现执行过程对内存的消耗非常大:

所以本来虚拟机只分配了2G内存,后来又分配了3G内存,成功完成了执行:

输出的gds文件为:

同还可以查看results/klayout下的picorv32a.xor.gds文件:

加入一个开源 design

上面使用的是OpenLANE本来自带的design,下面我们加入网上获得的其它design,因为做实验最开始的时候使用过OpenROAD开源项目,所以就使用了一个它包含的一个简单设计gcd:gcd源码链接。

新加入其它的设计之前,首先要了解一下OenLANE中的配置文件,OpenLANE中的配置文件主要包括三个部分:

- PDK / technology specific

- Flow specific

- Design specific

第一种PDK配置文件主要针对的是标准单元库的变量的定义,它定义在下面的文件中:

$PDK_ROOT/$PDK/config.tcl

标准单元库有很多种,包括:

- sky130_fd_sc_hd

- sky130_fd_sc_hs

- sky130_fd_sc_ms

- sky130_fd_sc_ls

- sky130_fd_sc_hdll

所以在特定的标准单元库类型下又有自己的额外的变量定义,甚至可以覆盖了PDK配置文件中的定义:

$PDK_ROOT/$PDK/$STD_CELL_LIBRARY/config.tcl

第二种对于 flow 配置文件,包含了 flow 过程中的默认变量定义,可以设置某些步骤是否进行以及一些参数的具体值,它主要包含在下面的文件夹中

./configuration/

我们可以看看该文件夹下配置文件general.tcl 里的变量设置,注意下面设置了默认标准单元库是 sky130_fd_sc_hd:

比如下面的 ::env(RUN_CVC)如果设置为0就可以不用进行CVC检查了:

第三种对于每个design都有自己的config.tcl文件,包含了必须设置的变量以及可以选择的变量,design 自己的变量可以覆盖掉上面两种配置文件中的变量值:

./designs/<design>/config.tcl

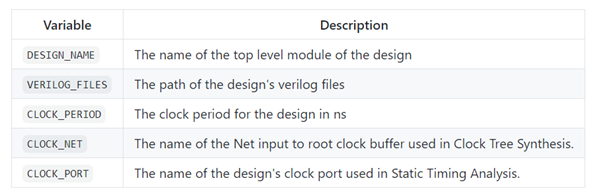

必须包含的变量包括:

其它可以设置的变量可以查看:变量列表链接

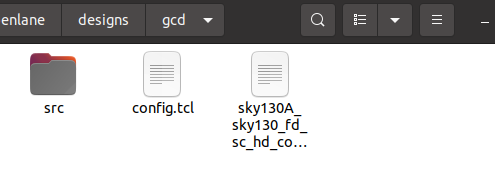

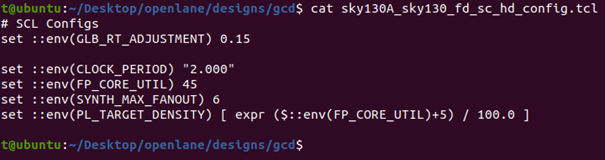

知道了配置文件我们就可以开始加入开源设计了,首先在designs目录下新建文件夹gcd,在gcd文件夹下创建src目录和config.tcl,src目录用来放RTL代码,还要创建sky130A_sky130_fd_sc_hd_config.tcl文件,用来指定标准单元库的相应变量,因为我们默认使用sky130_fd_sc_hd单元库,这是在前面提到的gerneral.tcl中规定的。如果用其它库要创建其它文件:

接着编辑config.tcl,要包含前面提到的必须的5种变量,注意DESIGN_NAME以及CLOCK_PORT的名称要和代码中的名称一致,SDC_FILE指定了src目录下的相应文件作为sdc约束文件,文件的最后指定了标准单元库的配置文件,就是同一目录下的sky130A_sky130_fd_sc_hd_config.tcl:

导入源代码,设置sdc文件:

下面介绍一下对sdc文件的理解,就是生成了一个名为clk,周期为2的时钟。

下面是sky130A_sky130_fd_sc_hd_config.tcl的内容,可以拷贝OpenLANE其它设计的该配置文件,也可以在这个文件中设置时钟周期变量:

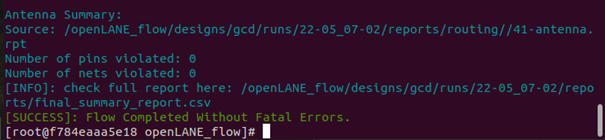

接着执行 sudo make mount,./flow.tcl -design gcd 即可,成功执行:

生成的gds文件为:

此时就完成了加入一个新的design的操作。

没有解决的问题

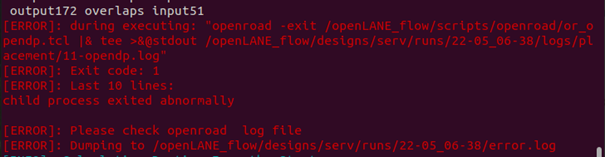

下面介绍一些没有解决的问题,在尝试添加一个新的 design 即 serv 时报错:serv源地址:

报错显示是在进行detailed placement 操作时出现错误,这个问题在github上也有相应的issue: openlane-issue:321,没有得到解决,有回答提到有时这个问题会自动解决。

另外还有可能因为内存不足,导致一些设计的执行没有显著错误提示却会卡在某一步,所以尽量地为虚拟机分配较大的内存。

总结

本文简单介绍了 OpenLANE 的使用方法,OpenLANE 和另一个开源 EDA 工具 OpenROAD 很相似,甚至很多工具直接来源于 OpenROAD,限于篇幅,本文只是简单的对 OpenLANE 的入门教程,如果想要深入的学习使用,可以查看项目官方地址以及教程。

OpenLANE 出现的时间比 OpenROAD 要晚一些,它的基本组成成除了包括OpenROAD项目的核心组件外,还来自于 YosysHQ 和 Open Circuit Design 等项目的开源组件,除此之外它还加入了Skywate-pdk,其中的标准单元库对flow过程是非常有价值的。两者的开源社区都有一定的活跃度,且获得了相当有分量的公司或机构的赞助,相信两者都会为芯片设计开源事业做出自己的贡献。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)