低功耗验证 (二)UPF,低功耗流程,VCS NLP

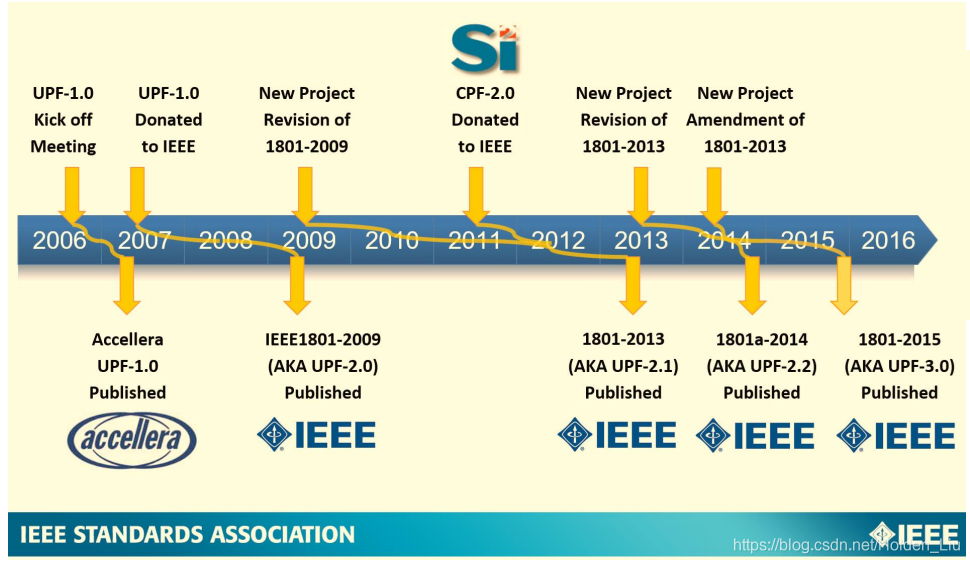

UPFUnified Power Format (UPF) 用于定义power intent的标准,基于TCL语言编写。目前,最新版的UPF为UPF3.0 1801-2018。UPF文件主要包含4部分内容:power domain, power state, low power cell rule, PG connection。power domain: 对特定的RTL instance做电源管理

UPF

Unified Power Format (UPF) 用于描述power intent(供电意图)的标准,基于TCL语言编写。

目前,最新版的UPF为UPF3.0 1801-2018。

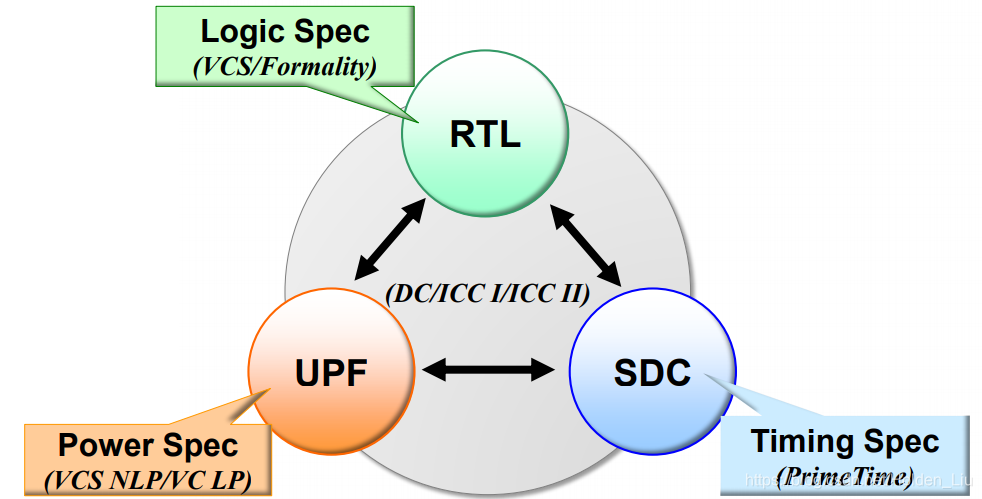

SDC时序约束为Timing Spec;UPF为 POWER DESIGN SPEC,传递给后端作为输入文件,需要保证其为 Golden File。

UPF文件主要包含4部分内容:power domain, PG connection,low power cell rule,power state 。

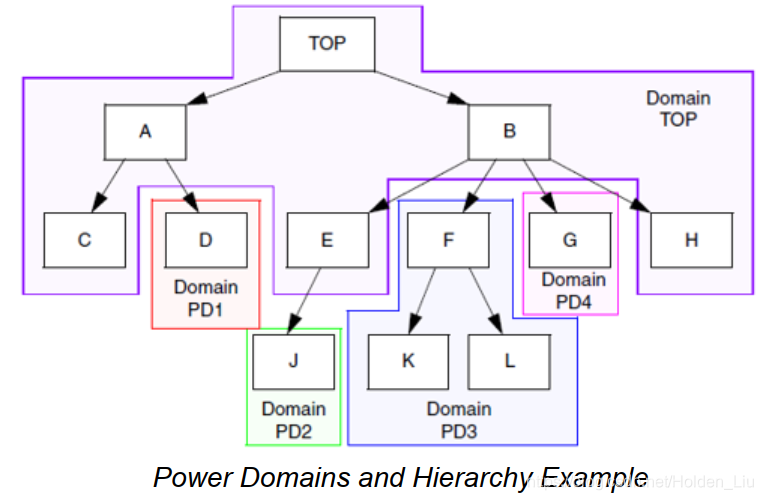

power domain: 对特定的RTL instance做电源管理,可以将其单独定义为一个domain,需要primary net供电。物理实现为voltage area。

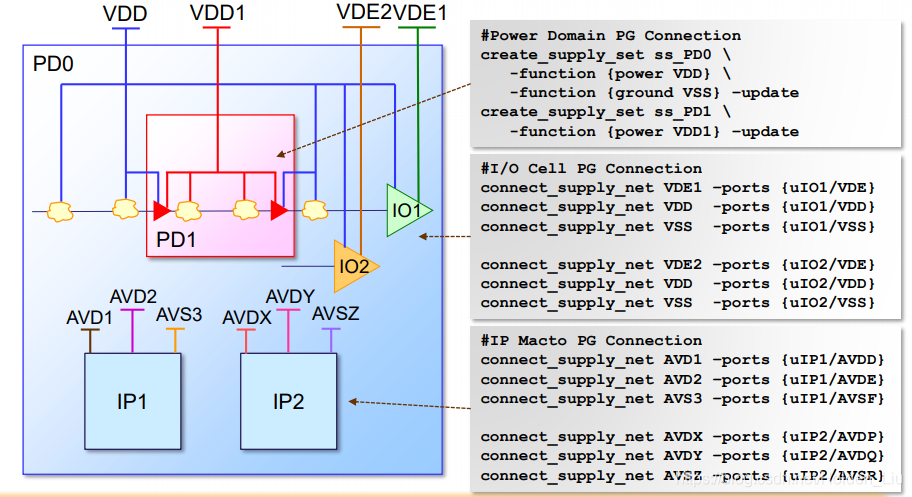

PG connection: 通过supply net或者supply set构建power network电源网络,给各个power domain, IP Macro, I/O cell供电。物理实现为power rail。supply port供电端口。

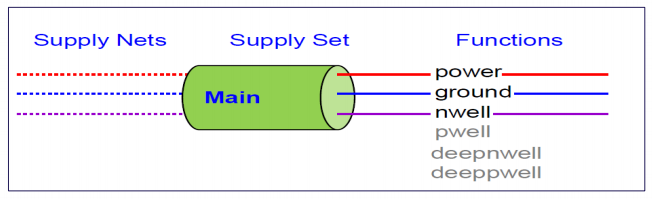

在UPF2.0中引入了supply set的概念,是supply net的抽象集合。

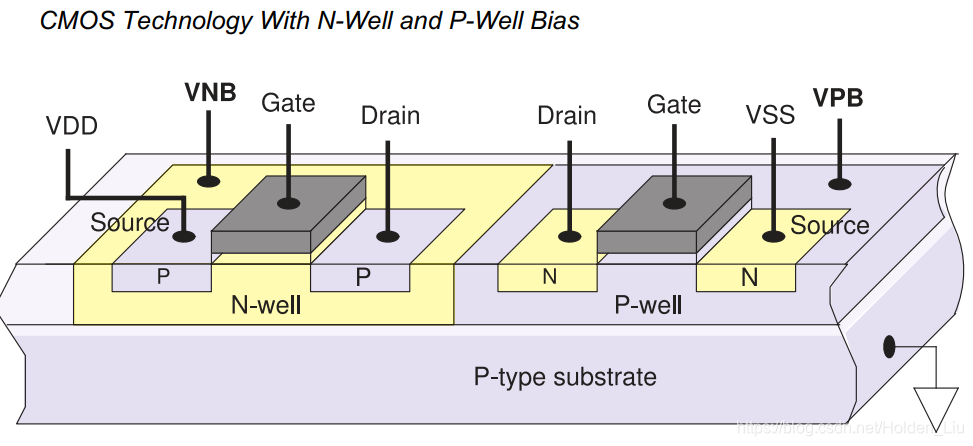

对于一个MOS管,供电端必须有power Pin, ground Pin;在一些其他的低功耗策略中,如Body Bias中,还会对nwell,pwell,deepnwell,deeppwell做额外处理。所以supply set作为supply net的集合,对于供电网络的描述更佳友好。

VNBPin对nwell供电,VPBPin对pwell。

low power cell rule:对于level shifter,isolation,retention register,power switch cell的行为描述。如level shifter从高到低还是从低到高,isolation cell钳位的高低电平,power switch的控制信号等。

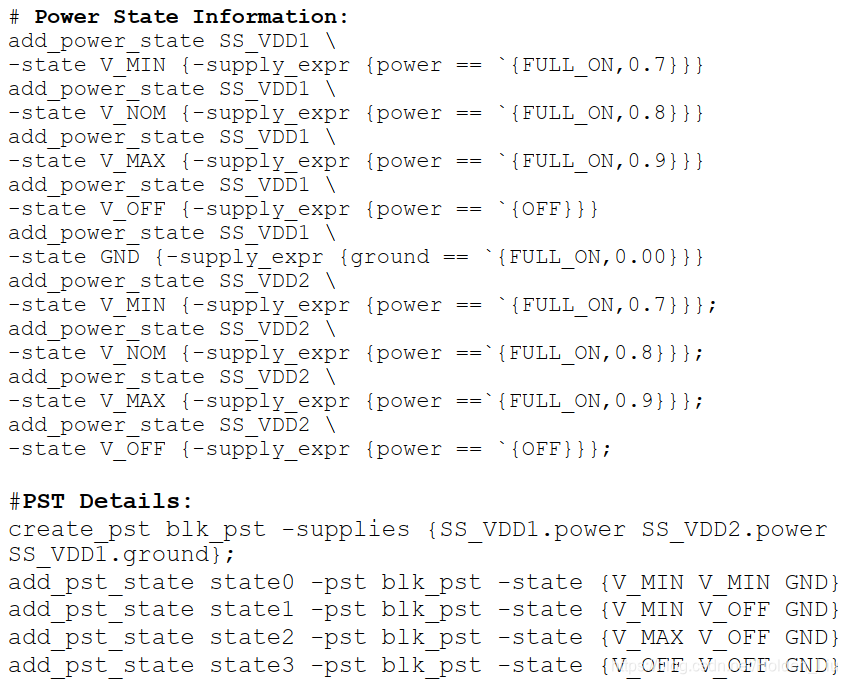

power state:Chip的一种供电模式,是特定条件下supply net的供电组合。

可以通过create_pst创建PST power state table,并作覆盖率分析。

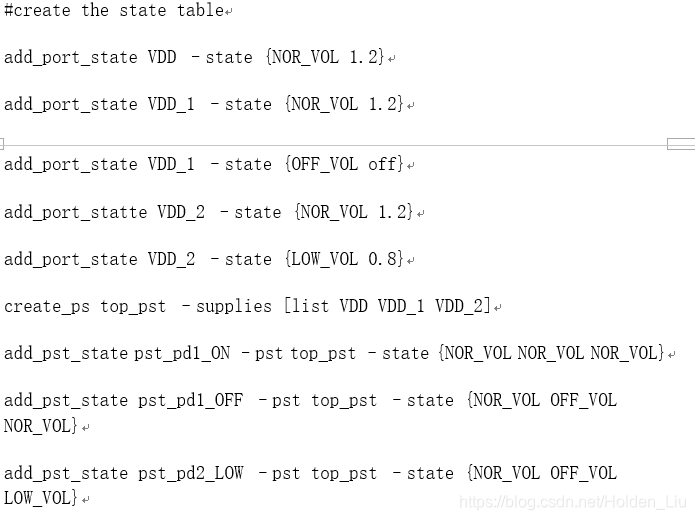

PST有两种方式,一种是add_power_state,将power_state加入PST(recommend):

另一种是add_port_state,将port_state加入PST(legacy):

power sate也可以用于创建Power Model。对于超大项目,需要在pre-RTL阶段,在软件应用层做架构探索,对性能,功耗,面积评估(Shift left and constant visibility)。

VPU Power Model示例:🔗5G Mobile SoC Pre-RTL Power/Performance Optimization

整个UPF的编写和维护,根据实际项目需求,编写SPEC-2-UPF的脚本,自动生成UPF文件,减少工作量和书写错误。

🔗An innovative and efficient approach for… UPF files

Low Power Simulation

Tools

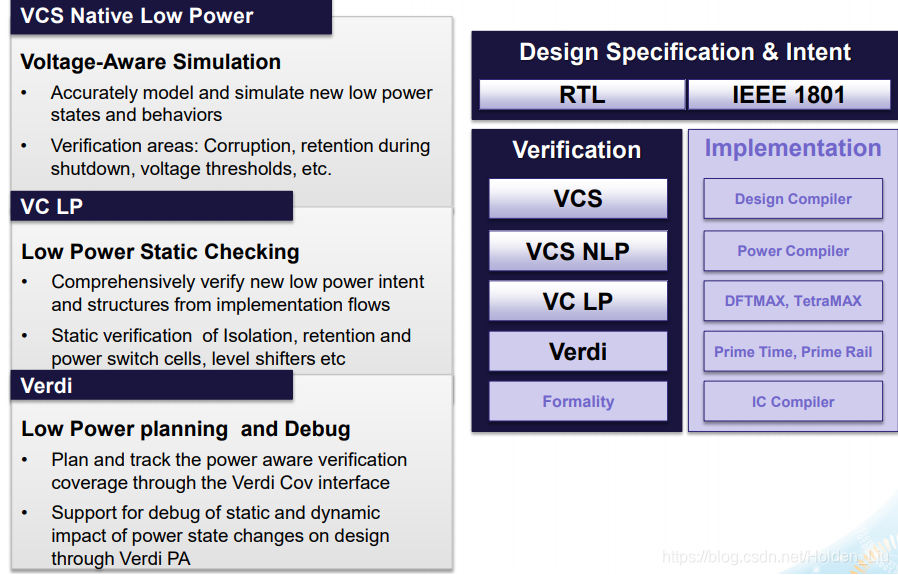

VC LP: low power的静态检查工具,用于Static Verification。以 UPF/PST 作为 Golden 去检查 UPF 本身的一致性,以及检查设计/网表是否有缺少/冗余的低功耗器件,包括检查带有电源地信息的网表里面电源/地的连接是否和 UPF 的设计意图一致,等等,一般由UPF实现工程师完成,是 LP 验证检查的第一步。VC LP涉及LP实现的整个流程,为动态仿真和逻辑综合提供一个"干净“的UPF(Hand-off前),保证最后的UPF实现与最初的设计意图一致(Sign-off前)。

VCS NLP: VCS Native Low Power 支持VCS带UPF/CPF的Power-Aware的仿真,用于Dynamic Verification。Power-Aware就是仿真工具可以根据UPF对RTL model实现power-up,power-down,以及retention, isolation, and level shifting等功能,相当于插入虚拟的power cell来实现low power simulation。(VCS NLP天然集成了 low power simulation功能,以往的方式是采用 MVSIM工具,一款协同仿真器(Co-Simulator),同 VCS协同仿真)

vcs -upf <upf file>指定UPF文件即可实现带UPF的仿真。

Verdi Power-Aware Debug: dump POWER相关信息后,verdi也支持Power-Aware的debug。🔗低功耗验证 (三) Verdi Power-Aware Debug简单使用

其余的一些工具,如Design Compiler,IC Compiler,Formality,PrimeTime 等非Verification tool不在深入研究。

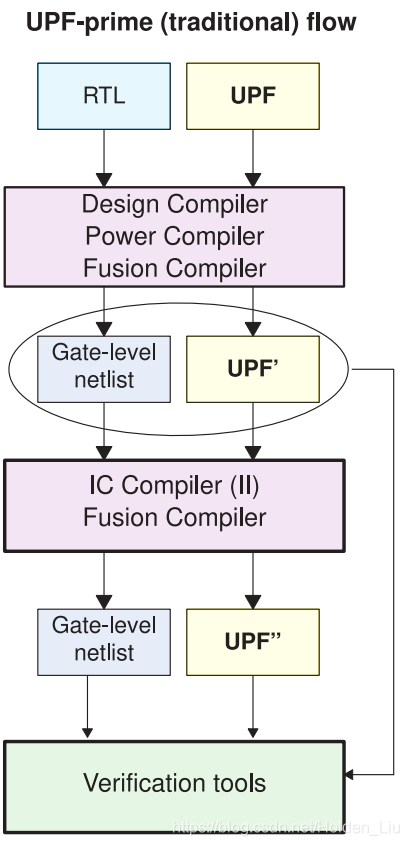

Low Power Flow

Synopsys® 推荐的UPF-flow如下图所示,仿真涉及三个阶段,逻辑综合前RTL+UPF,逻辑综合后Gate-level netlist + UPF’,物理实现后Gate-level netlist + UPF" 或者Gate-level netlist with PG pin。UPF file作为Golden file,贯穿整个流程,指导工具实现。( 相比 traditional flow,Snps推荐的 Golden UPF Flow,工具会额外生成 supplemental UPF,可以参考🔗Golden UPF Flow Application Note)

Original RTL + UPF

在逻辑综合之前,RTL model中还没有插入Low Power cells(isolation cells, level shifters, retention registers, or power switches) 和 power and ground (PG) net。VCS NLP根据UPF插入虚拟cells和net,实现Power Aware功能。

Gate-Level Netlist + UPF’

使用DC逻辑综合后,产生UPF’ (UPF prime),此时网表插入了isolation cells,level shifters,retention registers,但是PG net和power switches还没有。这一阶段的仿真,需要gate-level netlist,UPF’ file以及 .db file。(.db是binary格式,描述 Cell 每个 Pin 和电源直接的依赖关系,由test格式的.lib转化得到)根据项目需求,这个阶段的仿真不是必须要做的。

Gate-Level Netlist + UPF’’ 及 PG Netlist

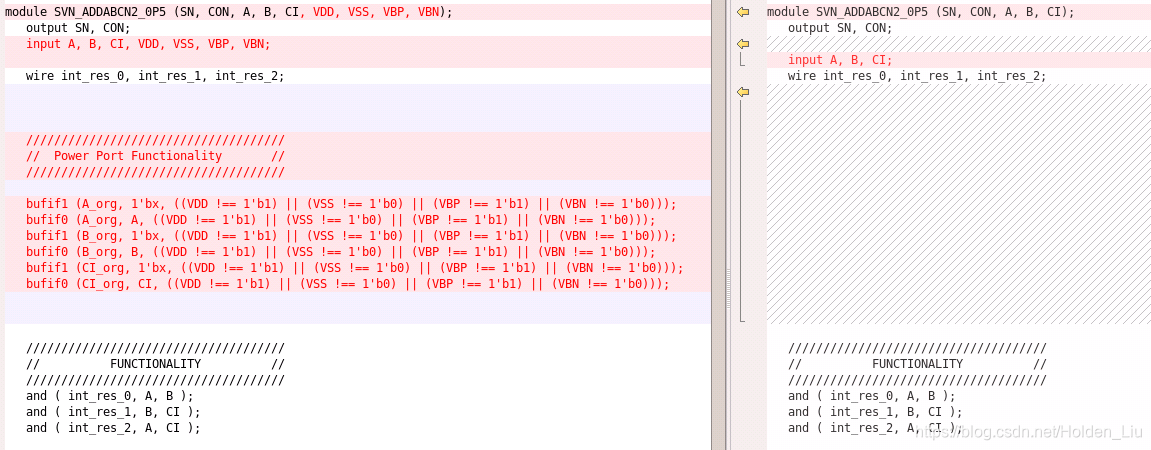

经过IC Compiler,IC Compiler II, 或者 Fusion Compiler布局布线后,会产生UPF" (UPF double-prime)。这时没有必要使用VCS NLP跑带UPF" 的仿真了,可以直接跑PG Netlist的仿真。PG Netlist包含UPF中定义的各种low power cells以及PG pin组成的供电网络。PG Netlist是Power-Aware的,直接使用vcs仿真。

带PG pin的std cell多了VDD VSS VBP VBN四个PG pin,下电条件下通过三态门bufif1驱动x态,上电则正常导通,实现Power-Aware:

VCS-NLP Simulation

▶将顶层testbench创建为一个power domain,作为一个虚拟的always on domain。

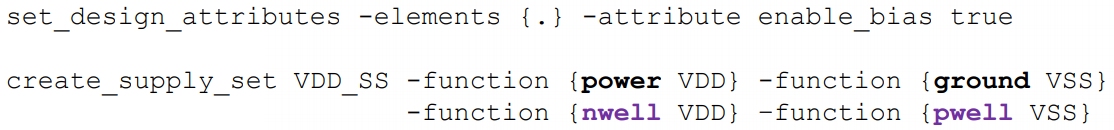

▶ set_design_attributes设定属性。例如-attribute UPF_dont_touch TRUE设置为不受UPF掉电影响,为always_on状态。-attribute enable_bias TRUE使能bias functions。更多属性参考手册。

▶数字部分由模拟部分控制上下电,可以在UPF中加入power switches来模拟LDO/DC-DC的行为。

▶对于power sequence的time delay,例如power switch打开后,多久关闭isolation。可以根据后端结果评估设置一个安全时间cycle delay或者使用power switch的ack_port做判断。

▶domain的供电来自供电端口,可以通过add_port_state定义端口电压,也可以通过调用supply_on supply_off的方式控制。默认power_net 为 { FULL_ON, 1.0000V} ground_net为 {OFF, 0.0000V}。

▶Supply States: OFF, UNDETERMINED,PARTIAL_ON, FULL_ON四种状态。

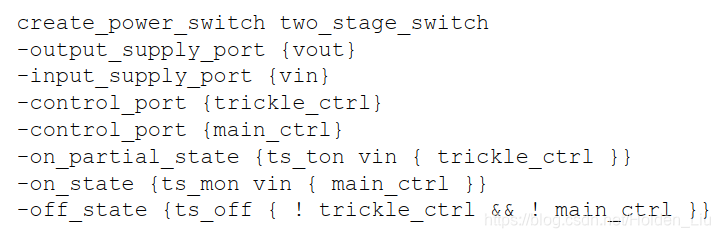

示例:power switch 两个 control,input supply port为FULL_ON时,trickle_ctrl打开,output supply port为PARTIAL_ON,main_ctrl打开,为FULL_ON状态。若控制信号出现X态或者高阻态,则为UNDETERMINED不确定状态。

▶vcs_reinit

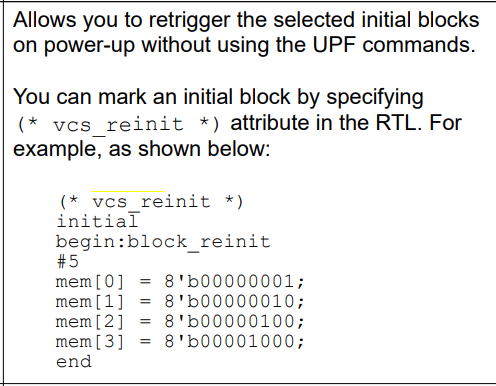

对于ROM,实际掉电数据不会丢失;但是仿真时掉电仿真器不会保存ROM中的数据。可以手动monitor上电信号赋初值或者通过vcs_reinit自动再次触发initial blocks。

也可以在upf中通过命令行控制:set_design_attributes -elements <element_list> -models <model_list> -attribute SNPS_reinit TRUE

▶Monitor Power Domain State

第一种:power domain下电时,内部信号(4-state variables)呈X态。根据是否为X态,监测是上电状态还是下电状态。

第二种:monitor power_state_simstate。

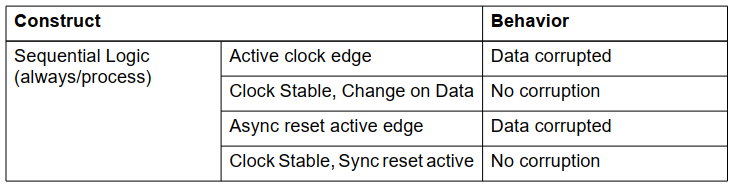

NORMAL,CORRUPT,CORRUPT_ON_ACTIVITY,CORRUPT_STATE_ON_CHANGE,CORRUPT_STATE_ON_ACTIVITY5种类型的simstate。若没有额外声明,默认NORMAL上电,CORRUPT下电两种状态。

*vcs_always_on*需要配合编译命令-power=attributes_on使用,保证不受掉电影响。

也可以在testbench中先通过bind RTL module的方式加入,然后再通过XMR(Cross-Module References)的方式直接monitor simstate,避免掉电影响。

`ifdef UPF_POWER_AWARE

import UPF::*;

power_state_simstate upf_simstate;

(*vcs_always_on*)

always @(upf_simstate) begin

if (upf_simstate == CORRUPT)

begin

$display ($time , "SNPS =>DOMAIN IS CORRUPT");

end

else if (upf_simstate == NORMAL)

begin

$display ($time , "SNPS => DOMAIN IS ON");

end

else

begin

$display ($time , "SNPS => DOMAIN IS NON-ON and NON-CURRUPT STAGE");

end

end

`endif

CORRUPT_STATE_ON_CHANGE就是low-vdd stnady的操作,降低vdd,减少漏电流,但不至于存储电平丢失。此时不可以进行存储的访问操作,否则数据丢失。

第三种:Power Aware Verification Environment (PAVE) is an infrastructure that enables accessing the UPF objects, monitor low power events, and write power-aware assertions.

PAVE内建访问UPF object的API,使用TCL语言编写,在编译选项中–lpa_bind xxx.tcl bind。需要一些学习成本。

▶Log and Report:

VCS-NLP仿真会实时打印power相关的log,WARING,ERROR的需要清理。默认生成mvsim_native_reportsreport目录。

▶覆盖率收集:-power=coverage会根据UPF文件自动收集PST states, Power switch,Supply net/port/transitions等低功耗相关的覆盖率。

也可以-power=cov_pst+cov_psw+cov_iso+cov_pd_simstate+cov_port_state+cov_supply_set手动选择需要收集的覆盖率条目。

合并覆盖率:urg -full64 -dir coverage/cov.vdb/ -dbname mergedir/merged

打开覆盖率:verdi -cov -codir mergedir.vdb

▶VCS除了支持功能仿真,低功耗仿真外,还支持SPICE模拟部分仿真与X-Propagation X态传播(🔗X态详解 与 X态传播 VCS X-Propagation)。

SNUG上两篇 Best Paper Award 的Paper:

Power-Aware下的数模混仿🔗Power aware simulation for Analog-Mixed Signal design

Power-Aware下的X态传播:🔗Is X-optimism burning my low power design

Lower Power Verification

-

Power sequence

不同power mode之间的切换;PMU中fsm的遍历;CPU 执行WFI指令请求下电;isolation操作在下电前,上电后; -

Wakeup interrupt

不同条件下,从SLEEP MODE唤醒,如Pin Wakeup,RTC Wakeup,IP Wakeup等。 -

Memory retention testing

重新上电后,retention mem的数据保持不变。 -

Assertion checker

assertion domain power down/up; Free-running clocks/gated clocks; Analog model signal assertion; isolation ctrl and power down/power up sequence assertion;clamp value check; -

Formal Verification

- protocol compliant check : LPI(Low Power Interface,Q-channel/P-channel)protocol

- parameters, tie-offs and connectivity check : the propagation of parameters, the value of tie-offs, the connectivity of combinatorial logic

- deadlock check : no specific sequencing errors prevent power transitions

- livness checks : activity on any of the Q-channels will always result in power transitions from a low to a high state

- other functional point suitable for Formal

-

Collect and Analysis Power Coverage

-

Clean model and sim log error

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)