简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

RVV intrinsic API 可查询 rvv-intrinsic-doc/auto-generated/intrinsic_funcs.adoc。本文档列出RVV intrinsic function的用例,仓库中也提供相同的用例,我们可以拉取下来,然后进行测试。qemu没有预编译好的版本,需要自己手动编译,为了方便,这里我们选择qemu-user模式。接下来,单步调试这个RVV函数,并查看

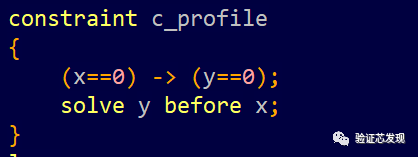

总的来看,使用->或者if-else时,参数的概率分布会变得复杂且不易理解,尤其涉及到多条件蕴含时,某些参数的概率分布很难做出预期,因此更加需要后续的功能覆盖率加以分析,找出不合理的约束。

0. 引言在UVM支持的寄存器操作中,有get、update、mirror、write等等一些方法,在这里整理一下他们的用法。 寄存器模型中的寄存器值应该与DUT保持同步,但是由于DUT的值是实时更新的,所以寄存器模型并不能实时知道这种更新,在寄存器模型中专门有个值来尽可能与DUT中寄存器的值保持一致,叫镜像值(mirrorred value)。寄存器模型中还有一个值叫期望值(desired v

http://www.testbench.in/https://verificationacademy.com/ mentor的学习论坛,里面有UVM cookbook同时还包含练习代码以及testbench的模板代码...

第一种:直接在tc中例化sequence,通过调用star函数指定sequencer启动。my_sequence my_seq;my_seq = my_sequence::type_id::create("my_seq");my_seq.start(sequencer); ## 括号中是sequencer的例化路径,也可以使用m_sequencer(m_sequencer为sequenc.....

I2C七宗罪(连载) (点击文章题目,即可阅读往期精彩) I2C第七罪 由于前段时间工作上的事情比较杂乱, 导致第七罪姗姗来迟,既然是大结局,当然就应该让大家更加深刻的来理解I2C.。我们先来复习一下大家共有的对I2C的认知: 1. I2C的SCL(Clock)总是由Master来驱动; 2. I2C的SDA (Data)则不同,Master和Slave分别都驱动。 这两点想必读者都没

要随机产生一个4bit的 -1 ~ -7的数:val = $urandom_range(-1,-7);要随机产生一个4bit的 0 ~ -7的数:val = $urandom_range(-0,-7); // 这样写错误需要写成std::randomize(val) with { val inside {0,[9:15]};};参考:https://www.cnblogs...

传统的Veriog仅仅支持文字表述上的字符串, 而SystemVerilog将字符串作为了内建的数据类型。类似C++的std::string类型,SystemVerilog字符串类型支持很多操作和函数。SytemVerilog字符串类型支持的操作和方法:一些有用的系统任务SytemVerilog字符串类型支持的操作和方法操作...

Cadence以前覆盖率收集的工具是Incisive Comprehensive Coverage (ICC),现在整合到IMC中了。使用IMC首先要加载 mdv(MDVMAIN)模块在Makefile的run命令后加上覆盖率收集相关配置:-covfile xxx.f #配置imc相关内容xxx.f 示例内容,具体参考 cdnshelp 内容:select_coverage -...