AD9361 官方例程详解(一)

文章目录前言一、pandas是什么?二、使用步骤总结前言一、pandas是什么?二、使用步骤总结

文章目录

- 前言

- 一、 Device selection、Identification number、Reference Clock、Base Configuration

- 二、 ENSM Control、 LO Control 、Rate & BW Control、 RF Port Control 、TX Attenuation Control 、 Reference Clock Control

- 三、Gain Control、Gain MGC Control、Gain AGC Control、Fast AGC、FAGC - Low Power、FAGC - Lock Level、FAGC - Peak Detectors and Final Settling、FAGC - Final Power Test、FAGC - Unlocking the Gain

- 四、RSSI Control

- 五、Digital Interface Control

- 六、GPO Control 、Tx Monitor Control 、GPIO definitions、MCS Sync、External LO clocks

- 七、AD9361_RXFIRConfig rx_fir_config 、AD9361_TXFIRConfig tx_fir_config

前言

AD9361 官方例程中,NO-oS ,AD9361_InitParam结构体中配置参数含义

一、 Device selection、Identification number、Reference Clock、Base Configuration

1.1 Device selection

ID_AD9361 ,// dev_sel :器件选择,可配置为ID_AD9361,ID_AD9364,ID_AD9363A

1.2 Identification number

0 ,// id_no :设备编号,

1.3 Reference Clock

40000000UL , // 参考时钟频率 40 MHz

1.4 Base Configuration

0 , //two_rx_two_tx_mode_enable , 2Rx2Tx 模式使能,AD9364必须是0,我现在用的1Rx1Tx

1 , //one_rx_one_tx_mode_use_rx_num,仅在1Rx1Tx模式下对AD9361和AD9363有效(AD9364只有一个RX和一个TX通道) ,选择使用哪个RX通道进行接收

1 , //one_rx_one_tx_mode_use_tx_num ,仅在1Rx1Tx模式下对AD9361和AD9363有效(AD9364只有一个RX和一个TX通道),选择使用哪个TX通道进行发送

1 , //frequency_division_duplex_mode_enable ,使能FDD模式

0 , //frequency_division_duplex_independent_mode_enable ,FDD independent模式(AD9361 介绍 (中) 8.3节)使能

0 , //tdd_use_dual_synth_mode_enable ,TDD模式下,双射频合成器模式使能。0,在任何给定时间只有一个射频合成器是打开的,当设置1时,两个合成器总是开着。(AD9361包含两个相同的RFPLL合成器来产生所需的LO信号,一个用于Rx通道,另一个用于Tx通道。)

0 , //tdd_skip_vco_cal_enable ,TDD模式下从TX / RX转移到Alert时可以选择跳过VCO cal。某些情况下,如快速锁定合成器模式,VCO校准可以屏蔽(禁用),如果TDD中的LO频率不随帧变化,就没有必要每次都重新校准VCO。

0 , //tx_fastlock_delay_ns,

0, //rx_fastlock_delay_ns 和tx_fastlock_delay_ns,设置了电荷泵电流,环路滤波器的R1, R3和C3在fast lock期间改变到最终值之前保持其初始值的时间,范围为0 ns到63.75 μs。

0, //rx_fastlock_pincontrol_enable ,这个位为1,CTRL_IN0到CTRL_IN2引脚将选择Rx快速锁定配置文件。这个位为0,寄存器Rx Fast Lock Setup (0x25A)[D7:D5]位选择快速锁定配置文件。

0, //tx_fastlock_pincontrol_enable ,同rx_fastlock_pincontrol_enable

0, //external_rx_lo_enable ,使能外部LO对Rx路

0, //external_tx_lo_enable ,使能外部LO对Tx路

5, //dc_offset_tracking_update_event_mask ,详见寄存器DC Offset Config2(0x18B)D2-D0位,这些位指定了DC偏移量更新条件

6, //dc_offset_attenuation_high_range ,RX LO>4 GHz:这些位控制衰减器,用于初始化和跟踪射频直流偏移校准。

5, //dc_offset_attenuation_low_range,RX LO<4 GHz:这些位控制衰减器,用于初始化和跟踪射频直流偏移校准。

0x28, //dc_offset_count_high_range ,RX LO>4 GHz:这个值影响RF DC偏移初始化和跟踪,并设置集成采样数和环路增益,增加此值将增加环路增益

0x32, //dc_offset_count_low_range ,RX LO<4 GHz:该值影响RF DC偏移初始化和跟踪,并设置集成采样数和环路增益,增加该值将增加环路增益。

0, //split_gain_table_mode_enable,使能Split增益表模式,0为Full Table模式

MAX_SYNTH_FREF, //trx_synthesizer_target_fref_overwrite_hz ,RF PLL 参考时钟频率 最好在10-80MHz选大的值,REF_CLK_IN为40MHz,乘2得到80MHz

0, // qec_tracking_slow_mode_enable,改进的RX QEC跟踪,以防感兴趣的信号接近 DC/LO

二、 ENSM Control、 LO Control 、Rate & BW Control、 RF Port Control 、TX Attenuation Control 、 Reference Clock Control

2.1 ENSM Control

0, //ensm_enable_pin_pulse_mode_enable ,ENSM (ENABLE/TXNRX)引脚控制 脉冲模式使能,0为电平模式,详见(AD9361 介绍 (中) 8.2节)

0, //ensm_enable_txnrx_control_enable ,ENSM(ENABLE/TXNRX) 引脚控制使能, 0为SPI 写控制ENSM

2.2 LO Control

2400000000UL, //rx_synthesizer_frequency_hz,RX LO上电频率(Hz)

2400000000UL, //tx_synthesizer_frequency_hz,TX LO上电频率(Hz)

1, //tx_lo_powerdown_managed_enable ,LO断电管理使能,寄存器0x050和0x051 D4位

2.3 Rate & BW Control

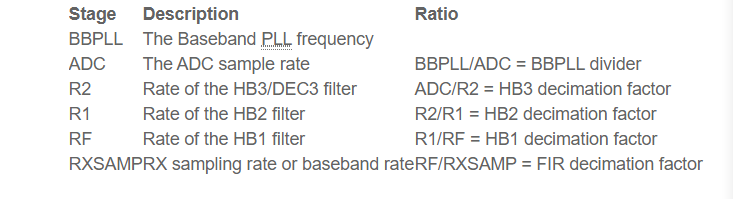

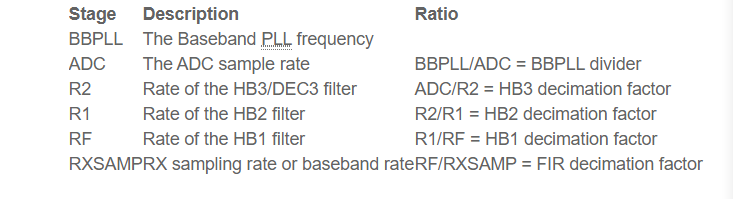

{983040000, 245760000, 122880000, 61440000, 30720000, 30720000},// rx_path_clock_frequencies[6],RX路径频率(Hz)

{983040000, 122880000, 122880000, 61440000, 30720000, 30720000},// tx_path_clock_frequencies[6] ,TX路径频率(Hz)

18000000,//rf_rx_bandwidth_hz ,RX RF带宽上电设置

18000000,//rf_tx_bandwidth_hz,TX RF带宽上电设置

2.4 RF Port Control

0, //rx_rf_port_input_select , 射频端口输入选择

0, //tx_rf_port_input_select , 射频端口输出选择

2.5 TX Attenuation Control

10000, //tx_attenuation_mdB ,TX加电衰减(毫分贝),10 mdB

0, //update_tx_gain_in_alert_enable ,为1时,在TDD模式下,禁用即时TX增益更新,直到ENSM移到 Alert 状态

2.6 Reference Clock Control

0, //xo_disable_use_ext_refclk_enable ,为1时,禁用XO 使用 外部时钟 到 XTAL_N

{8, 5920}, //dcxo_coarse_and_fine_tune[2] ,DCXO精调和粗调,详见AD9361 介绍 (中) 7.1节

CLKOUT_DISABLE, //clk_output_mode_select,CLKOUT模式选择,详见 AD9361 介绍 (终) 12.2.1节

三、Gain Control、Gain MGC Control、Gain AGC Control、Fast AGC、FAGC - Low Power、FAGC - Lock Level、FAGC - Peak Detectors and Final Settling、FAGC - Final Power Test、FAGC - Unlocking the Gain

3.1 Gain Control

对比AD936x 配置软件介绍 下,更容易理解下面所设置的参数意义

2, //gc_rx1_mode ,RX1增益控制模式:手动增益(0);Fast AGC(1);Slow AGC(2);Hybrid AGC(3)

2, //gc_rx2_mode ,RX2增益控制模式:手动增益(0);Fast AGC(1);Slow AGC(2);Hybrid AGC(3)

58, //gc_adc_large_overload_thresh ,设置 large ADC overload,寄存器0x105

4, //gc_adc_ovr_sample_size,设置确定ADC过载的ADC输出样本数。见寄存器0x0FC,位[D2:D0]。

47, //gc_adc_small_overload_thresh ,设置 small ADC overload,寄存器0x104

8192, //gc_dec_pow_measurement_duration ,增益控制算法使用的功率测量持续时间。见寄存器0x15C,位[D3:D0]

0, //gc_dig_gain_enable ,为1时,在split 表模式下启用数字增益指针。参见寄存器0x0FB,位D2,0不使用数字增益

800, //gc_lmt_overload_high_thresh ,设置large LMT过载阈值。见寄存器0x108。

704, //gc_lmt_overload_low_thresh ,设置small LMT过载阈值。见寄存器0x107。

24, //gc_low_power_thresh ,LOW power threshold : -24 dBFS, 范围为0 dBFS至-63.5 dBFS。fast AGC使用该阈值来确定是否应该增加增益。这个阈值也可以用来触发MGC模式下的CTRL_OUT信号转换。见寄存器0x114,位[D6:D0]。

15, //gc_max_dig_gain ,设置最大允许数字增益,适用于所有增益控制模式,见寄存器0x100的位[D4:D0]。

3.2 Gain MGC Control

2, //mgc_dec_gain_step, 在CTRL_IN信号控制增益时,当某些CTRL_IN信号跳变为高电平时,增益索引减小此值。参见寄存器0x0FE的位[D7:D5]。

2, //mgc_inc_gain_step ,在CTRL_IN信号控制增益时,当某些CTRL_IN信号跳变为高电平时,增益索引增加此值。参见寄存器0x0FC的位[D7:D5]。

0, //mgc_rx1_ctrl_inp_enable ,为0时,SPI写操作更改RX1增益。为1时,CTRL_IN引脚将控制增益。参见寄存器0x0FB的位[D0]。

0, //mgc_rx2_ctrl_inp_enable ,为0时,SPI写操作更改RX2增益。为1时,CTRL_IN引脚将控制增益。参见寄存器0x0FB的位[D1]。

0, //mgc_split_table_ctrl_inp_gain_mode ,MGC模式, CTLR_IN 信号控制, split表模式下,AGC确定增益变化(0);仅LPF增益变化(1);仅LMT增益变化(2)。参见寄存器0x0FC的位[D4],[D3]。

3.3 Gain AGC Control

10, //agc_adc_large_overload_exceed_counter , 该计数器指定 large ADC过载发生次数,发生的过载次数超过该值后,减小设定的增益步长。参见寄存器0x122的位[D7:D:4]。

2, //agc_adc_large_overload_inc_steps ,用于AGC,决定 split 表模式下的 large LPF过载或全表模式下的large LMT和large ADC 过载的增益变化量。参见寄存器0x106的位[D3:D0](名称具有误导性,应为dec-steps)

0, //agc_adc_lmt_small_overload_prevent_gain_inc_enable ,为1时,如果发生 small LMT或small ADC 过载,防止增益增加。参见寄存器0x120的位[D7]。

10, //agc_adc_small_overload_exceed_counter ,该计数器指定 small ADC过载发生次数,发生的过载次数超过该值后,减小设定的增益步长。参见寄存器0x122的位[D3:D0]。

4, //agc_dig_gain_step_size ,如果发生digital saturation,数字增益将降低此值。参见寄存器0x100的位[D7:D5]。

3, //agc_dig_saturation_exceed_counter ,该计数器指定digital saturation事件发生次数,发生的次数超过该值后,减小设定的增益步长。参见寄存器0x128的位[D3:D0]。

1000, // agc_gain_update_interval_us ,增益更新计数器配置为1000 us

0, //agc_immed_gain_change_if_large_adc_overload_enable ,设为1时,large ADC过载立即降低增益,忽略增益更新计数器。参见寄存器0x123的D3位。

0, //agc_immed_gain_change_if_large_lmt_overload_enable ,设为1时,large LMT过载立即降低增益,忽略增益更新计数器。参见寄存器0x123的D7位。

10, //agc_inner_thresh_high ,slow AGC 控制环路 inner threshold high: -10 dBFS

1, //agc_inner_thresh_high_dec_steps ,超过inner threshold high后,增益减少步长

12, //agc_inner_thresh_low ,slow AGC 控制环路 inner threshold low: -12dBFS

1, //agc_inner_thresh_low_inc_steps ,低于inner threshold low后,增益增加步长

10, //agc_lmt_overload_large_exceed_counter 该计数器指定 large LMT过载发生次数,发生的过载次数超过该值后,减小设定的增益步长。参见寄存器0x121的位[D7:D:4]。

2, //agc_lmt_overload_large_inc_steps,确定split 表模式下large LMT的增益变化或full 表模式下small ADC过载的增益变化。参见寄存器0x103的位[D4:D2]。

10, //agc_lmt_overload_small_exceed_counter ,该计数器指定 small LMT过载发生次数,配合其他寄存器,可以防止增益增加。参见寄存器0x121的位[D3:D0]。

5, //agc_outer_thresh_high ,slow AGC 控制环路 outer threshold high: -5 dBFS

2, //agc_outer_thresh_high_dec_steps ,超过outer threshold high后,增益减少步长

18, //agc_outer_thresh_low,slow AGC 控制环路 outer threshold low: -18 dBFS

2, //agc_outer_thresh_low_inc_steps ,低于outer threshold low后,增益增加步长

1, //agc_attack_delay_extra_margin_us, AGC Attack Delay可防止AGC在接收路径建立之前开始其算法,使接收路径在AGC启动之前稳定。当ENSM进入Rx状态时,延迟计数器启动,范围:0-31微秒。参见寄存器0x022的位[D5:D0]。

0, //agc_sync_for_gain_counter_enable ,1时,则CTRL_IN2转换为高电平会将增益更新计数器复位,参见寄存器0x128的D4位。

3.4 Fast AGC

64, //fagc_dec_pow_measuremnt_duration ,增益控制算法使用的功率测量持续时间。参见寄存器0x15C的位[D3:D0]。

260, //fagc_state_wait_time_ns,Energy Detect Count 配置为260 ns ,4个 Rx samples, 如果该时段没有检测到峰值过载,fast AGC可以从状态1进入状态2。Energy Detect Count 以ClkRF时钟频率(Rx FIR滤波器输入端使用的时钟)计时,参见寄存器0x117的位[D4:D0]。

3.5 Fast AGC - Low Power

0, //fagc_allow_agc_gain_increase ,为1时 Enable Incr Gain 位为1,如果平均信号功率低于低功率阈值的时间大于增量时间,进入State 2A, AGC 增加增益。 后续我们不使用Enable Incr Gain 位,配0。参见寄存器0x110的D0位。

5, //fagc_lp_thresh_increment_time ,增量时间 5 Rx samples :fast AGC改变增益之前信号功率必须保持在低功率阈值以下的时间。也可以由MGC使用。参见寄存器0x11B的位[D7:D0]。

1, //fagc_lp_thresh_increment_steps ,如果信号功率降低到“低功率阈值”以下,并且仅在启用“Enable Incr Gain ”的情况下,快速AGC才会将增益索引增加此步长值。参见寄存器0x117的位[D7:D5]。

3.6 Fast AGC - Lock Level (Lock Level is set via slow AGC inner high threshold)

1, //fagc_lock_level_lmt_gain_increase_en ,为1时,如果在移至AGC锁定电平时需要增加增益索引,则允许AGC使用LMT增益。参见寄存器0x111的D6位。

5, //fagc_lock_level_gain_increase_upper_limit ,fast AGC用于锁定电平时,可调整的增益索引最大增加值。参见寄存器0x118的位[D5:D0]。

3.7 Fast AGC - Peak Detectors and Final Settling

1, //fagc_lpf_final_settling_steps ,增益索引减小值,如果在锁定电平后但在fast AGC状态5之前发生large LMT或large ADC过载时。如果过载次数超过了“Final Overrange Count”(fagc_final_overrange_count),则AGC算法将重新启动。如果使用split表,则取决于各种条件,增益可能会降低LPF或 LMT步长(fagc_lmt_final_settling_steps)。参见寄存器0x112的位[D7:D6]。

1, //fagc_lmt_final_settling_steps,“Post Lock Level Step for LMT Table”。参见寄存器0x113的位[D7:D6]。

3, //fagc_final_overrange_count ,“Final Overrange Count”。参见寄存器0x116的位[D7:D5]。

3.8 Fast AGC - Final Power Test

0, //fagc_gain_increase_after_gain_lock_en ,低功率测试 ,为1时 ,可在增益锁定后但在状态5之前增加增益。信号功率必须低于低功率阈值,且持续时间大于增量持续时间。参见寄存器0x110的D7位。

3.9 Fast AGC - Unlocking the Gain

0, //fagc_gain_index_type_after_exit_rx_mode , AD9361退出Rx State, AGC将增益重置为:MAX Gain (0); Optimized Gain(1); Set Gain(2)。参见寄存器0x110的D4,D2位。

1, //fagc_use_last_lock_level_for_set_gain_en ,配置1时,将前一帧的最后的增益索引用于Set Gain。0时使用上一帧的第一个增益索引。参见寄存器0x111的D7位

1, //fagc_rst_gla_stronger_sig_thresh_exceeded_en ,为1时,并且fast AGC处于状态5,则信号功率增加的幅度超过“Stronger Signal Threshold”,增益解锁。参见寄存器0x115的D7位。

5, //fagc_optimized_gain_offset , Optimize Gain Offset,上一次突发最后一个 AGC 增益锁定索引 加 Optimize Gain Offset,结果就是optimize gain索引。参见寄存器0x116的位[D3:D0]。

10, //fagc_rst_gla_stronger_sig_thresh_above_ll ,如果信号功率增加了此阈值,并且信号功率保持在此水平或更高,持续时间为Gain Lock Exit Count的两倍,则增益可能会解锁,具体取决于其他AGC配置位。参见寄存器0x113的位[D5:D0]。

1, //fagc_rst_gla_engergy_lost_sig_thresh_exceeded_en ,为1时,并且fast AGC处于状态5,则平均信号功率下降的幅度大于Energy Lost Threshold寄存器,增益解锁。参见寄存器0x110的D3位。

1, //fagc_rst_gla_engergy_lost_goto_optim_gain_en,为1时,并且fast AGC处于状态5,则在发生energy lost state或EN_AGC信号变高时,增益索引将达到 optimize gain 值。参见寄存器0x110的D6位。

10, //fagc_rst_gla_engergy_lost_sig_thresh_below_ll ,如果信号功率降低此阈值,并且信号功率保持在此水平或更低,且持续时间是Gain Lock Exit Count的两倍,则增益可能会解锁,具体取决于其他AGC配置位。参见寄存器0x112的位[D5:D0]。

8, //fagc_energy_lost_stronger_sig_gain_lock_exit_cnt ,“Gain Lock Exit Count”。参见寄存器0x119的位[D5:D0]。

1, //fagc_rst_gla_large_adc_overload_en ,为1时,如果Lg ADC Ovrg发生,解锁增益。参见寄存器0x110的位D1和寄存器0x114的位D7。

1, //fagc_rst_gla_large_lmt_overload_en ,fagc_rst_gla_large_adc_overload_en 和 该值 都为1时, 如果Lg ADC或LMT Ovrg发生,解锁增益。参见寄存器0x110的D1位。

0, //fagc_rst_gla_en_agc_pulled_high_en ,为1时,EN_AGC 拉高电平,增益将解锁,AGC算法将重新启动

0, //fagc_rst_gla_if_en_agc_pulled_high_mode ,EN_AGC 拉高电平,增益将解锁,AGC算法将重新启动,增益索引:MAX Gain(0); Optimized Gain(1); Set Gain(2),不改变增益。参见寄存器0x110、0x111

64, //fagc_power_measurement_duration_in_state5,功率测量持续时间,用在fast AGC 状态5(增益锁定)增益控制算法。参见寄存器0x109的位D7和0x10a的位[D7:D5]。

四、RSSI Control

4.1 RSSI Control

1, //rssi_delay ,1微秒,RSSI Delay,时钟频率为接收采样速率(Rx sample rate)8分频, 范围0到2040个 Rx samples

1000, //rssi_duration ,1000微秒,RSSI Duration 测量持续时间

3, //rssi_restart_mode,3,模式选择Gain change occurs

0, //rssi_unit_is_rx_samples_enable ,0时,RSSI单位是微秒,1时单位是rx_samples

1, //rssi_wait ,1微秒,RSSI Wait,时钟频率为接收采样速率4分频, 范围0到1020个 Rx samples

4.2 Aux ADC Control

4.2、4.3和4.4 见AD9361 介绍 (上) 第二部分

256, //aux_adc_decimation ,设置AuxADC抽取,参见寄存器0x01D位[D3:D1]。

40000000UL, //aux_adc_rate, 将AuxADC时钟频率设置为40000000Hz。参见寄存器0x01C的位[D5:D0]。

4.3 AuxDAC Control

1, //aux_dac_manual_mode_enable ,为1时,将 AuxDAC 设置为手动操作,也可以设置为在TDD 操作期间自动切换,以减少对 BBP 的控制要求

0, //aux_dac1_default_value_mV,DAC1默认电压(mV)

0, //aux_dac1_active_in_rx_enable,如果使能,DAC1在RX模式下处于活动状态

0, //aux_dac1_active_in_tx_enable ,如果使能,DAC1在TX模式下处于活动状态

0, //aux_dac1_active_in_alert_enable ,如果使能,DAC1在alert模式下处于活动状态

0, //aux_dac1_rx_delay_us ,RX 延时(us)

0, //aux_dac1_tx_delay_us ,TX 延时(us)

0, //aux_dac2_default_value_mV, DAC2默认电压(mV)

0, //aux_dac2_active_in_rx_enable ,如果使能,DAC2在RX模式下处于活动状态

0, //aux_dac2_active_in_tx_enable ,如果使能,DAC2在TX模式下处于活动状态

0, //aux_dac2_active_in_alert_enable ,如果使能,DAC2在alert模式下处于活动状态

0, //aux_dac2_rx_delay_us ,RX 延时(us)

0, //aux_dac2_tx_delay_us ,T X 延时(us)

4.4 Temperature Sensor Control

256, //temp_sense_decimation ,用于导出温度的AuxADC的抽取。

1000, //temp_sense_measurement_interval_ms ,测量间隔(以毫秒为单位)。

0xCE, //temp_sense_offset_signed ,偏移度为有符号 deg.C,范围-128…127

1, //temp_sense_periodic_measurement_enable ,启用定期测量

4.5 Control Out Setup

4.5和4.6详见AD9361 补充(下)

0xFF, //ctrl_outs_enable_mask ,Control Output Enable

0, //ctrl_outs_index *** adi,ctrl-outs-index,Control Output Pointer,范围0-31

4.6 External LNA Control

0, //elna_settling_delay_ns,外部LNA的建立延迟(ns)

0, //elna_gain_mdB

0, //elna_bypass_loss_mdB和elna_gain_mdB ,仅当(1)使用外部LNA且(2)增益表中的“ Ext LNA ctrl”位已编程时,elna_gain_mdB必须具有非零值。对于固定增益LNA,将elna-gain-mdB设置为LNA的增益,并将寄存器elna-bypass-loss-mdB的默认值保持为0。对于具有旁路模式的外部LNA,编程elna-gain-mdB使用“high gain(非旁路)值设置,并使用“low gain”(旁路)值编程elna-bypass-loss-mdB。该器件认为这两个值均代表AD9361之前的前端正增益。两个寄存器的范围为0至31500mdB,步长为500mdB。参阅下面两个elna-rx[1|2]-gpo[0|1]-control-enable,将外部LNA增益表位路由到GPO引脚。

0, //elna_rx1_gpo0_control_enable ,为1时,Rx1增益表中的“ Ext LNA Ctrl”位设置GPO0状态

0, //elna_rx2_gpo1_control_enable,为1时,Rx2增益表中的“ Ext LNA Ctrl”位设置GPO1状态

0, //elna_gaintable_all_index_enable ,为所有增益表中索引设置external LNA control位

五、Digital Interface Control

0, //digital_interface_tune_skip_mode ,跳过数字接口tune,0 =不跳过,1 =跳过TX tuning,2 =跳过RX 和TX并使用rx-data-clock-delay,rx-data-delay,tx-fb-clock -delay,tx-data-delay代替

0, //digital_interface_tune_fir_disable,FIR滤波器一旦启用,接口时序就会改变。如果时间间隔足够大,这通常不是问题。但是,在61.44 MSPS时,它会在某些系统上引起问题。一般在滤波器启用的情况下运行digital tune 。

1, //pp_tx_swap_enable ,为0时将交换I和Q(执行频谱反转)

1, //pp_rx_swap_enable ,为0时将交换I和Q(执行频谱反转)

0, //tx_channel_swap_enable,为1时将交换Tx1和Tx2样本的位置

0, //rx_channel_swap_enable ,为1时将交换Rx1和Rx2样本的位置

1, //rx_frame_pulse_mode_enable ,AD9361输出一个Rx帧同步信号,指示Rx帧的开始。为0时,Rx帧将与第一个有效的接收采样一致地变高,只要启用了接收器,它就会保持高电平。为1时,Rx帧信号以50%的占空比切换高低电平。

0, //two_t_two_r_timing_enable, 为1时,无论启用的发送器和接收器的数量如何,数据端口均使用2R2T时序。为0时,时序反映启用的信号路径的数量

0, //invert_data_bus_enable ,将数据端口从[11:0]转换为[0:11]

0, //invert_data_clk_enable,设置此选项将反转DATA_CLK

0, //fdd_alt_word_order_enable ,仅在全双工,双端口,全端口模式下有效。为1时,每个端口分成两个6位半端口。Rx1使用端口的6位,Rx2使用端口的其他6位(接收器不交错)。Tx1和Tx2的组织方式类似。

0, //invert_rx_frame_enable ,设置此选项会使Rx帧反转

0, //fdd_rx_rate_2tx_enable,为0时,Rx采样率等于Tx采样率。为1时,Rx速率是Tx速率的两倍。寄存器0x012的选项D3为0(全双工模式)时,才能设置此选项。

0, //swap_ports_enable ,为1时,将交换端口0和端口1。在LVDS模式下必须为0。

0, //single_data_rate_enable ,为0时,将使用DATA_CLK的两个边沿。为1时,仅使用的一个边缘

1, //lvds_mode_enable,为0时,数据端口使用单端CMOS。为1时,使用LVDS。

0, //half_duplex_mode_enable ,为0时,将允许同时双向数据。为1时,数据一次仅沿一个方向流动

0, //single_port_mode_enable,为0时,将同时使用P0和P1端口。为1时,仅使用一个数据端口。

0, //full_port_enable ,仅在全双工模式和双端口模式下使用。为1时,会强制接收器位于一个端口,发射器位于另一个端口。为0时,会混合每个端口上的接收器和发射器。

0, //full_duplex_swap_bits_enable,接收数据的比特和用于传输数据的比特之间切换使能,只有一个例外。如果设置了FDD Alt Word

Order位(0x011[D7]),则结果是用最低有效的6位交换最高有效的6位。

0, //delay_rx_data , 设置Rx数据相对于Rx帧的延迟,DDR时单位是 DATA_CLK的一半,SDR时单位是 DATA_CLK。

0, //rx_data_clock_delay,见下方描述

4, //rx_data_delay ,这些位影响DATA_CLK和 Rx data延迟。典型的延迟约为0.3 ns / LSB。Rx Frame 的延迟量与数据端口比特的延迟量相同。最小延迟设置为0x0,最大延迟设置为0xF。设置该寄存器,以使AD9361的数据符合BBP建立/保持规范。寄存器0x006

7, //tx_fb_clock_delay ,见下方描述

0, //tx_data_delay ,该寄存器的功能与寄存器0x006相同,但会影响FB_CLK,Tx_FRAME和 Tx Data位。Tx帧同步的延迟量与数据端口比特的延迟量相同。设置该寄存器,以使来自BBP的数据满足AD9361设建立/保持规范。

#ifdef ALTERA_PLATFORM

300, //lvds_bias_mV

#else

150, //lvds_bias_mV ,LVDS驱动器幅度控制。VOD = 75 mV to 450 mV

#endif

1, //lvds_rx_onchip_termination_enable,对所有数据路径比特、Tx_FRAME和FB_CLK使用LVDS Rx100片内匹配。CMOS模式下不能将该位置1

0, //rx1rx2_phase_inversion_en ,FMCOMMS5使用,Rx1和Rx2反相

0xFF, //lvds_invert1_control ,见下方描述

0x0F, //lvds_invert2_control ,通过设置这两个寄存器中的位,可以将任何LVDS对的相位从默认配置反转过来(见下表)。数据位的默认配置反相的。设置lvds-invert1-control = 0xFF和lvds-invert2-control = 0x0F来防止数据反相。时钟和帧信号在默认情况下不反相

六、GPO Control 、Tx Monitor Control 、GPIO definitions、MCS Sync、External LO clocks

6.1 GPO Control

0, //gpo0_inactive_state_high_enable

0, //gpo1_inactive_state_high_enable

0, //gpo2_inactive_state_high_enable

0, //gpo3_inactive_state_high_enable ,GPO[X]_inactive_state_high_enable,为0时,在Sleep, Wait, 和 Alert状态下为逻辑低;为1时,GPO在 Alert状态下为逻辑高。

0, //gpo0_slave_rx_enable

0, //gpo0_slave_tx_enable

0, //gpo1_slave_rx_enable

0, //gpo1_slave_tx_enable

0, //gpo2_slave_rx_enable

0, //gpo2_slave_tx_enable

0, //gpo3_slave_rx_enable ,为1时,当ENSM进入RX状态时,GPO引脚更改状态

0, //gpo3_slave_tx_enable, 为1时,当ENSM进入TX状态时,GPO引脚更改状态

0, //gpo0_rx_delay_us

0, //gpo0_tx_delay_us

0, //gpo1_rx_delay_us

0, //gpo1_tx_delay_us

0, //gpo2_rx_delay_us

0, //gpo2_tx_delay_us

0, //gpo3_rx_delay_us,设置从 Alert 状态转移到RX的延迟为GPO改变逻辑电平的时间。1us / LSB,范围从0到255 us。

0, //gpo3_tx_delay_us ,设置从 Alert 状态转移到TX的延迟为GPO改变逻辑电平的时间。1us / LSB,范围从0到255 us。

6.2 Tx Monitor Control

37000, //low_high_gain_threshold_mdB ,Tx Atten Threshold 37dB,TPM增益模式,低或高增益索引由 Tx Atten Threshold寄存器(寄存器0x078 [D7:D0])中的阈值决定。如果Tx Attenuation(寄存器0x073和寄存器0x074)等于或小于阈值,则使用低增益索引值,如果该值大于阈值,则在接收路径中使用高增益索引值。

0, //low_gain_dB ,Tx Mon Low Gain,接收低通滤波器增益GBBF由寄存器Tx Mon Low Gain 和 Tx Mon High Gain 设置(寄存器0x067 [D4:D0]和寄存器0x068 [D4:D0])。

24, //high_gain_dB ,Tx Mon High Gain,接收低通滤波器增益GBBF由寄存器Tx Mon Low Gain 和 Tx Mon High Gain 设置(寄存器0x067 [D4:D0]和寄存器0x068 [D4:D0])。

0, //tx_mon_track_en,为了最大化SNR, 0x067[D5] Tx Mon Track位可以设置为1,以最小化Tx monitor 信号路径中的DC偏移。

0, //one_shot_mode_en,必须是0,TPM Mode Enable,0x06E D[6]

511, //tx_mon_delay ,Tx Mon Delay Counter, ENSM进入发送状态后,如果0x06A[D7:D2]中的Tx Level Threshold= 0,Tx Mon Delay Counter启动。如果0x06A[D7:D2]非零,AD9361将I和Q样本的 6 MSBs与0x06A[D7:D2]进行比较。如果超过0x06A[D7:D2],Tx Mon Delay Counter 启动。到期后,AD9361测量发射RSSI。分辨率为 64 × ADC clocks/LSB

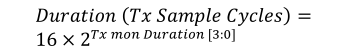

8192, //tx_mon_duration ,Tx Mon Duration,该寄存器根据下式指定发射RSSI测量的持续时间。

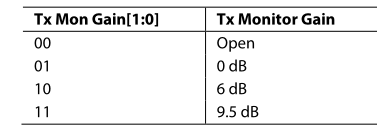

2, //tx1_mon_front_end_gain ,Tx Mon 1 Config ,Tx Mon 1 TIA Gain[1:0] ,TPM前端增益如下表

2, //tx2_mon_front_end_gain ,Tx Mon 2 Config ,Tx Mon 2 TIA Gain[1:0] ,TPM前端增益如下表

48, //tx1_mon_lo_cm ,48,Tx Mon 1 Config [D7:D2],必须6’b110000

48, //tx2_mon_lo_cm , 48,Tx Mon 2 Config [D7:D2],必须6’b110000

6.3 GPIO definitions

-1, //gpio_resetb ,复位引脚,输出,初始化时赋值为GPIO_RESET_PIN

6.4 MCS Sync

Multi Chip Sync (MCS) config,多片同步配置,FMCOMMS5需要

-1, //gpio_sync ,我使用FMCOMMS3,不使用该引脚(该值小于0即可),FMCOMMS5时配为GPIO_SYNC_PIN

-1, //gpio_cal_sw1 ,不使用该引脚(该值小于0即可),FMCOMMS5时配为GPIO_CAL_SW1_PIN

-1, //gpio_cal_sw2 ,不使用该引脚(该值小于0即可),FMCOMMS5时配为GPIO_CAL_SW2_PIN

6.5 External LO clocks

外部LO时钟,不使用外部LO时钟,配为NULL指针。

NULL, //(*ad9361_rfpll_ext_recalc_rate)()

NULL, //(*ad9361_rfpll_ext_round_rate)()

NULL //(*ad9361_rfpll_ext_set_rate)()

七、AD9361_RXFIRConfig rx_fir_config 、AD9361_TXFIRConfig tx_fir_config

滤波器详细介绍在AD9361 FIR 滤波器设计

AD9361_RXFIRConfig rx_fir_config = {

3, // rx

-6, // rx_gain

2, // rx_dec

{-12,-15,-22,-8,9,28,24,1,-28,-31,-2,42,57,21,-43,-76,-38,50,109,73,-44,-138,-111,36,177,169,-10,-210,-235,-26,247,321,86,-273,-419,-167,294,538,283,-297,-673,-434,280,832,641,-228,-1016,-916,130,1239,1302,48,-1522,-1873,-362,1926,2834,986,-2643,-4912,-2652,4728,14235,20875,20875,14235,4728,-2652,-4912,-2643,986,2834,1926,-362,-1873,-1522,48,1302,1239,130,-916,-1016,-228,641,832,280,-434,-673,-297,283,538,294,-167,-419,-273,86,321,247,-26,-235,-210,-10,169,177,36,-111,-138,-44,73,109,50,-38,-76,-43,21,57,42,-2,-31,-28,1,24,28,9,-8,-22,-15,-12}, // rx_coef[128]

128, // rx_coef_size

{983040000,491520000,245760000,122880000,61440000,30720000}, // rx_path_clks[6]

25820686 // rx_bandwidth

};

得到上面滤波器的配置结构体后, {983040000,491520000,245760000,122880000,61440000,30720000}, // rx_path_clks[6] 和 25820686 // rx_bandwidth 在后续ad9361_set_rx_fir_config函数配置滤波器时未用到

将上述得到的Rx/Tx路径时钟和带宽替换到AD9361_InitParam 参数的{983040000, 245760000, 122880000, 61440000, 30720000, 30720000},// rx_path_clock_frequencies[6]和18000000,//rf_rx_bandwidth_hz

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)