数字信号处理基础----信号的抽取和插值

1. 采样定理回顾 这一篇博客中将会介绍信号的 速率变换 和 抽取、插值 等操作。这些内容在FPGA进行数字处理的时候那是相当有用,解决了我在AD/DA和信号频率这些问题上的诸多疑问。其实这些问题,主要需要关注两个率,一个是信号的中心频率 Fb,一个是对信号的采样速率 Fs。1.1 低通采样定理 低通采样定理要求采样的最低频率需要大于两倍的信号的带宽。也即 Fs >= 2Fh。由卷积定理

1. 采样定理回顾

这一篇博客中将会介绍信号的 速率变换 和 抽取、插值 等操作。这些内容在FPGA进行数字处理的时候那是相当有用,解决了我在AD/DA和信号频率这些问题上的诸多疑问。其实这些问题,主要需要关注两个率,一个是信号的中心频率 Fb,一个是对信号的采样速率 Fs。

1.1 低通采样定理

低通采样定理要求采样的最低频率需要大于两倍的信号的带宽。也即 Fs >= 2Fh。由卷积定理可以知道,时域相乘等于频域卷积。于是可以看到以采样速率 Fs 进行低通采样过后,将基带信号的中心频率 Fb 搬到采样速率的位置。

1.2 对基带信号进行采样

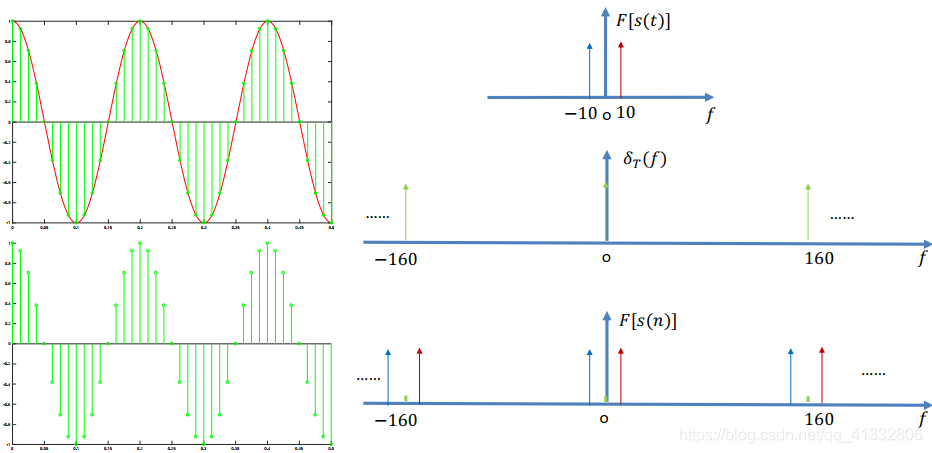

现在对基带信号进行采样,可以看到在频域中是将基带信号的频谱搬移到了以采样速率 Fs 为中心的频带上。

下面是基带信号的 I 路信号经过低通采样后的频域示意图,对于Q路信号同样适用

1.3 带通采样定理

对于一个带通信号,对其采样的时候,满足带通采样定理。

基于这个理论,就为我们用FPGA控制ADC在对信道上的信号进行采样的时候可以不用以一个很高的频率对原始信号进行采样,就能将原始信号无失真的恢复出来。

2. 信号的速率变换

2.1 提高采样速率

假设现在有一个基带信号和一个载波信号,载波信号是由160M对一个中心频率为70MHz进行采样得到的信号,基带信号是由20MHz采样得到信号,那么现在这两者的采样速率不匹配。如下图所示:

为了解决这个问题,可以对基带采样得到的基带信号进行插值,从而得到一个采样速率为160MHz的信号。

2.2 降低采样速率

FPGA以一定160MHz采样速率对外部ADC进行采样得到数据输入信号,对该信号以一个同样为160MHz采样速率的信号进行下变频,然后通过低通滤波器,得到基带信号,此时基带信号的采样速率是160MHz。

由于在FPGA处理基带信号的时候,需要占用存储资源的,因此,在基带信号还以160MHz采样的话,将会占用大量的存储资源。因此,根据带通采样定理,可以对信号进行抽取,从而降低信号的采样频率。

2. 信号的抽取

2.1 信号抽取的时域特征

对于一个离散的信号进行抽取的过程,可以看作是一个离散序列,对原始模拟信号以较低的采样速率进行采样得到的结果。

也就是说,对于一个采样速率较高的序列 S(n) ,可以看作是以较高采样频率,从模拟信号得到的序列。而对这个序列 S(n), 进行抽取得到的序列 **Sd2(n)**可以看作是对原始模拟信号以较低采样速率得到的一个序列。

2.2 信号抽取的频域特征

对一个信号以较高采样速率进行采样时,得到的频谱,相邻频带之间的距离较宽。

对一个模拟信号以较低采样率进行采样时,得到的频带之间的距离较近。

比较以较高采样速率和较低采样速率进行的信号的时域和频域特征不难看出,对一个信号进行抽取,就相当于降低了信号的采样速率。

2.3 对基带信号的抽取

对基带信号进行抽取时,一般会先让其通过一个低通滤波器,这样能够滤除信号中存在的噪声,于此同时,根据这个低通滤波器,还能够来设计抽取,防止抽取过多数据导致频谱的混叠。

3. 信号的插值

3.1 理想的插值

要了解信号的插值,首先还是需要来看一下对信号进行采样。分别对信号以较高采样速率采样和以一个较低的采样速率进行采样。

原始信号的时域和频域信息如下:

首先以一个 较低 的采样速率进行采样

然后以一个较高的采样速率进行采样。

可以比较两次采样的结果,第二次以较高速率对原始信号进行采样的时候,可以看作是在第一次较低采样速率的基础上插入一些数据。也就是说,在序列中插入值,相当于提高了采样速率。

3.2 对离散信号的插值

在实际中,对一个离散的信号进行插值时,是不知道原来的连续的信号长什么样子的,因此在插值的时候,并不知道要向原来的序列中,插入一些什么值。

正式由于不能知要插入的确切的值,因此考虑在序列中才入0值。

首先看没有插值时的时域和频域信息。可以看到在频域上各个平袋之间的间隔很小。

现在若考虑在采样点之间等间隔地插入0值。

可以看到其时域上非零值得点和原来没插值得时候没有变化,频谱上也和原来没有变化。但是由于我们插入了0值,也就是相当于在这个地方采样时采样到了零值。相对地就提高了采样地速率。所以可以看到在频谱和时域点没有发生变化的情况下,通过插入0值,就提高了采样的速率。

3.3 通过插值还原高采样率

下面再看一下以较低采样率进行采样,以较高采样率采样,和对较低采样率采样结果插值的对比。

可以看到,插值之后的频谱,和没有插值之前时没有变化的,唯一变化的就是采样率提高了。对比高采样率的频谱,可以发现,插值相较于高采样率的频谱多出了一些镜像。要是我们能够去除掉这些多出来的镜像,那么就可以通过插值得到一个高采样率的序列。

对采样过后的离散信号进行低通滤波

进行离散的低通滤波过后,就只会保留想要的信号,最终就相当于提高了采样的速率。

总结

最后还需要看一下一个完整的基带信号从调制到解调的过程当中的中心频率和速率变化的情况。

参考:

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)