高速逻辑电平LVDS、LVPECL、CML一站式详解

1.TTL、CMOS电平不适用于高速应用的原因:(1)电平幅度大,信号高低电平之间的转换时间长,不适用于传输频率达到200MHZ以上的信号;(2)输出信号为单端信号,传输路径易受到干扰,不利于长线传输;(3)功耗大,大家都知道TTL器件的静态功耗较大,即使静态功耗小的CMOS器件,由于电平摆幅宽,其动态功耗也偏大。所以以上所有的缺点就是高速电平的突出特点!!!!!2.高速逻辑电平详解:详解之前先整

1.TTL、CMOS电平不适用于高速应用的原因:

(1)电平幅度大,信号高低电平之间的转换时间长,不适用于传输频率达到200MHZ以上的信号;

(2)输出信号为单端信号,传输路径易受到干扰,不利于长线传输;

(3)功耗大,大家都知道TTL器件的静态功耗较大,即使静态功耗小的CMOS器件,由于电平摆幅宽,其动态功耗也偏大。

所以以上所有的缺点就是高速电平的突出特点!!!!!

2.高速逻辑电平详解:

详解之前先整体感知一下这三种电平的一些重要特性(图1)

2.1、LVDS

lvds指低压差分信号,是一种最高支持3.125Gbps的高速逻辑电平模式,一般适用于点到点的场合,例如:并行高速总线SPI 4.2的I/O接口电平;其逻辑电平是如何产生的呢?看下图:

下面以LVDS电平的发送端为例说明

划重点:LVDS采用的是电流驱动模式。

在发送端是由一个3.5mA的恒流源进行驱动,电流按照上图箭头的方向回流到地,在接收端由于100Ω终端电阻的存在形成350mV的电压摆幅,接收端被识别为逻辑”1“,反之当电流从地流回至恒流源时,便产生了-350mV的摆幅,被识别为逻辑”0“;对于单个端口而言。负载功耗为1.2mW(350mV*3.5mA=1.2mW);

讨论:

(1)端接电阻100Ω的作用是实现电流到电压的转换;以及差分信号的阻抗匹配,防止信号发生发射;

(2)LVDS接收端对输入的差分对信号摆幅要求是100mV;

(3)信号沿变化速率较低。上升沿爬升时间约为0.5ns,因此信号沿变化率为0.7V/ns,其变化率已经很慢了,这样EMI值就越小,因此LVDS电平有助于减小EMI。

(4)空闲输入引脚悬空防止噪声引入,空闲输出管脚应悬空,以减小功耗。

(5)LVDS电平不适合传输大于2Gbps的数据速率,(好像跟他特性里面的最高传输速率互相矛盾)

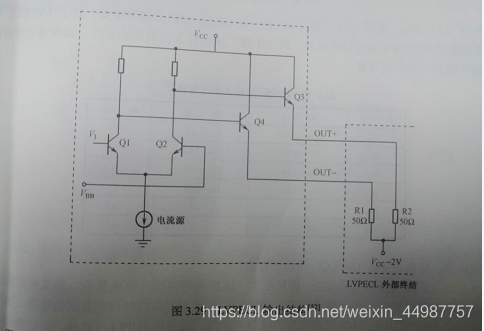

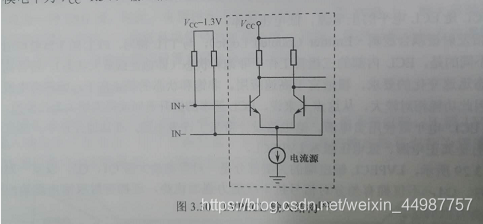

2.2 LVPECL

LVPECL是ECL电平的正电平、低电压版本;

ECL指的是发射极耦合逻辑,与TTL主体相同也是由三极管构成,不同的是ECL内部的三极管工作于非饱和状态,满足逻辑状态快速变化的需求;ECL常采用负电源供电,而在实际高速设计的时候常采用正电源;

结构:Q1、Q2组成差动放大电路,Q3、Q4发射极输出;

特点:差分对抗干扰能力强,射极输出电阻小驱动能力强;

VCC取值为3.3V或2.5V,VBB为内部参考电平;属于电流驱动型

当V1电平高于VBB时,Q1导通Q2截止,在输出端Q3导通Q4截止,输出逻辑“1”;

当V1电平低于VBB时,Q1截止Q2导通,在输出端Q3截止Q4导通,输出逻辑“0”;

任意时间段由于Q1或Q2必导通,这就导致LVPECL的功耗大的原因

LVPECL输入输出电平尚未在国际上形成标准;

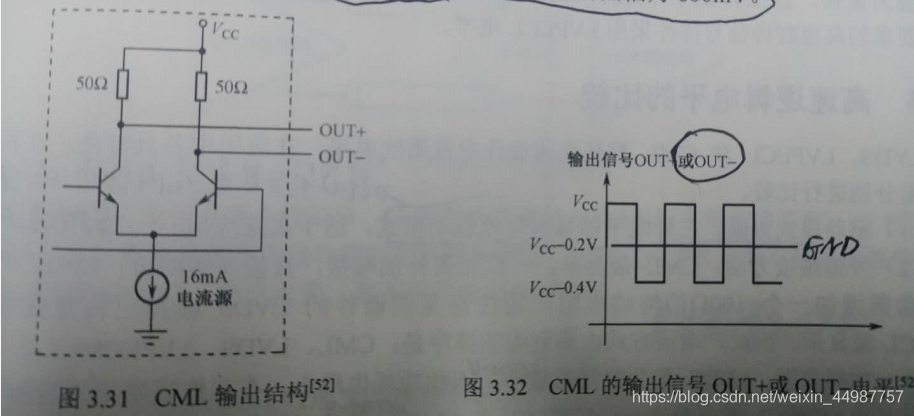

2.3 CML

CML(current Mode Logic)指电流模式逻辑;

常应用于:XAUI(10Gbps以太网连接单元接口)、10G XFI接口(10Gbps以太网串行接口)。

输出结构:CML的电源VCC一般取1.2V,输出端由一对三极管组成差动放大电路、两个三极管的发射极与GND之间串一个16mA的电流源,三极管的集电极与VCC之间串接50Ω电阻。

CML的输出信号OUT+ 或OUT-其共模电平为VCC-0.2V,摆幅为400mV,因此差分对OUT+与OUT-的摆幅为800mV

CML电平输入输出电平,国际标准组织尚无定论不同厂商的器件参数可能不一致;CML支持的数据速率高达10Gbps,极高速信号往往采用匹配方式简单的CML电平;

3. 三种逻辑电平的比较

①从驱动模式来讲:三者都输入电流驱动,适用于高速应用;

②从耦合方式来讲:三种电平都支持直接耦合或AC耦合;

③从功耗上来讲:LVDS的摆幅只有350mV,因此其功耗最小,CML与LVPECL摆幅较大,基于结构上的差异CML略低于LVPECL;

④从工作速率将:CML与LVPECL内部三极管工作在非饱和状态,逻辑翻转快支持极高速率,LVDS无法支持极高速率;

⑤从端接模式来讲:CML输出直接可以互联,LVDS需要在输入端接100欧电阻,LVPECL外围电路最复杂;

⑥从标准规范来讲:只有 LVDS电平在国际上有统一的标准。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)