简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

USB传输ADC数据之FT232H驱动设计

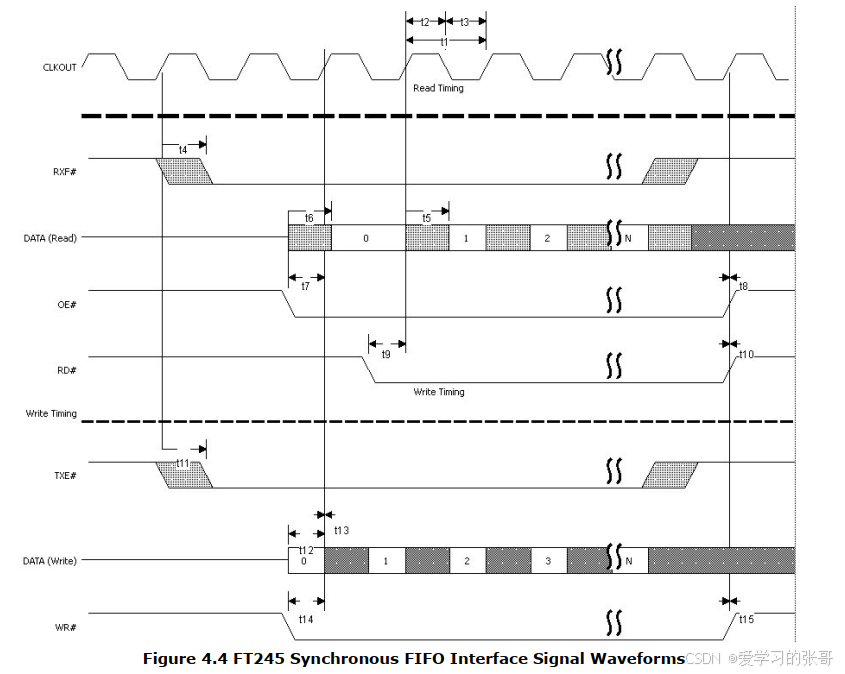

首先FT232H拉低RXF#信号,表示FT232H中的FIFO有数据等待读出,当FPGA接收到这个信号时,将OE#信号拉低,使能FT232H的输出,观察时序可知,在OE#拉低的t6时间后,总线开始输出有效数据,这时拉低RD#,即可读取有效数据,注意手册中明确指出OE#拉低压迫至少比RD#拉低提早一个时钟周期,故在程序设计中,将RD#拉低晚于OE#一个时钟周期即可。若此时FPGA侧的FIFO同样有数

到底了