简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

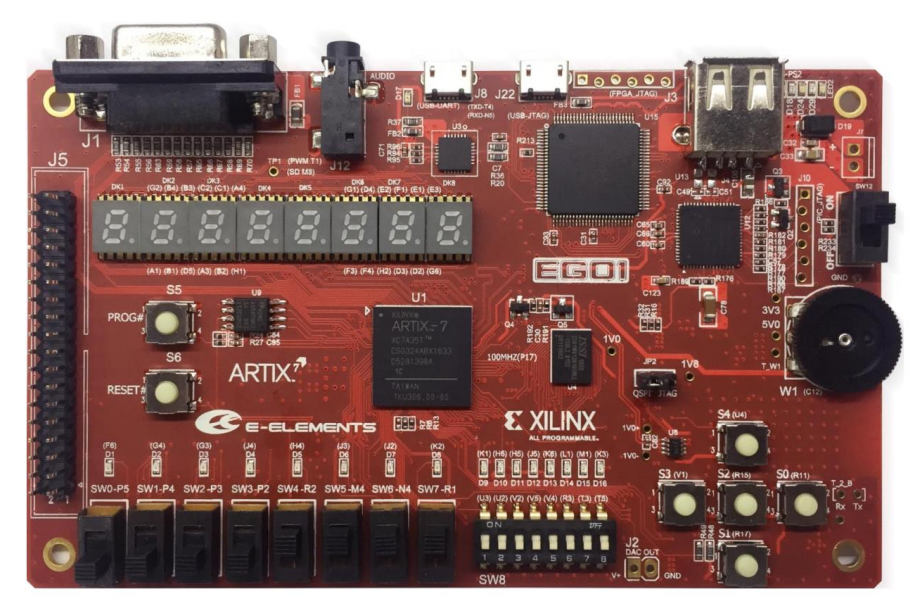

1.键盘按键作为琴键,由于按键有限,根据你要演奏的曲目,设计每个按键代表的音符2.用数码管显示当前按下的音符,自定义显示方式。3.蜂鸣器作为输出,参考音符频率对照表4.选择一个拔码开关作为电子琴的开关,信号有效时才产生音乐输出,无效时不输出音乐。5.能自动播放一首乐曲。6.LED灯点亮情况能根据乐曲变化而变化7.具有暂停和继续播放功能。8.具有倍速播放功能。9.具有循环播放功能

74LS48芯片功能实现74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路系统的显示中设计代码实现74LS48芯片功能,并进行仿真

代码功能:60进制递减计数器使用按键控制倒计数,按一次减1,减到0后再回到59数码管显示计数值

代码功能:60秒倒计时器1、按下复位按键后开始60秒倒计时,每秒递减1,减到0后保持。2、使用数码管显示倒计时

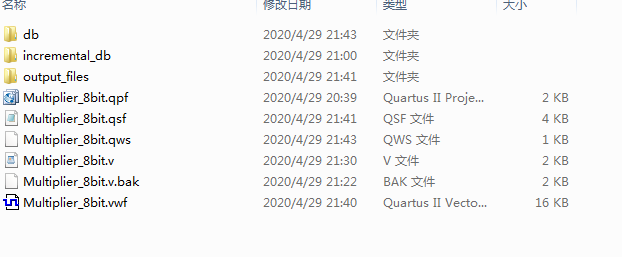

代码功能:使用booth、移位、并行算法实现乘法器1、使用三种方法设计8位乘法器2、使用booth算法实现3、使用移位相加算法实现4、使用并行相乘算法实现

代码功能:设计并制作一个数字电子钟,要求如下:具有“时”、“分”、“秒”数字显示具有“时分”校时功能。(1)编写程序并进行仿真验证(2)下载到FPGA板上,并且在数码管上显示时间(4位数码管,显示分和秒,用4个LED表示小时)(3)扩展功能自行发挥(可加分)

代码功能:出租车计费器1、起步价5元,3公里内起步价2、3公里后每公里2.1元3、停车等待时,0.6元每十分钟4、计费方式可以通过代码参数快捷修改

代码功能:象棋游戏倒计时器设计1、具有2个选手控制按键,选手1,按下按键选手2的时间开始倒计时2、选手2,按下控制按键选手1的时间开始倒计时3、若对方倒计时结束,则赢得比赛4、设置获胜指示灯,有超时提醒5、数码管显示2个选手倒计时分钟、秒钟

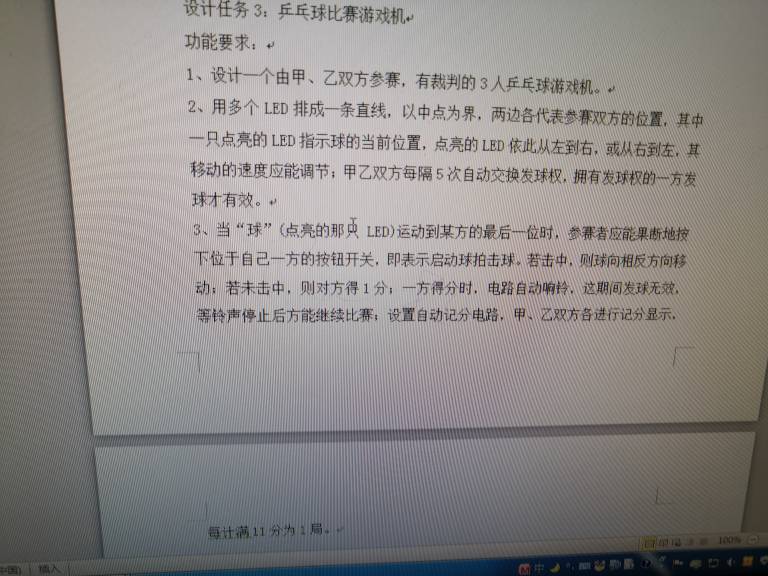

1、设计一个由甲、乙双方参赛,有裁判的3人乒乓球游戏机。2、用多个LED排成一条直线,以中点为界,两边各代表参赛双方的位置,其中一只点亮的LED指示球的当前位置,点亮的LED依此从左到右,或从右到左,其移动的速度应能调节;甲乙双方每隔5次自动交换发球权,拥有发球权的一方发球才有效。3、当“球”(点亮的那LED)运动到某方的最后一位时,参赛者应能果断地按下位于自己一方的按钮开关,即表示启动球拍击球。

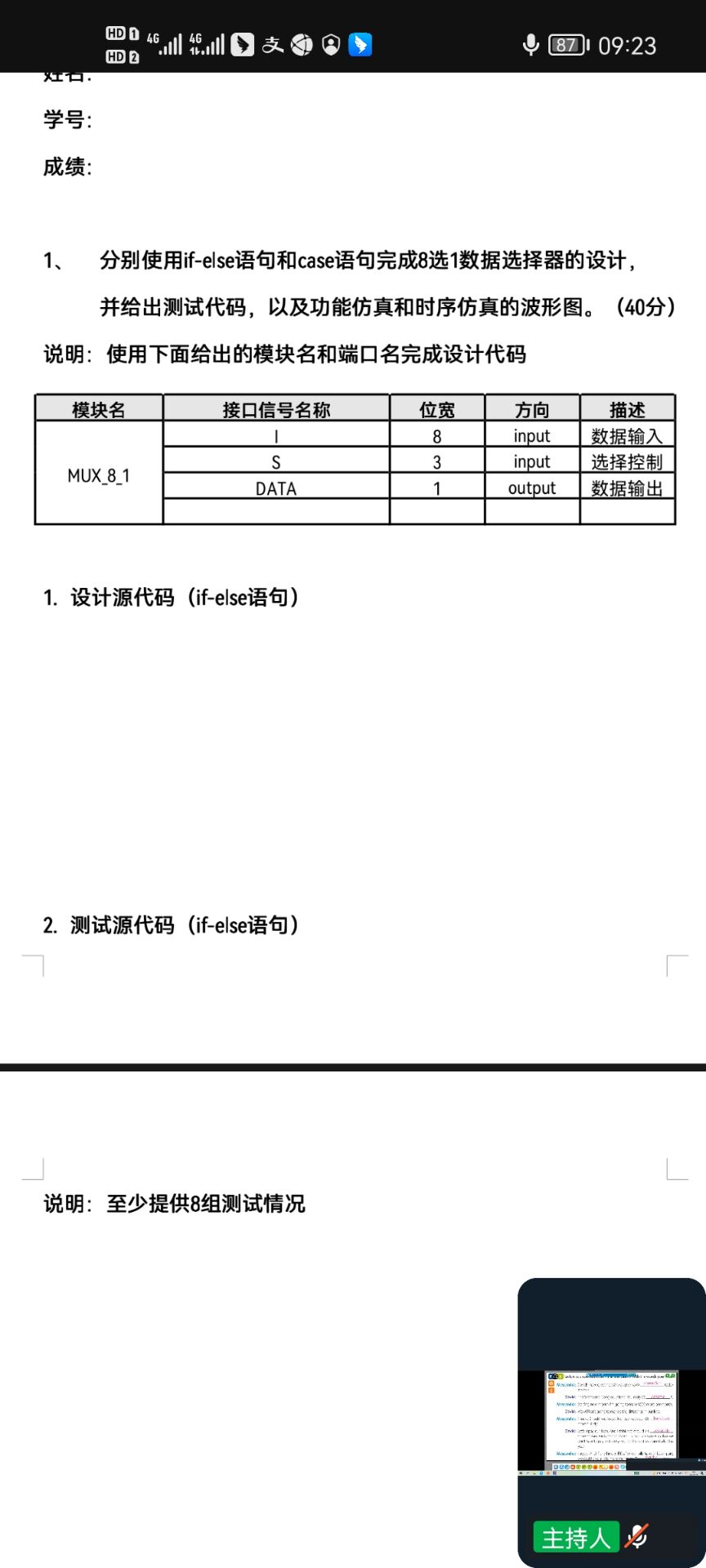

分别使用f-else语句和case语句完成8选1数据选择器的设计并给出测试代码,以及功能仿真和时序仿真的波形图。说明:使用下面给出的模块名和端口名完成设计代码