简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

通过本文您可能会了解:1、学会如何使用三段式状态机来实现DHT11数字温湿度传感器的驱动代码;2、加深对三段式状态机的理解与应用。

【数字IC/FPGA】书籍推荐(0)----《Verilog 传奇--从电路出发的HDL代码设计》

什么是组合逻辑环路?它到底有什么危害使得人人谈之色变?

通过本文您可能会了解:1、学会如何使用三段式状态机来实现DHT11数字温湿度传感器的驱动代码;2、加深对三段式状态机的理解与应用。

【FPGA】线性反馈移位寄存器(LFSR)的Verilog实现

给大家推荐一个非常好的练习Verilog的网站,有一两百道题,基本涵盖了Verilog语法的方方面面,是一个非常好的入门学习网站。网站连接:HDLBits

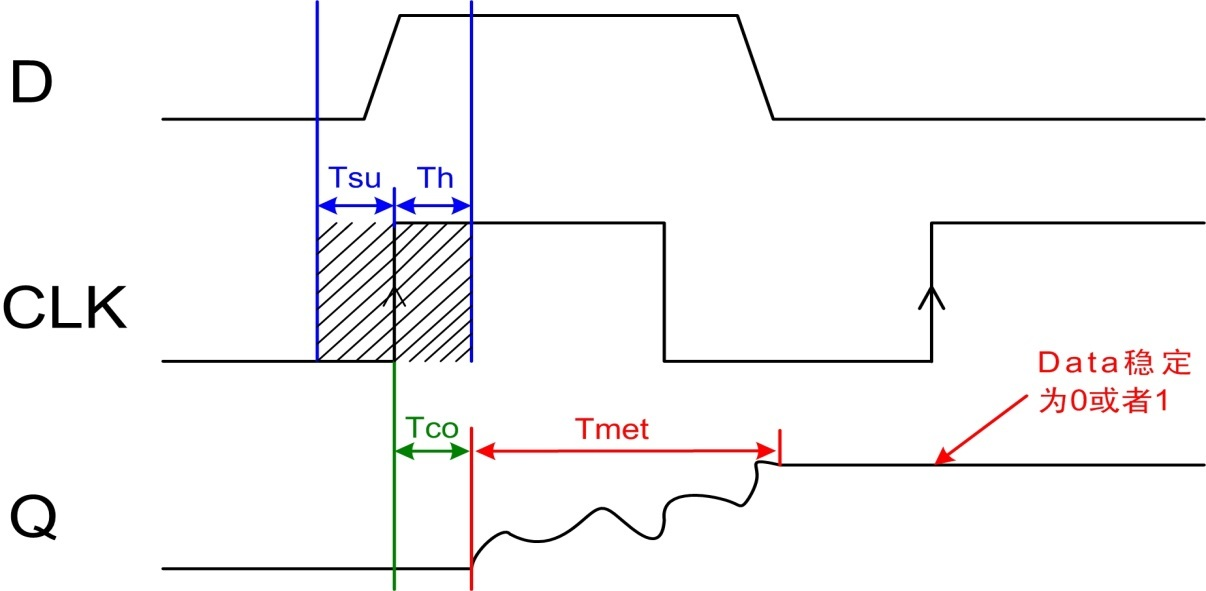

1、前言可能很多FPGA初学者在刚开始学习FPGA设计的时候(当然也包括我自己),经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。2、触发器的建立时间和保持时间时序电路的基础是触发器(FF、Flip-Flop),触发器正常工作需要满足建立时间和保持时间的时序要求。建立时间(Tsu:set

Xilinx 7系列FPGA之Artix-7产品简介

转载自:集成电路芯片半导体中英文对照术语词汇表英语中文 1-9 10 gigabit10 Gb1st Nyquist zone第一奈奎斯特区域3D full‑wave electromagnetic solver3D 全波电磁解算器3-state三态4th generation segmented routing第四代分层布线技术5G commercialization5G 商用7 series

给大家推荐一个非常好的练习Verilog的网站,有一两百道题,基本涵盖了Verilog语法的方方面面,是一个非常好的入门学习网站。网站连接:HDLBits