简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

VIVADO 仿真报错 ERROR: [VRFC 10-2063] Module <blk_mem_gen_2_ban> not found while processing module insta

其他人的工程 直接用高版本vivado打开后 仿真报错。尝试Reset Output Products。

VIVADO 仿真 信号异常高阻抗

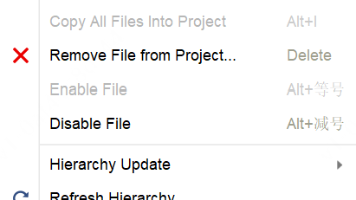

生成仿真文件后 vivado 会自动将仿真顶层文件set as top,但此时仿真会出现信号高阻状态(如时钟、复位等信号)。此时需要重新将该仿真顶层文件set as top(先将另一文件set as top,再将仿真顶层文件set as top)可解决该问题。

COE文件格式及地址对应方式 RAM IP核设置COE文件时报错 RAM/ROM数值初始化设置

报错信息a.coe' for IP 'blk_mem_gen_0'. Invalid COE File- Invalid Radix found:0. Radix can be only 2,8,10 or 16。按照该图COE文件设置方式,即将RAM地址0-15部分内容进行初始化设置,如地址内不止4bit,则从低位开始设置,如图,即将地址0内的第四位设置为4‘b1111。MEMORY_INITI

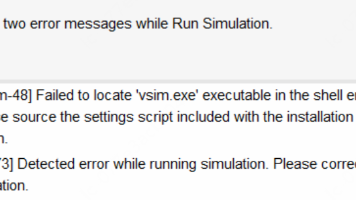

VIVADO 仿真报错 [USF-ModelSim-48] Failed to locate ‘vsim.exe‘ executable in the shell environment ‘PATH‘

在不需要使用ModelSim联仿的时候改为Vivado Simulator。

到底了