简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

基于Quartus件完成1位全加器的设计及4位全加器的设计

基于Quartus件完成1位全加器的设计及4位全加器的设计

FPGA:uart原理+tx发送模块+rx接收模块

它在发送数据时将并行数据转换为串行的数据来传输,在接收数据时将接收到的串行数据转换成并行数据。UART串口通信需要两根信号线来实现,一根用于发送,另一个用于接收。串口通信速率用波特率表示,它表示每秒传输二进制数据的位数,单位是bit/s(位/秒),简称bps;tx发送模块:共四个状态,IDLE状态,START状态,DATA状态,FINISH状态。不带时钟同步信号的数据传输,发送方和接收方使用各自的

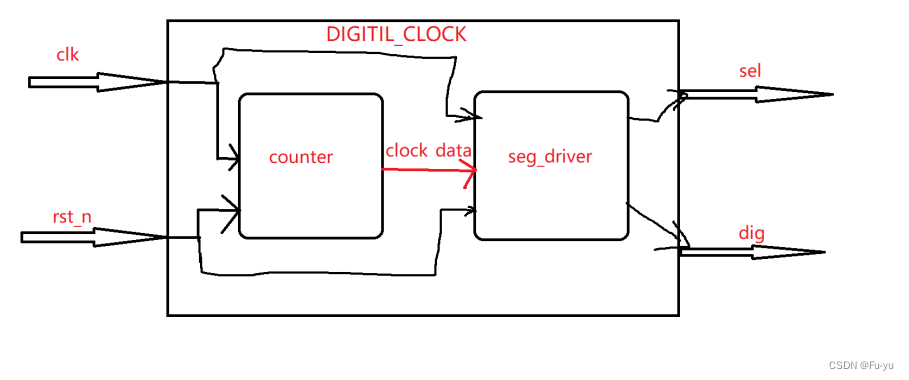

FPGA项目设计:数字时钟

设计一个数字时钟,数码管前两位显示小时,数码管中间两位显示分钟,数码管后面两位显示秒。

到底了