简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

z = scroll,t = top,b = bottom,z = center(中间的字母):Z 命令的精髓在于让你控制"看什么"和"怎么看",掌握这些命令能显著提高代码阅读和编辑的效率。:h = left,l = right,大写表示更大的移动距离。这些命令让你能够精确控制文本的显示方式,提高编辑效率。:重画版本在终端显示有问题时特别有用。:数字越大,折叠层次越深。

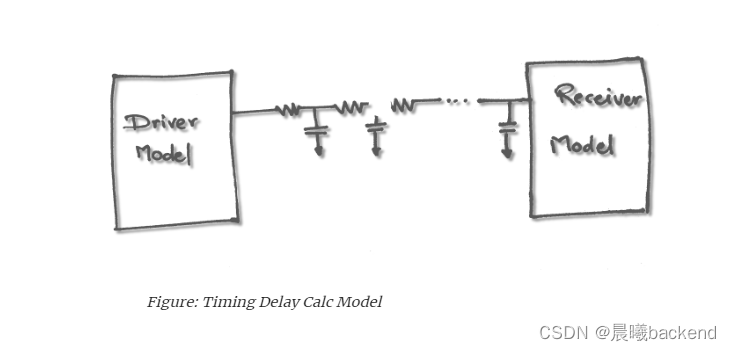

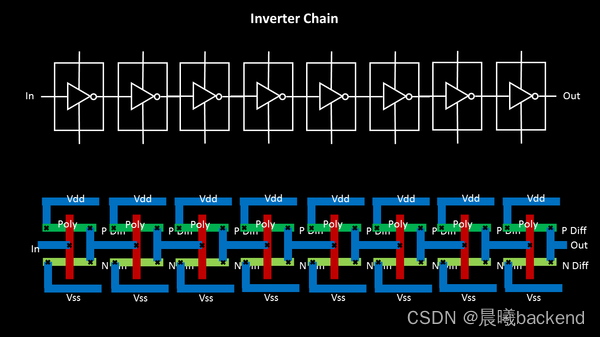

的模型就极为重要,尤其半定制,需要把一个std cell看成block box,只考虑其input/output pin。(由于密勒效应因此不准确) for the entire transition with no sensitivity.Cell model都需要对receiver/driver分别建立模型,得到的模型结果越接近真实值,则精确度更高。

芯片的delay由两部分影响因素构成PR工具读入文件MMMC:constrain mode(sdc) + library set pvt corner + rc tech file(rc_corner)

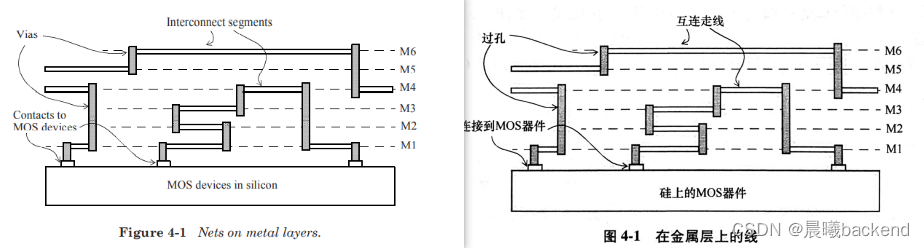

本章概述了各种处理和表示互连寄生参数的技术,这些技术用来验证设计的时序。在数字设计中,一条线段(Wire)把标准单元或块(Block)的引脚连接起来,被称为线(Net)。一条线(Net)通常只有一个驱动,但是它可以驱动多个扇出单元或块(Block)。在之后,这条线(Net)可能经过芯片上的多层金属。不同的金属层可能有不同的电阻和电容值。对于等效电气表示,一条线通常分解为不同的,每个片段用等效寄生参

本章概述了和后的,以单元为基础的设计是如何进行延迟计算的。前几章重点介绍了和库函数。单元和互连线的建模技术被用来得到设计的时序。

数字后端设计库(.v网表与sdc file)、逻辑综合、IO接口约、sdc、synopsys design constrains

DC LAB 3 flow

数字IC软件介绍及IP

本章概述了和后的,以单元为基础的设计是如何进行延迟计算的。前几章重点介绍了和库函数。单元和互连线的建模技术被用来得到设计的时序。

设置timing derate 的timing report 如下所示,在该例中,Total mean/sigma derate, Delay Mean, Delay sigma 的计算分别如下所示,其他的计算跟不带set_timing_derate 的一致。示例中,buff_4_2/Z 的arrival delay 值为0.55383, 是因为工具在计算时是按照浮点数位宽计算的,最后显示在时序报