简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

书接上文,本文测试禁用报告和抑制信息能否加快编译速度?先说结论:1. 禁用报告能略微提升Vivado编译速度,但副作用很大(看不到资源利用率、时序等报告了),不推荐;2. 抑制信息不能提升Vivado编译速度。具体测试详见正文。

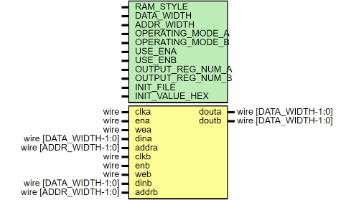

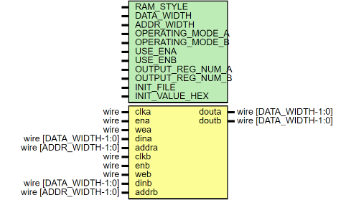

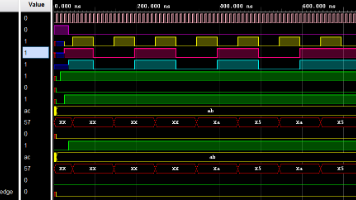

摘要:本文对自编RAM与Vivado RAM IP的功能特性进行了对比测试,重点分析了两者在初始化、使能控制、输出寄存器和操作模式等方面的差异。测试主要针对TDPRAM实现,在300MHz高频条件下验证了模块性能,并采用冲突抑制机制避免读写冲突(包括写-写冲突和读-写冲突)对测试结果的影响。文章通过随机信号测试方法,对比了两种RAM实现的关键功能表现,为FPGA存储器设计提供了实践参考。

FPGA内存模块自研实现方案解析 摘要:本文介绍了FPGA开发中自研RAM/ROM模块的必要性与实现方案。与商业IP核相比,自研模块具有更好的代码移植性,适用于基础功能场景。文章详细阐述了模块支持的三种RAM类型(单端口、简单双端口、真双端口)和两种ROM类型,实现了写优先/读优先/无变化三种操作模式,并兼容COE文件初始化功能。模块设计参考了Vivado BRAM IP的接口标准,但暂未实现字节

本系列文章将设置不同条件对Vivado编译速度进行详细测试,评估哪些手段能提高Vivado的编译速度。

书接上文,本文测试Vivado的两种非GUI模式即Tcl-Project Mode和Tcl-Non-Project Mode能否提高编译速度。先说结论,测试结果表明:两种模式均无法提升编译速度,甚至更慢。

本文基于Verilog设计的SPI主从机模块,通过回环仿真测试验证其功能正确性。实验使用Vivado工具,在不同时钟频率(100/120MHz)下设置多种SPI模式(0-3)、数据位宽(8/10/12/16)和时序参数进行测试。通过分析波形图,验证了SCLK频率、通信模式、数据位宽等参数符合设定,且主从机数据收发一致。仿真结果表明,SPI主从机模块在多种配置下均能正常工作,满足设计要求。测试代码展

本文以 MB、ZYNQU、VCT 三类含 Block Design 的工程为测试对象,基于 Vivado 2024.2 版本,对比 OOC per IP 与 Global 两种模式在工程第一次编译情况下的耗时。

本文聚焦问题——不同综合与实现策略是否影响编译速度及影响程度。以Vivado 2024.2为环境,选取CPU、MB、ZYNQU、VCT工程测试,对比默认与编译时间优化策略的耗时,剖析策略作用,为Vivado编译提速提供参考。

Vivado 编译速度是 FPGA 开发的关键瓶颈,此前已探讨线程、内存等提速方案,本次聚焦核心问题:Win11 与 Ubuntu(Linux)谁更能提升编译效率?尤其在虚拟机环境下。实验统一硬件(AMD 9950X、64G 内存)、Vivado 2024.2、32 线程,测试 4 类不同复杂度工程,用数据验证系统差异 —— 既看简单工程表现,更关注复杂工程是否因 Ubuntu 实现显著提速,为开

现代电脑都支持多线程,目前个人电脑基本都是16线程起步,一个优秀的软件应该有调用多线程加快运行速度的能力,那Vivado满足这个优秀的条件吗?这里的job就是线程的意思,因为你会发现,jobs的最大值总是和你电脑CPU的最大线程数一致。无论最大线程怎么设置,在编译时,都会弹出一个对话框,让我们选择用本机的多少jobs来进行编译,如下图所示。Vivado最多能利用的线程数应该是16,可以发现使用线程