简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

cortex_m3_stm32嵌入式学习笔记(十五):待机唤醒实验(WK_UP外部中断)https://blog.csdn.net/qq_16255321/article/details/43086403很多单片机都有低功耗模式, STM32 也不例外。在系统或电源复位以后,微控制器处于运行状态。运行状态下的 HCLK 为 CPU 提供时钟,内核执行程序代码。当 CPU 不需继续运行时,可以利用多

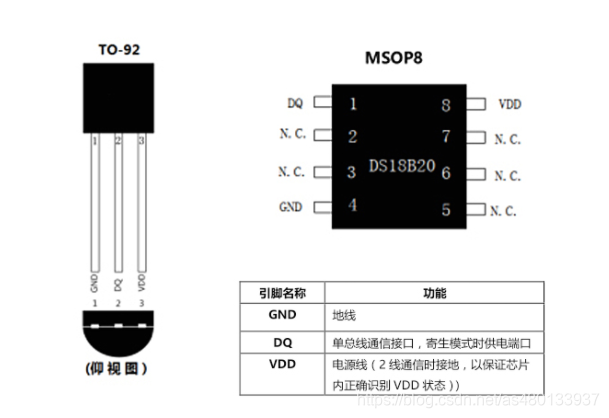

【常用传感器】DS18B20温度传感器原理详解及例程代码_Z小旋的博客-CSDN博客_ds18b20温度传感器传感器引脚及原理图DS18B20传感器的引脚及封装图如下:DS18B20一共有三个引脚,分别是:GND:电源地线DQ:数字信号输入/输出端。VDD:外接供电电源输入端。单个DS18B20接线方式: VDD接到电源,DQ接单片机引脚,同时外加上拉电阻,GND接地注意这个上拉电阻是必须的,就是

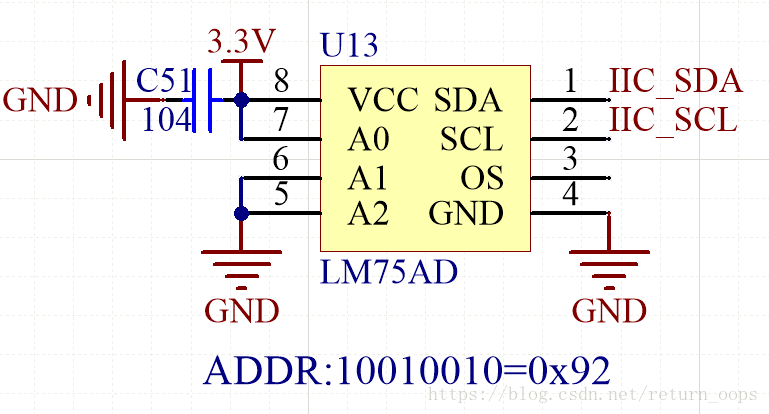

#include "LM75AD.h"#include "IIC.h"///*0x00Temperature Register0x01Configuration register器件模式 写00普通模式(100ms更新一次温度值) 写01为ShutDown模式0x02Hysteresis register0x03Over_temperature shutdown registerTemp Regi

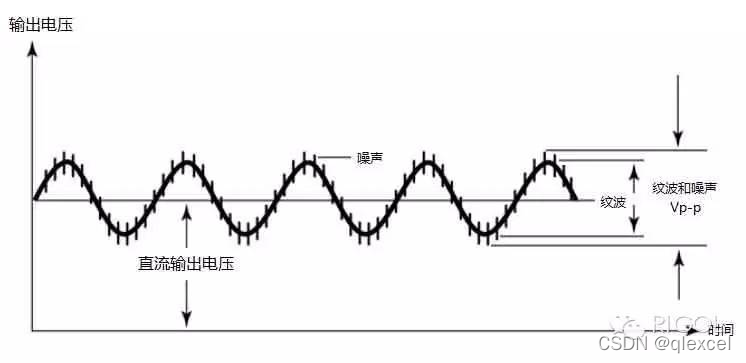

电源纹波和噪声的定义PARD(periodicand random deviation):1、 电源纹波(Power Ripple):直流电压/电流中,叠加在直流稳定量上的交流分量,用电压和电流的均方根值(mVrms/mArms)或峰峰值(mVpp/mApp)来表示。2、 电源噪声(Power Noise):开关管高速通断,使电压/电流急速变化而引起的高频噪声。纹波和噪声是直流电平上的杂波信号,包

STM32嵌入式:几种烧录方式目录ISPIAPSW/JTAGISP这种和下一种烧录方式就是我们常说的BootLoader,通过一段引导代码来将我们要烧录的程序通过串口烧写进入单片机的Flash。但是与IAP烧录方式不同的是,这段引导代码是ST公司在芯片出厂前就固化在内部的,我们是需要按照给出的文档说明操作就行了。ISP支持的下载接口有:方式协议说明软件链接备注USARTAN3155据说官方的软件很

开发板免费申请 嵌入式开发板测评-电子工程世界http://bbs.eeworld.com.cn/elecplay.html

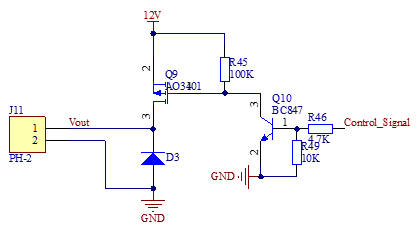

本次项目上需要实现的功能是利用AO3401 PMOS设计一个开关电路,实现一款设备的开关控制。被控设备12V供电,供电电流小于3A即可。且为了提高响应速度,使流过该设备的电流尽可能的大。该设备内阻大约为6ohm。AO3401产品参数其他参数芯片内部等效电路引脚顺序设计电路设计并调试好的电路如下图所示,由于供电电压和驱动电压均可以使用12V,所以采用了如下较为简单的方案。如图所示,Q9 AO3401